Verification method combining scoreboard and assertion check

A verification method and scoreboard technology, applied in the direction of instruments, CAD circuit design, computer-aided design, etc., can solve the problems of reducing simulation performance, lack of correlation, prolonging simulation time, etc., to improve quality, improve work efficiency, and realize fast The effect of positioning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings to further illustrate the present invention.

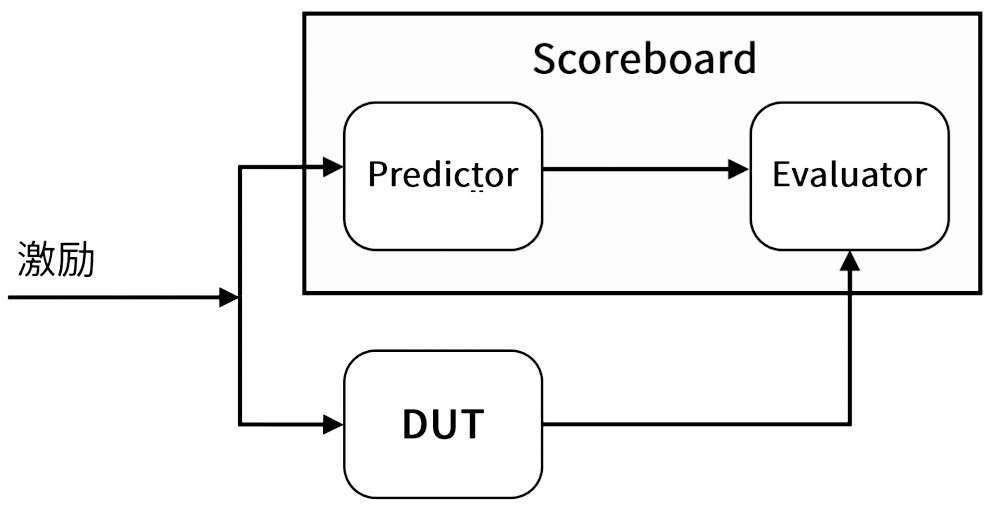

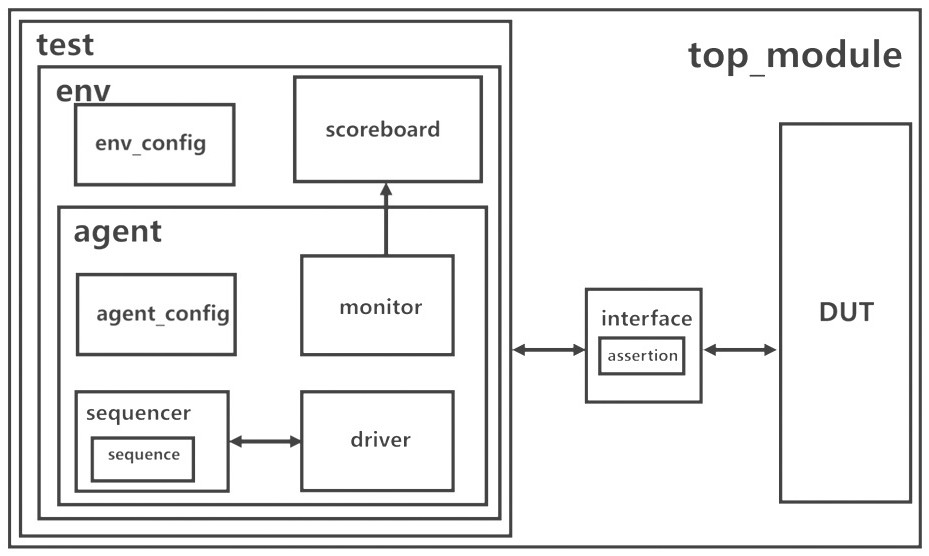

[0047] First, combine Figures 3~7 The verification method combining the scoreboard and the assertion check according to the embodiment of the present invention is described, which is used for verification of chips, and has a wide range of application scenarios.

[0048] like Figures 3~7 As shown, the verification method combining the scoreboard and the assertion check according to the embodiment of the present invention has the following steps:

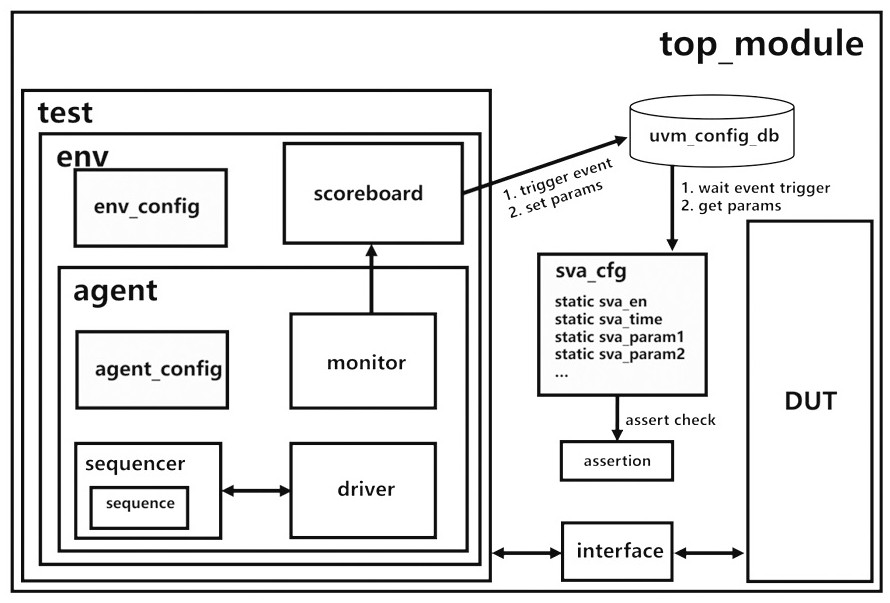

[0049] In S1, as in Figure 4 Shown: Declare the uvm_event event in the scoreboard to control the asserted enable switch variable.

[0050] In S2, as in Figure 4 Shown: The uvm_event event is instantiated in the build_phase in the phase mechanism of UVM, and passed into the configuration database of UVM. In this embodiment, the scope space passed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More