Layout construction method

A construction method and layout technology, applied in the direction of instrumentation, calculation, electrical digital data processing, etc., can solve problems such as function failure, timing information, power consumption information deviation, and inaccurate comprehensive results, so as to improve accuracy and accuracy rate Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example ;

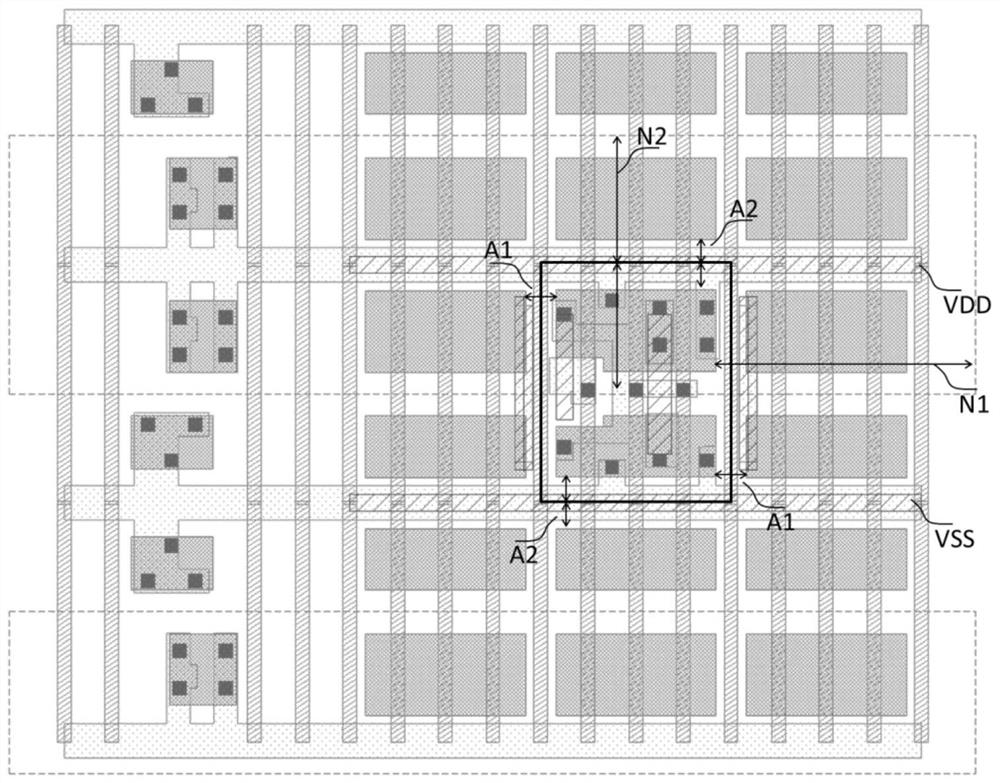

[0036] The present invention provides a layout construction method, which is used for simulating the use environment of a standard cell library unit, comprising the following steps:

[0037] S1) determine the substrate potential, the standard cell library unit connects the substrate with the set potential power supply through the substrate connection unit;

[0038] S2) simulate the active area environment, and increase the active area without electrical characteristics in the standard cell library unit up, down, left and right;

[0039] S3) simulate the injection layer environment, and the shown injection layer width is larger than the injection layer of the standard cell library unit itself;

[0040] S4) simulating the grid environment, arranging invalid grids in the upper, lower, left, and right directions of the effective grid of the standard cell library unit, simulating the environment after the upper, lower, left and right splicing of the cell library;

[0041] S5) simu...

no. 2 example ;

[0045] The present invention provides a layout construction method, which is used for simulating the use environment of a standard cell library unit, comprising the following steps:

[0046] S1) determine the substrate potential, the standard cell library unit is connected to the unit through the substrate, the substrate connecting unit is located on both sides of the standard cell library unit, and its P well is connected to the N well, and the substrate is connected to the set potential power supply connected;

[0047] S2) Simulate the active area environment, and add active areas with no electrical characteristics on the upper, lower, left, and right sides of the standard cell library unit; The minimum design rules provided by the tape-out manufacturer;

[0048] S3) simulate the injection layer environment, the width of the injection layer shown is larger than the injection layer of the standard cell library unit itself, and the width of the injection layer on the left and r...

no. 3 example ;

[0053] The present invention provides a layout construction method, which is used for simulating the use environment of a standard cell library unit, comprising the following steps:

[0054] S1) determine the substrate potential, the standard cell library unit is connected to the unit through the substrate, the substrate connecting unit is located on both sides of the standard cell library unit, and its P well is connected to the N well, and the substrate is connected to the set potential power supply connected;

[0055] S2) Simulate the active area environment, and add active areas with no electrical characteristics on the upper, lower, left, and right sides of the standard cell library unit; According to the minimum design rule provided by the tape-out manufacturer, the distance between the non-electrical active area on the upper and lower sides of the standard cell library unit and the active area of the standard cell library unit is the distance between the active areas ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More