SMT solver fault positioning method based on search

A fault location and solver technology, applied in genetic models, program code conversion, code compilation, etc., can solve problems such as no control flow, time-consuming, adaptation difficulties, etc., to facilitate debugging work and improve quality.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The specific embodiments of the present invention will be further described below with reference to the accompanying drawings and technical solutions.

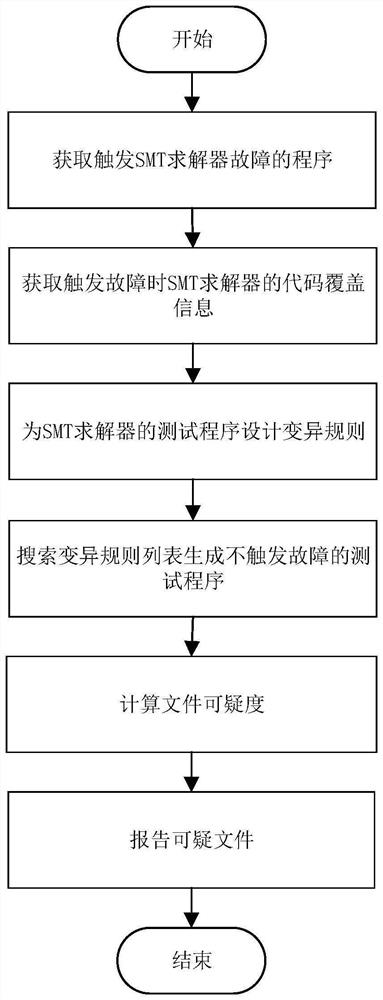

[0046] The workflow of the present invention is as follows figure 1 As shown, the method of the present invention is deployed on a computer equipped with a Linux operating system, and the specific configuration of the computer is shown in Table 1. Choose to use Z3 and CVC5 solvers according to the experimental requirements, and install the corresponding software according to the steps.

[0047] Table 1 Computer configuration information table

[0048] Processor model Memory operating system Intel Core i5-4570 2T Ubuntu20.04.2LTS

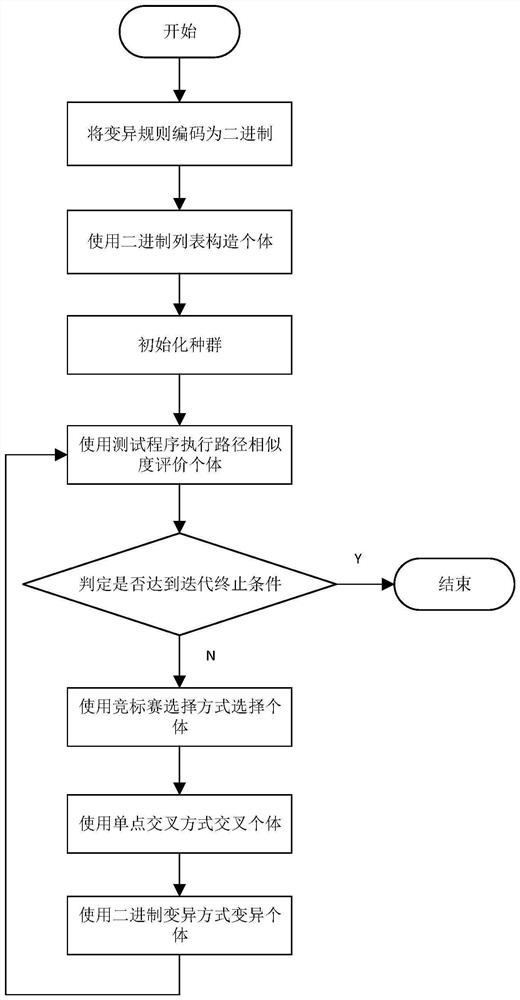

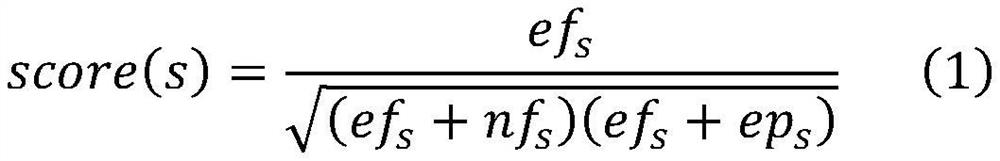

[0049] like figure 1 As shown, the SMT solver fault is located as follows. In SMT solver fault location, in addition to the deterministic factors specified in the compilation environment, other factors, such as population size, iteration termination conditions, cr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More