Method for acquiring file status by using Verilog hardware description language

A hardware description language and file technology, applied in the direction of program control design, instruments, electrical digital data processing, etc., can solve the problems of inconvenient testing, poor test code portability, inconvenient user design and testing, etc., to achieve enhanced operation functions, Simple code writing and good code portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

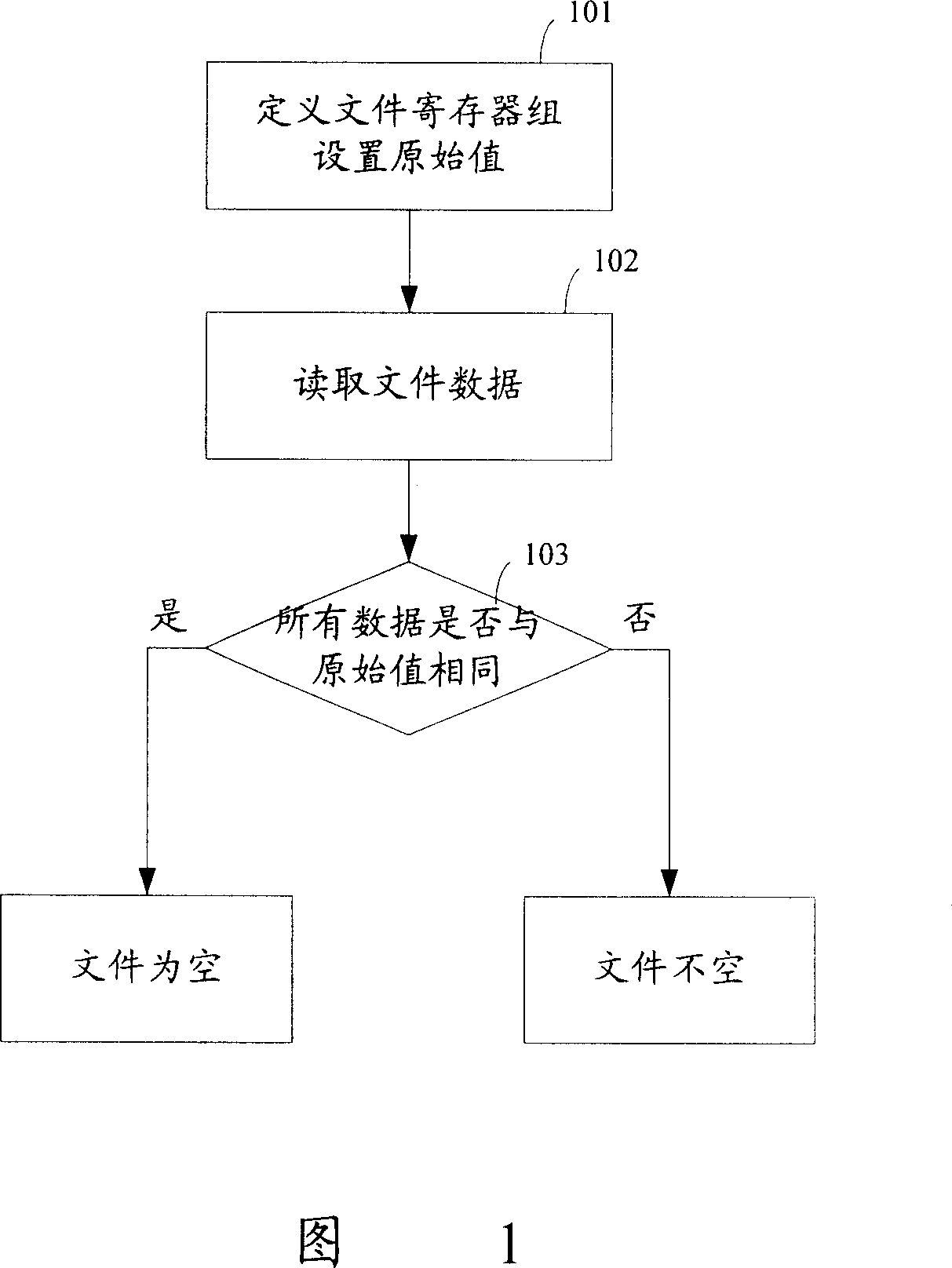

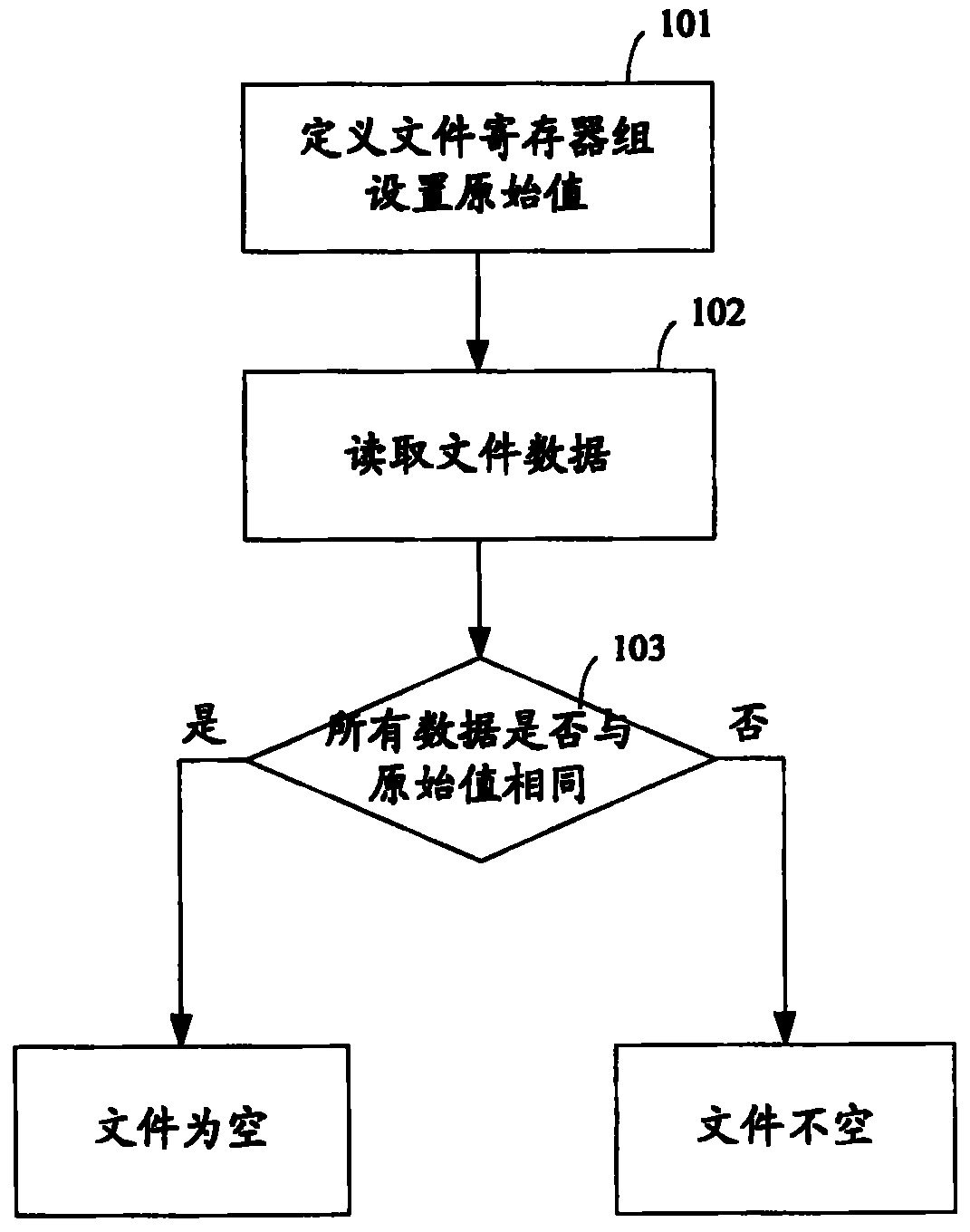

[0025] In the solution of the present invention, when creating a file register group for storing file data, all registers in the file register group are specified as a certain original value. Use the system task $readmemb or $readmemh provided in the Verilog language standard to read the file. When the file data is read into the register of the file register group, the content of the file data will overwrite the original value of the register where it is located. In this way, it is possible to determine whether the register is empty by comparing whether the data content in the register is consistent with the original value of the register, and then know the file status information corresponding to the file register group, such as: whether the file is empty, the data in the file number, the end point of the file, and whether the file has been read.

[0026] Below, the preferred embodiment of the present invention is described in detail by taking the read operation process of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More