Semiconductor device and its manufacturing method

A technology of semiconductors and devices, which is applied in the field of semiconductor devices and the manufacture of such devices, and can solve problems such as unsatisfactory matching properties of DRAM cells

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Detailed description of the preferred embodiment

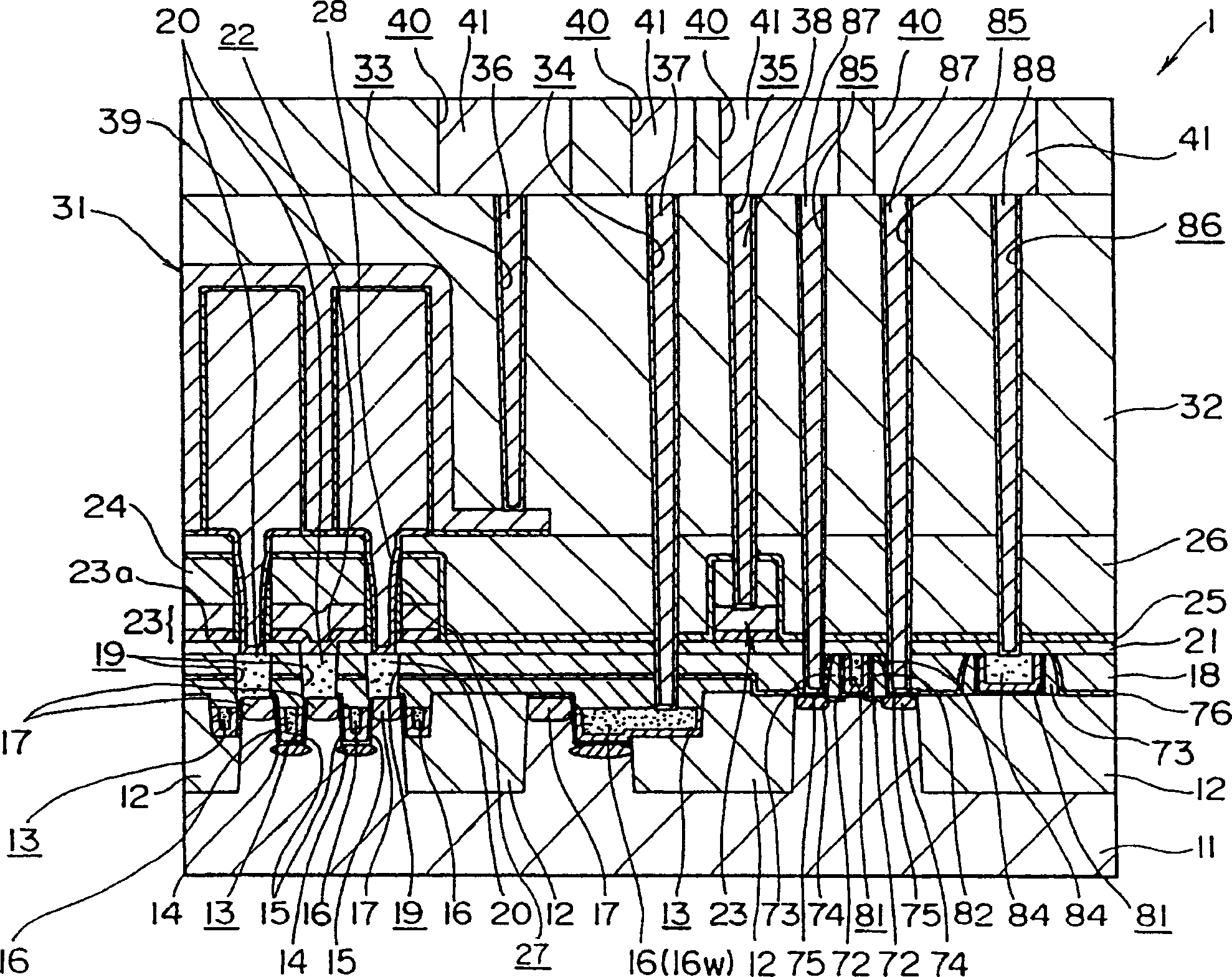

[0031] Referring now to the schematic cross-sectional view showing the structure of the device figure 1 An example of an embodiment of the semiconductor device according to the present invention will be described.

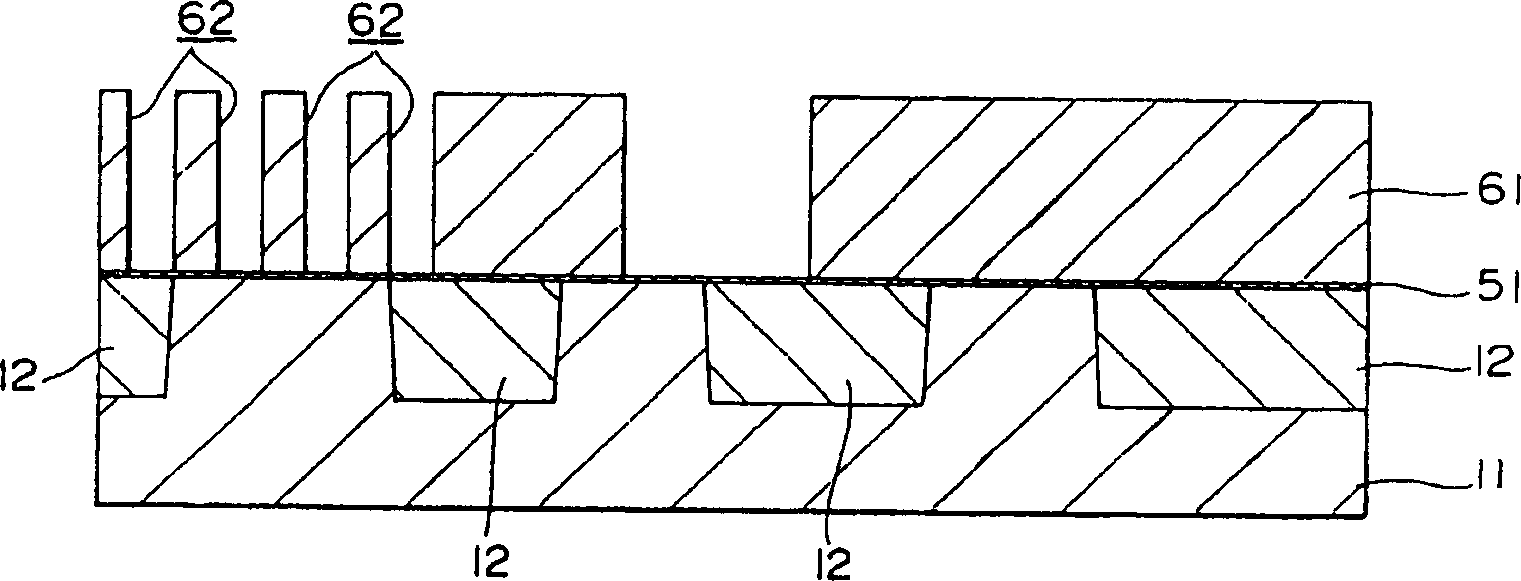

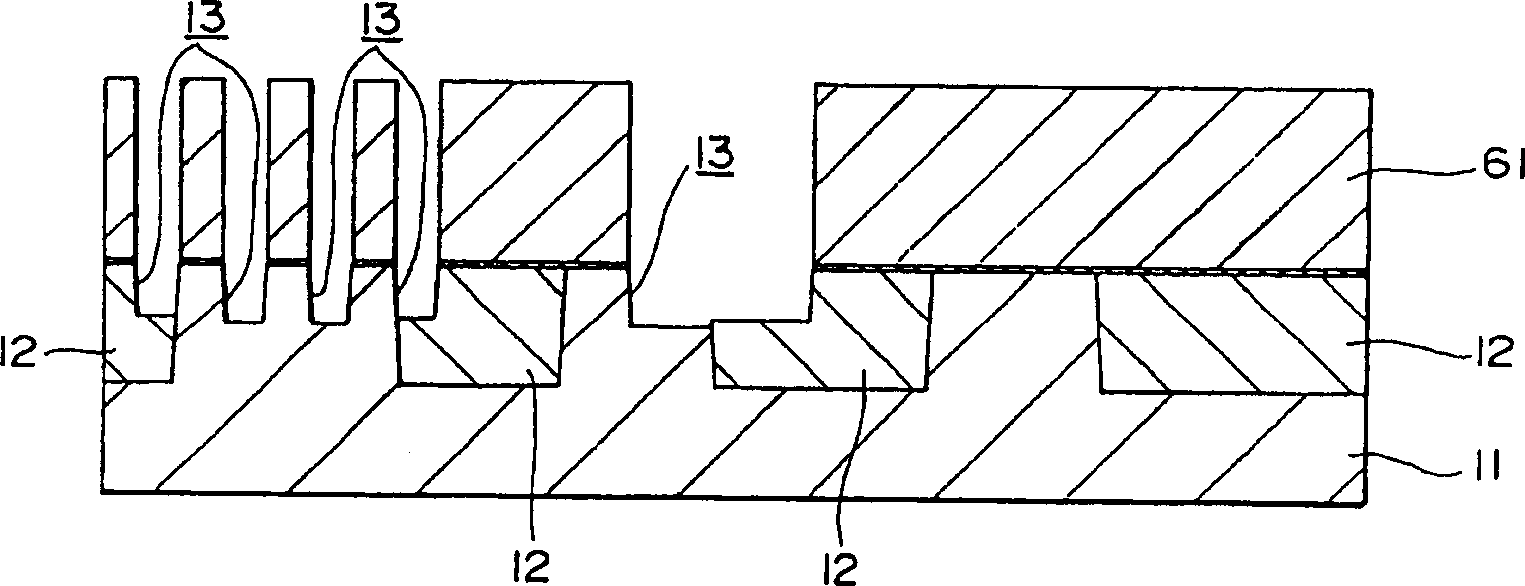

[0032] Such as figure 1 As shown, an element isolation region 12 is formed on a semiconductor substrate 11 .

[0033] STI (Shallow Trench Isolation) technology is used to make the element isolation region with a depth of 0.1-0.2 microns (μm). Grooves 13 having a depth of approximately 50 to 100 nanometers (nm) are formed on the semiconductor substrate 11 and the element separation region 12 . In the trench 13, a word line (gate electrode) 16 passing through the gate insulating film 15 is formed. Even if there is a difference between the depth of the groove 13 formed on the semiconductor substrate 11 and the depth of the groove 13 formed on the element separation region 12, there will be no problem.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More