Organic film transistor and preparing method

An organic thin film and transistor technology, which is applied in the field of the preparation of structured organic thin film transistors, can solve the problems of poor insulation performance of high dielectric materials, increase leakage current, etc., so as to increase channel capacitance, reduce turn-on voltage, and reduce adverse effects. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

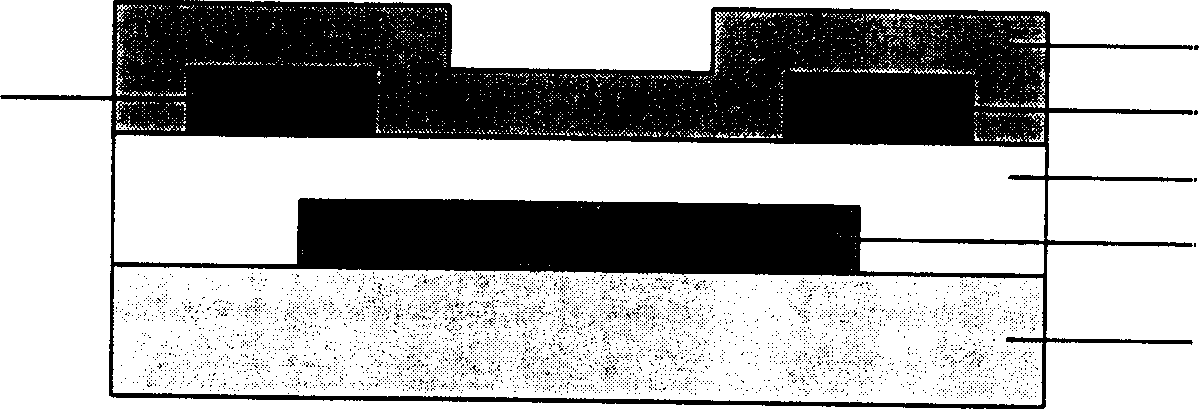

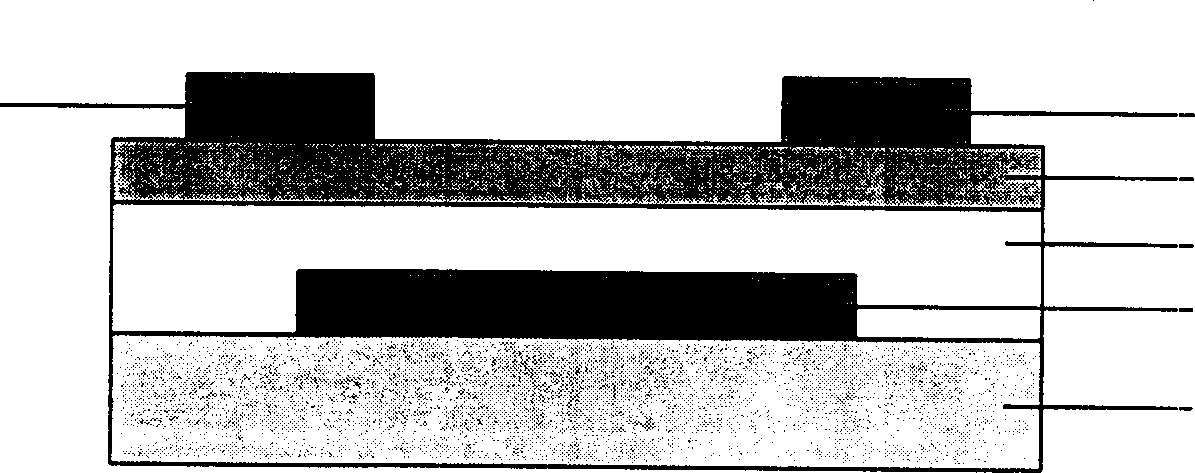

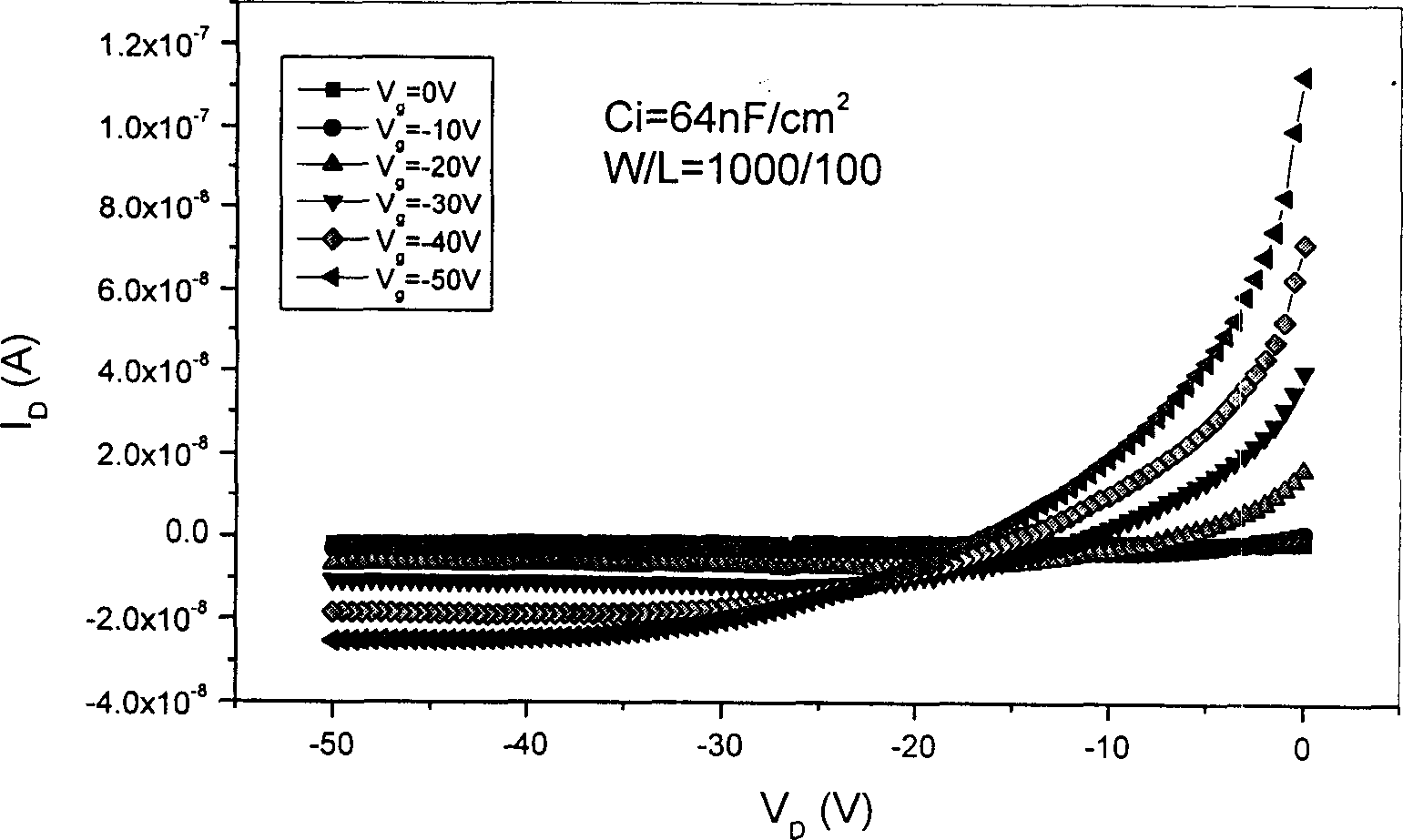

[0022] As shown in Figure 6, on the 7059 glass substrate 1, a layer of Ta metal film is plated on the 7059 glass substrate by the radio frequency magnetron sputtering method (the condition of sputtering is: background vacuum 2 × 10 -3 Pa; Ar gas pressure 1Pa; radio frequency power 500W; substrate temperature 100 degrees) and photolithography into the gate shape 2. A layer of 400 nm Ta was continuously sputtered by DC magnetron sputtering on the gate. 2 o 5 and a layer of 300 nm SiO 2 (reactive sputtering: background vacuum 2×10 -3 Pa; O 2 Air pressure 0.9Pa; DC power 500W; substrate temperature 100 degrees) as the gate insulating layer 3 and the second insulating layer 4 respectively. Then apply photoresist, expose, develop, and then use the photoresist as a drain plate in 10 -5 A layer of 100 nanometer gold (Au) is thermally evaporated under a high vacuum of Pa, and the sample is put into an acetone solvent to peel off the gold in the non-patterned area to form the sourc...

Embodiment 2

[0024] As shown in Figure 6, a layer of MoW alloy film is plated on the flexible plastic substrate 1 by radio frequency magnetron sputtering (the sputtering method is co-sputtering of Mo target and W target, and the condition of sputtering is: background vacuum 2×10 -3 Pa; Ar gas pressure 1Pa; radio frequency power 500W; substrate temperature 100 degrees) and photolithography into the gate shape 2. A layer of 500 nm Ta was sputtered on the grid by DC magnetron sputtering 2 o 5 (reactive sputtering: background vacuum 2×10 -3 Pa; O 2 air pressure 0.9Pa; DC power 500W; substrate temperature 100 degrees) as the gate insulating layer 3 , and then a layer of 300nm polymethyl methacrylate (PMMA) was spin-coated as the second insulating layer 4 . Next, apply photoresist, expose, develop, and then use the photoresist as a drain plate in 10 -5 A layer of silver (Ag) of 100 nanometers is thermally evaporated under a high vacuum of Pa, and the sample is put into an acetone solvent to...

Embodiment 3

[0026] As shown in Figure 6, a layer of chromium metal film is plated on the flexible plastic substrate 1 by radio frequency magnetron sputtering (the sputtering method is chromium target sputtering, and the sputtering condition is: background vacuum 2 × 10 -3 Pa; Ar gas pressure 1Pa; radio frequency power 500W; substrate temperature 100 degrees) and photolithography into the gate shape 2. A layer of 500nm TiO was sputtered on the grid by DC magnetron sputtering 2 (reactive sputtering: background vacuum 2×10 -3 Pa; O 2 air pressure 0.9Pa; DC power 500W; substrate temperature 150 degrees) as the gate insulating layer 3 , and then a layer of 300nm polyimide was spin-coated as the second insulating layer 4 . Next at 10 -5 A layer of 100 nanometer aluminum (AL) is thermally evaporated under a high vacuum of Pa, and then coated with photoresist, exposed, developed, and then photoetched to form a source electrode 5 and a drain electrode 6 . The channel width is 1000 microns, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More