Method for managing and allocating buffer storage during Ethernet interchange chip transmission of data

A technology for switching chips and data transmission, applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve the problem of increasing the complexity of data processing and circuit design, the tight timing design of multicast reference count tables, and increasing the cost of switching chips, etc. problems, to achieve the effect of improving data processing, improving work reliability, and improving practicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033]Below according to accompanying drawing and embodiment the present invention will be described in further detail:

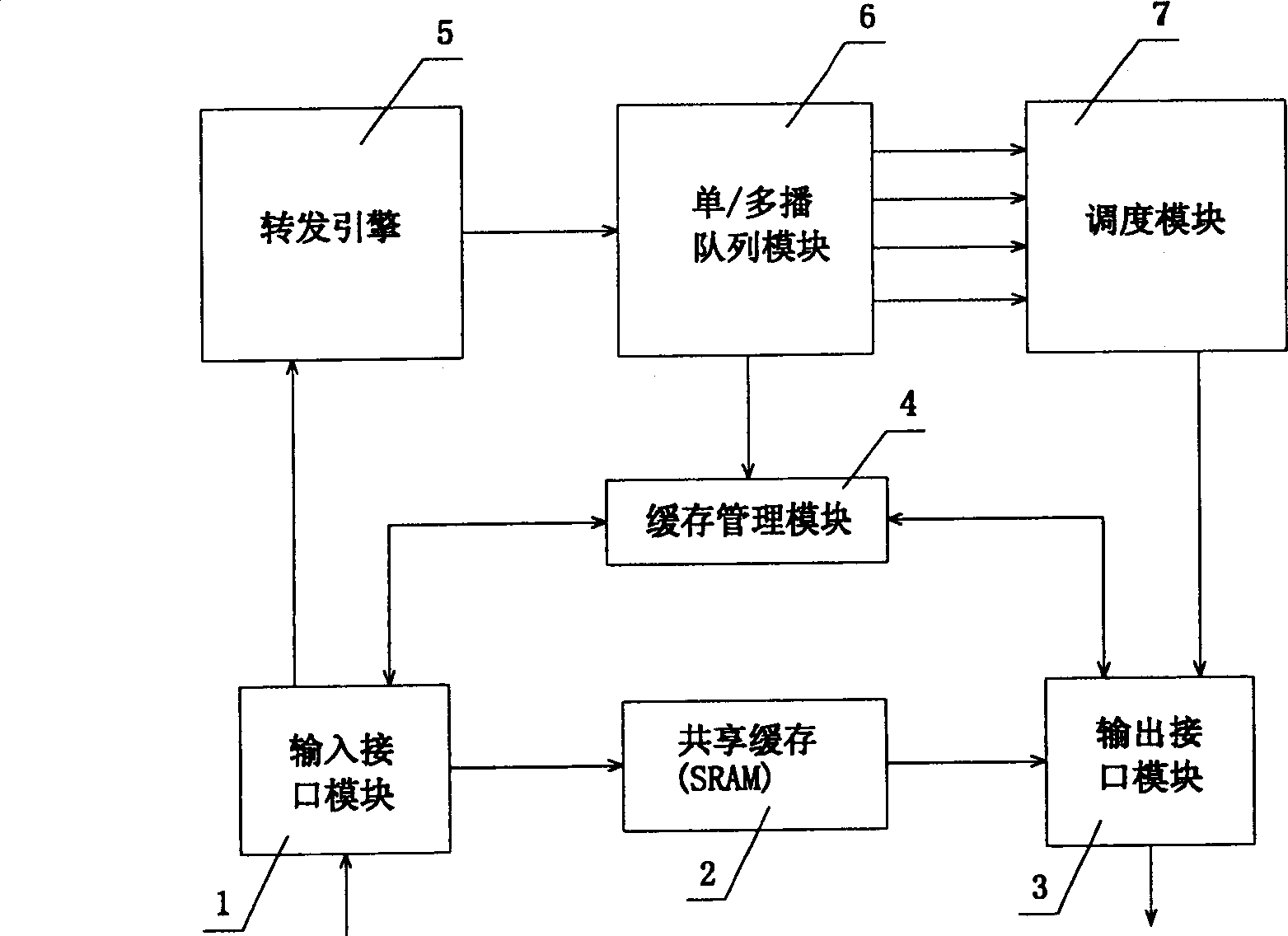

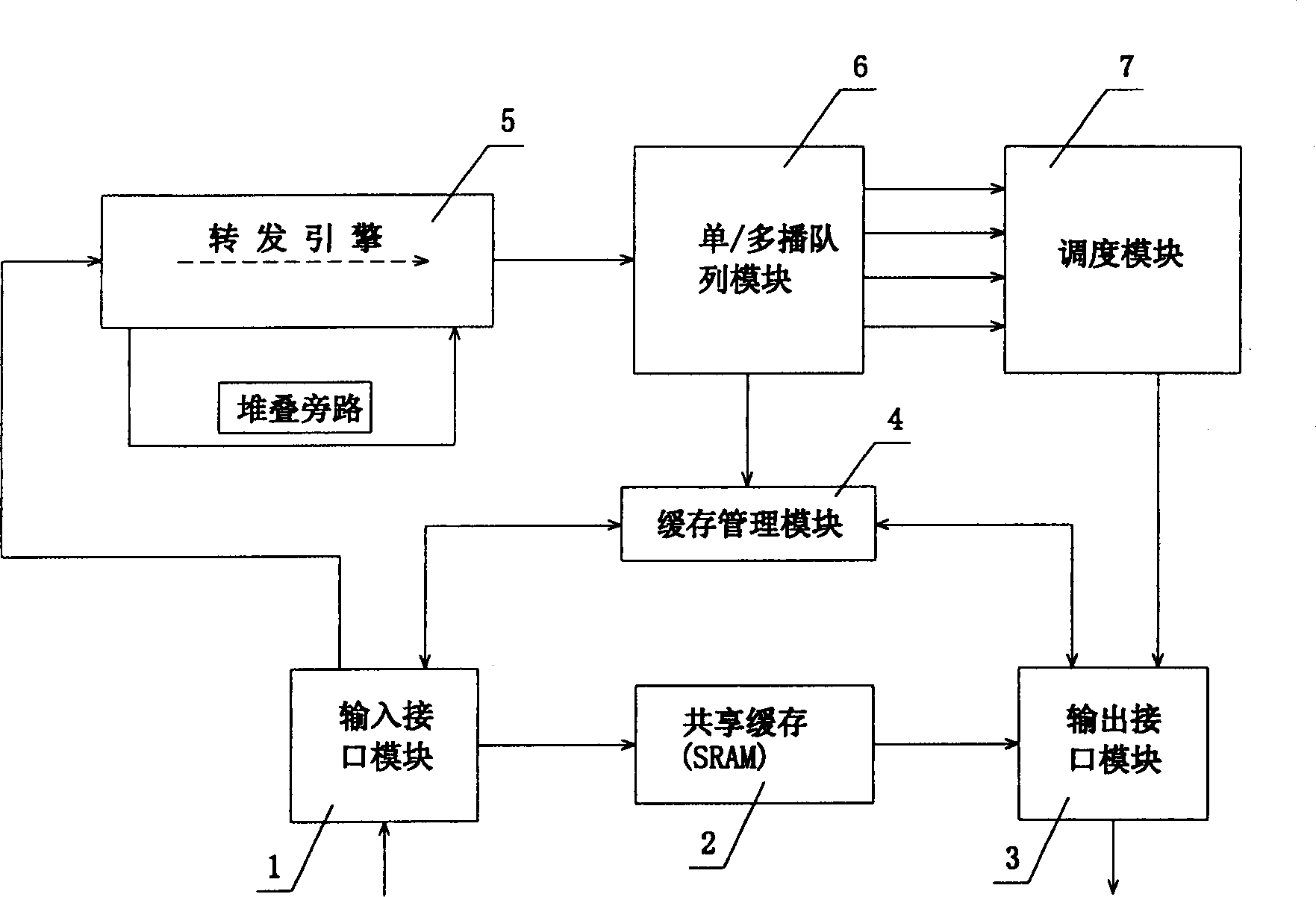

[0034] The number of ports provided with a switch chip is 27, such as image 3 As shown, a release weight table is used in the cache management module 4. The release weight table is a one-dimensional list, and each cache address pointer corresponds to one of the entries, and the value of the entry is the release value corresponding to the corresponding cache address pointer. The value of the weight, the shared cache has a total of 4K address pointers to maintain, each address pointer corresponds to a release weight table entry, the release weight table has a total of 4K entries, and the width of the entry is 5 bits. Using this cache management method The working process of the switch chip is as follows:

[0035] Such as image 3 As shown, when the switch chip is initialized, the initial value of each entry in the release weight table is set to 1FH, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More