Demodulation timing generation circuit and demodulation apparatus

A technology for generating circuits and circuits, applied in the direction of electrical components, modulated carrier systems, multiplexed communications, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

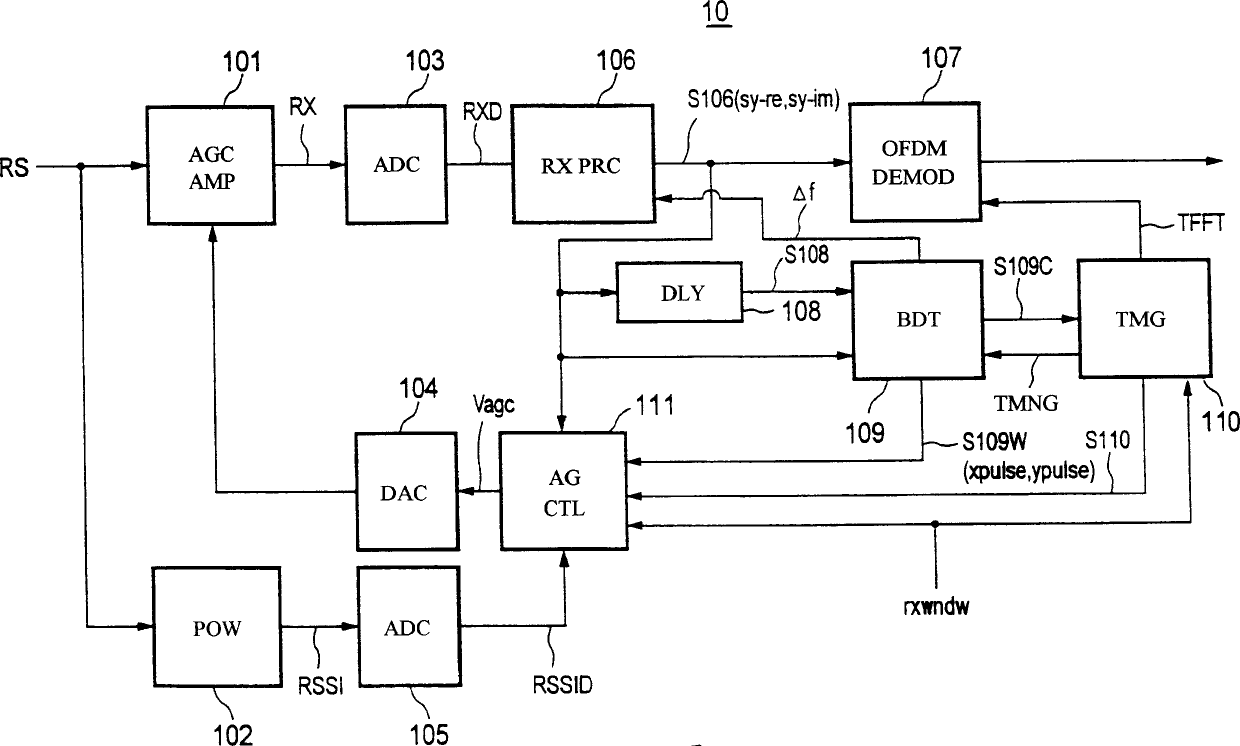

[0118] 1 is a block diagram showing the structure of a first embodiment of a burst synchronous demodulation apparatus to which an FFT timing generating circuit according to the present invention is applied.

[0119] As shown in Figure 1, the main components that burst pulse synchronous demodulation device 10 comprises are: automatic gain control amplifier (AGCAMP) 101, received signal power monitor (POW) 102, analog / digital (A / D) converter ( ADC) 103, digital / analog (D / A) converter (DAC) 104, A / D converter (ADC) 105, received signal processing unit (RXPRC) 106, OFDM demodulator (DEMOD) 107, delay unit ( DLY) 108, Burst Detector (BDT) 109, Timing Controller (TMG) 110 and Amplification Gain Controller (AGCTL) 111.

[0120] The automatic gain control system of the burst pulse synchronous communication system adopted in the present embodiment, transmission (reception) signal, and FFT timing optimization overview will be described in order below, and the burst pulse synchronous dem...

no. 2 example

[0402] Fig. 26 is a block diagram showing the structure of a second embodiment of a burst synchronous demodulation apparatus to which the FFT timing generating circuit according to the present invention is applied. Also, FIG. 27 is a circuit diagram of a specific structural example of the burst detector and timing controller of FIG. 26 according to the second embodiment of the present invention.

[0403] The second embodiment differs from the first embodiment explained above in that a frame synchronization function is added to the burst detector and the timing controller.

[0404] Specifically, in the second embodiment, by calculating the cross-correlation between the frame synchronization data (already known) and the input data, detection is performed only for the peak value that is in the detection window and exceeds the detection threshold, and after the synchronization is established according to The detection window is set by the frame period counted by the reference cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More