Storage test circuit

A memory testing and memory technology, applied in static memory, circuits, measuring electricity, etc., can solve the problems of deterioration of wiring characteristics, increased circuit size, and increased area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Afterwards, referring to the accompanying drawings, the present invention will be explained in more detail according to the embodiments of the present invention.

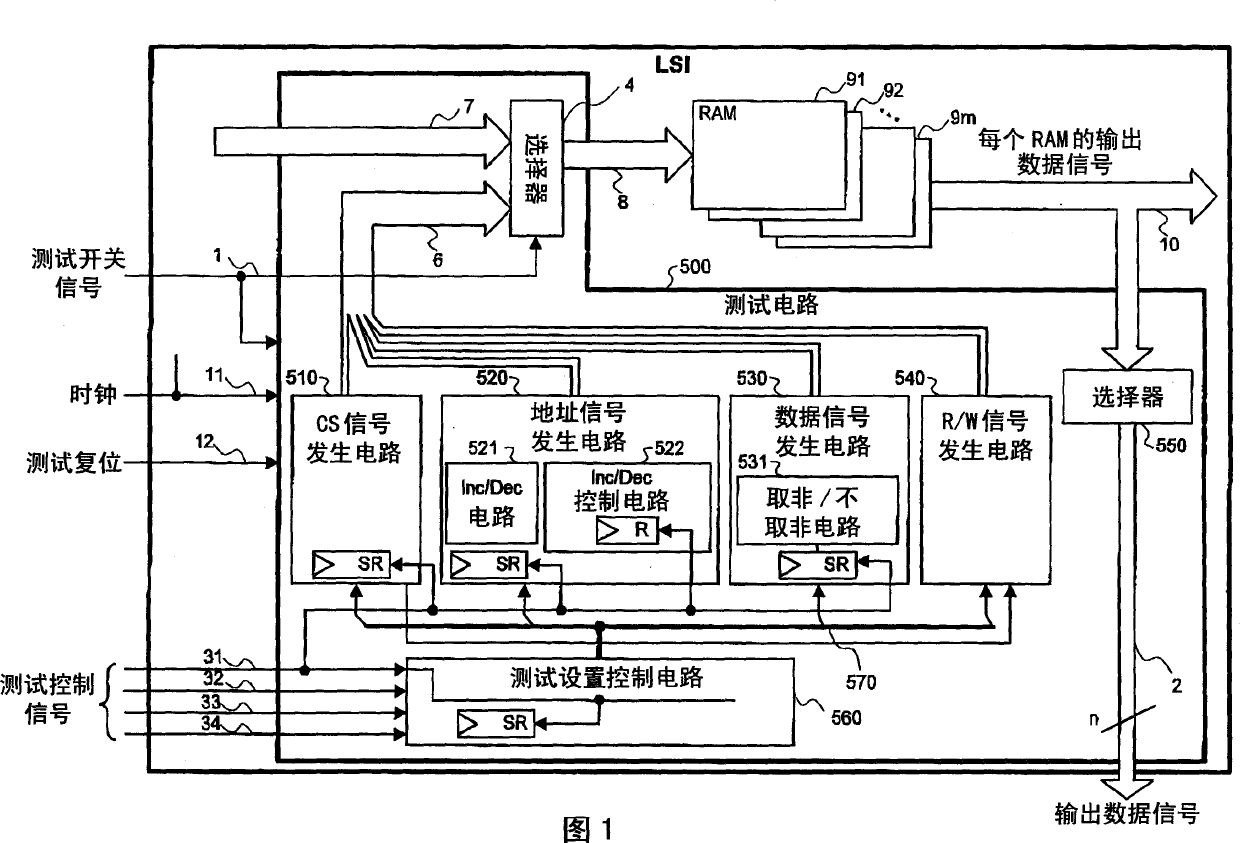

[0030] FIG. 1 shows the structure of an LSI having a memory test circuit related to an embodiment of the present invention. The LSI to which the memory test circuit of the present invention is applied has a plurality of RAMs 91 - 9m and a test circuit 500 .

[0031] The output 6 of the test circuit 500 is a data signal, an address signal, a chip select (CS) signal, and a read / write (R / W) signal which are input signals to each of the RAMs 91-9m during the test, and is connected with the select One input of selector 4 is connected, and the data signal, address signal, CS signal and R / W signal are connected to the other input of selector 4 as input signal 7 to each of RAM 91-9m during normal operation.

[0032] The selector 4 is mutually switched between the signals 6 and 7 by the test switch signal 1 input fro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More