Cutting multiplying accumulating unit with parallel processing

A technology of multiplication and accumulation and parallel processing, which is applied in the field of digital signal processors, can solve problems such as reducing the performance of large multipliers, and achieve the effects of saving area, small performance, and improving coding efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

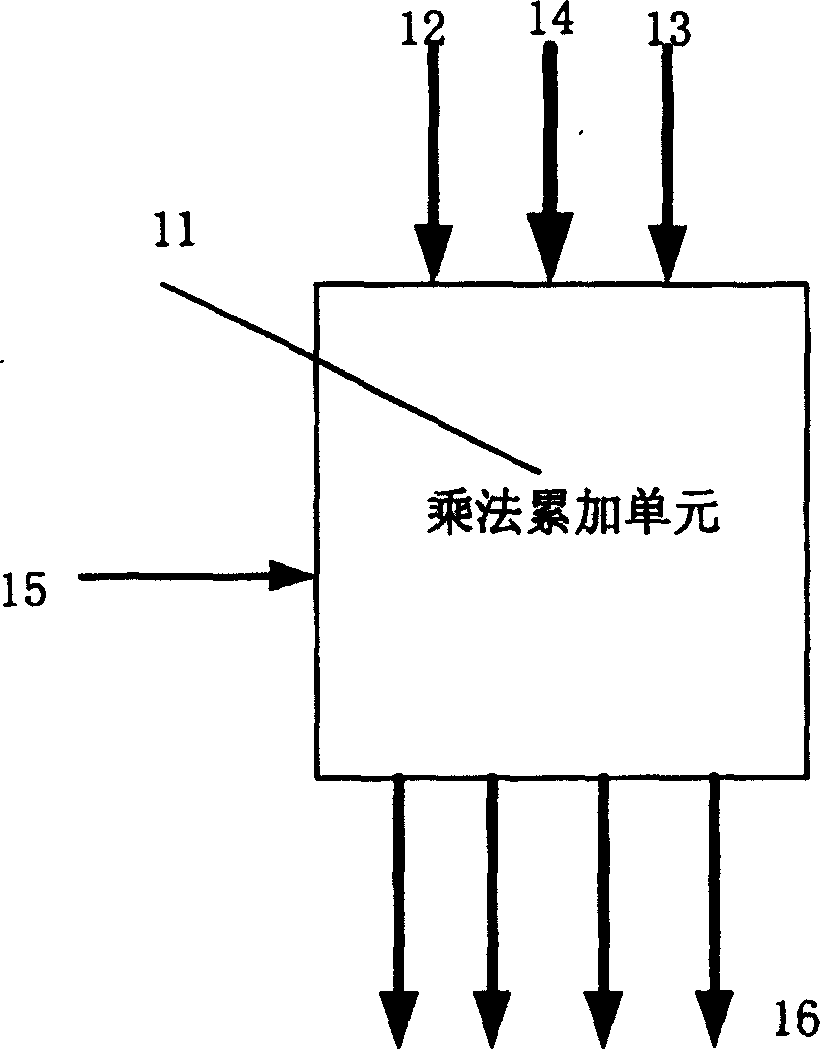

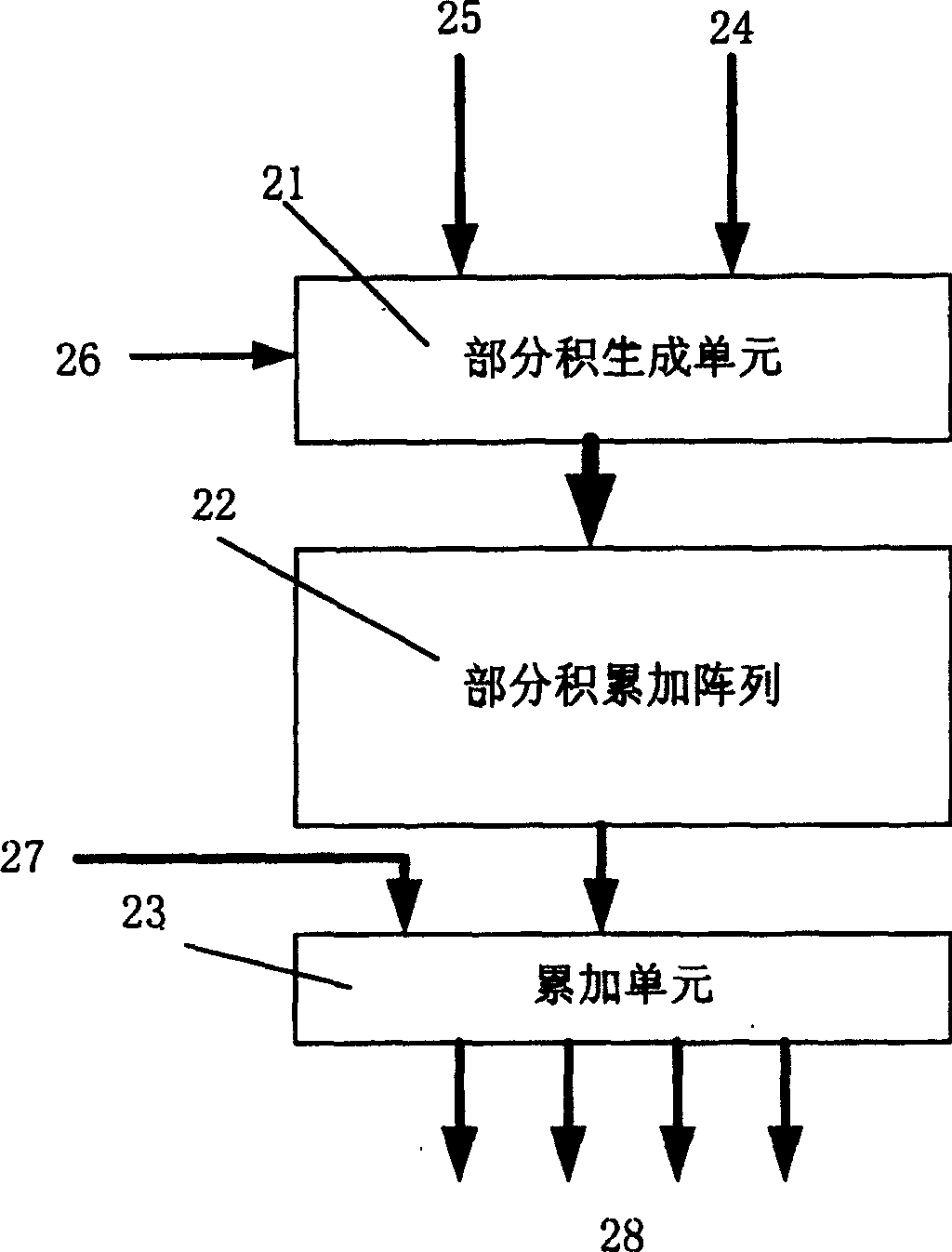

[0020] see figure 1 , the present invention a kind of parallel processing separable multiplication accumulation unit, which comprises: a partial product generation unit 21, a partial accumulation accumulation array 22, a divisible accumulator 23 constitutes; wherein the output end of the partial product generation unit 21 is connected The input end of the partial accumulation array 22; the output end of the partial accumulation array 22 is connected to the input end of the divisible accumulator 23; using this structure to realize 32-bit, 16-bit and 8-bit multiplication and accumulation operations.

[0021] Wherein the divisible partial product generating unit 21 is composed of 32 sub-generating units 41 (such as Figure 4 ), wherein the sub-generating unit is composed of an AND gate 51 and a two-input gate 52, wherein the output of the gate 52 is connected to an input of 51; the divisible partial product generating unit is according to different modes The control signals gene...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com