Method for operating semiconductor device and semiconductor device

A method of operation, semiconductor technology, applied in the direction of semiconductor devices, electric solid state devices, static memory, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

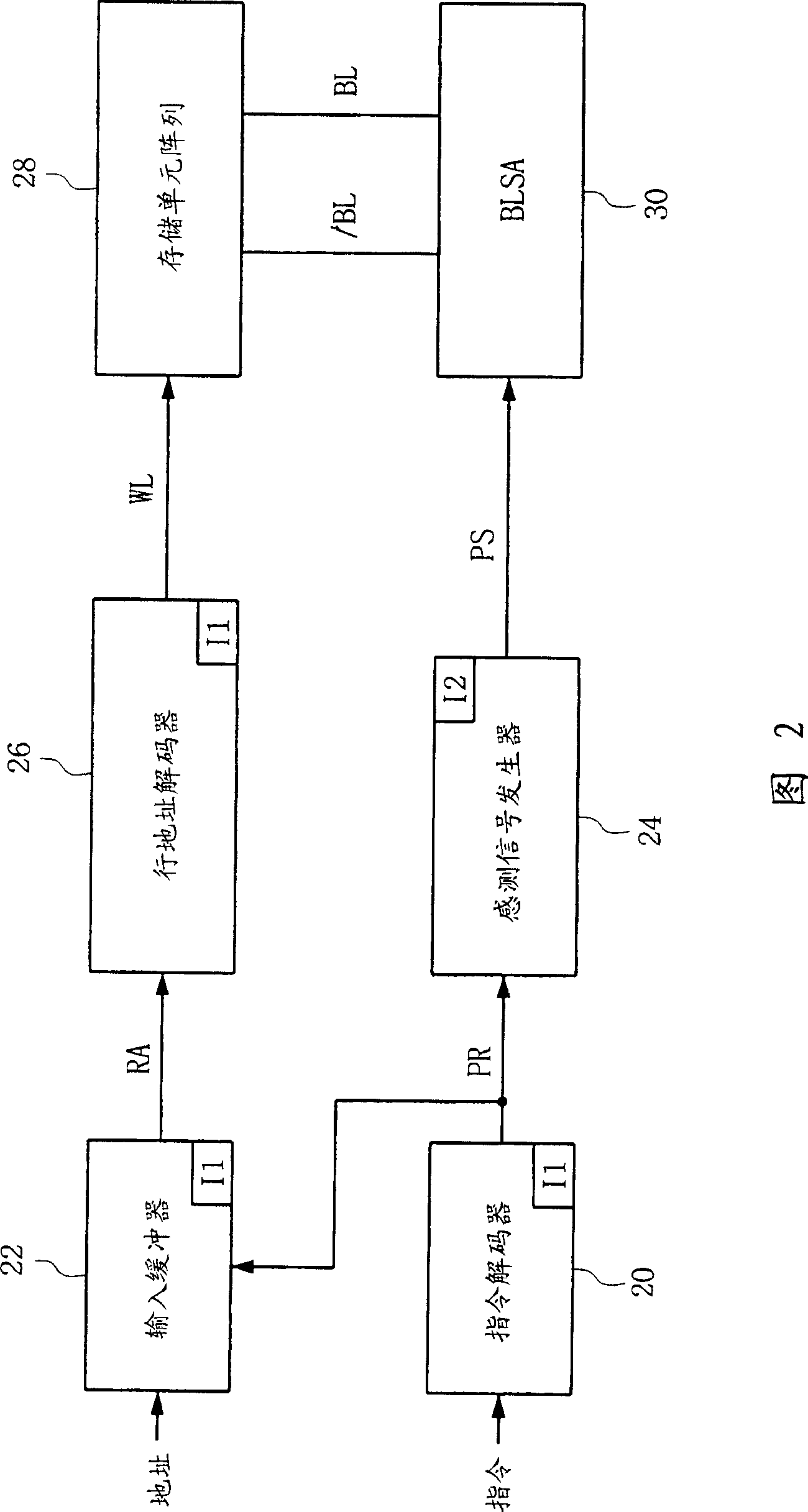

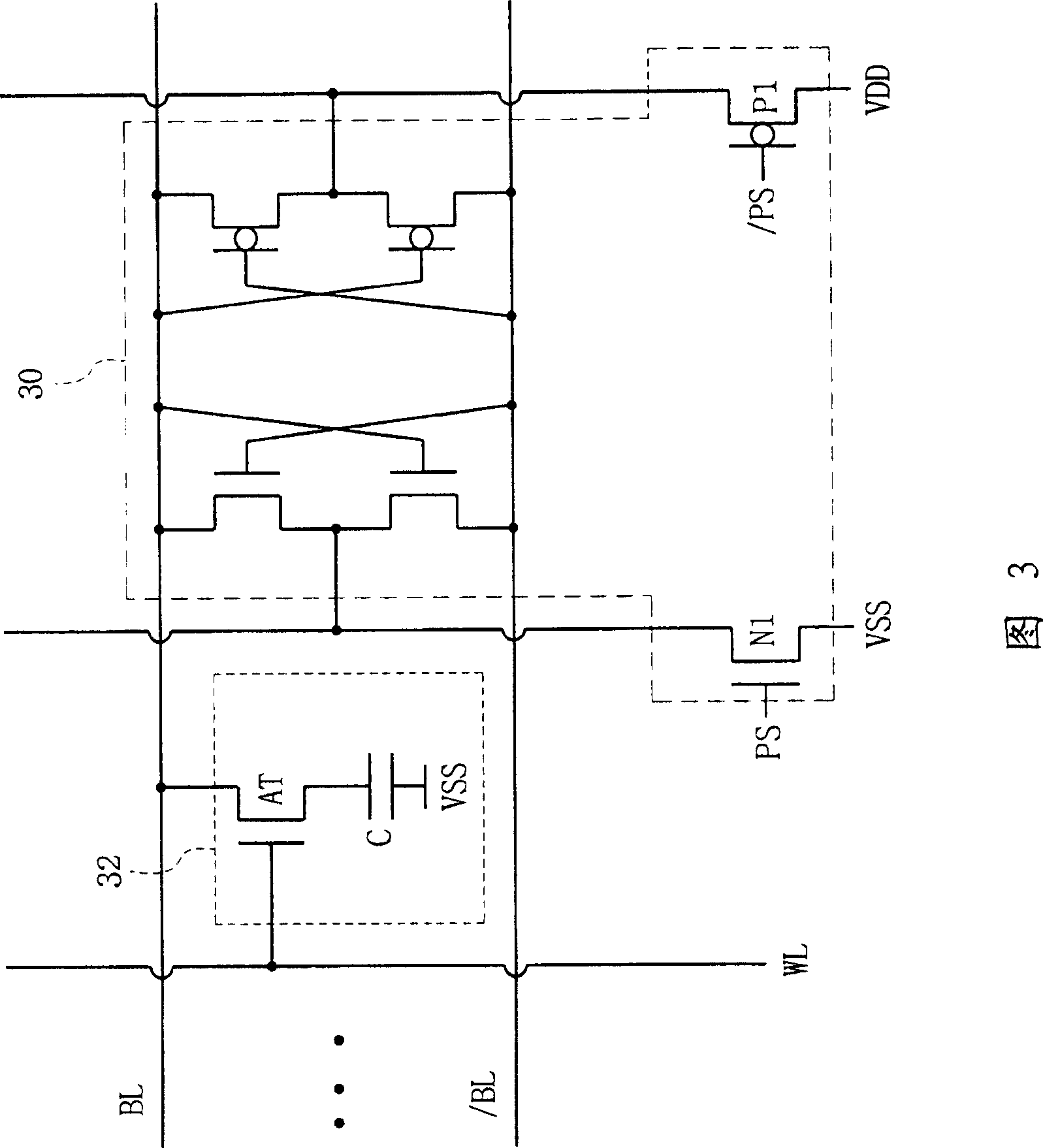

[0018] An inverter chain according to one embodiment of the present invention will be described, followed by an integrated semiconductor device incorporating the inverter chain.

[0019] inverter chain

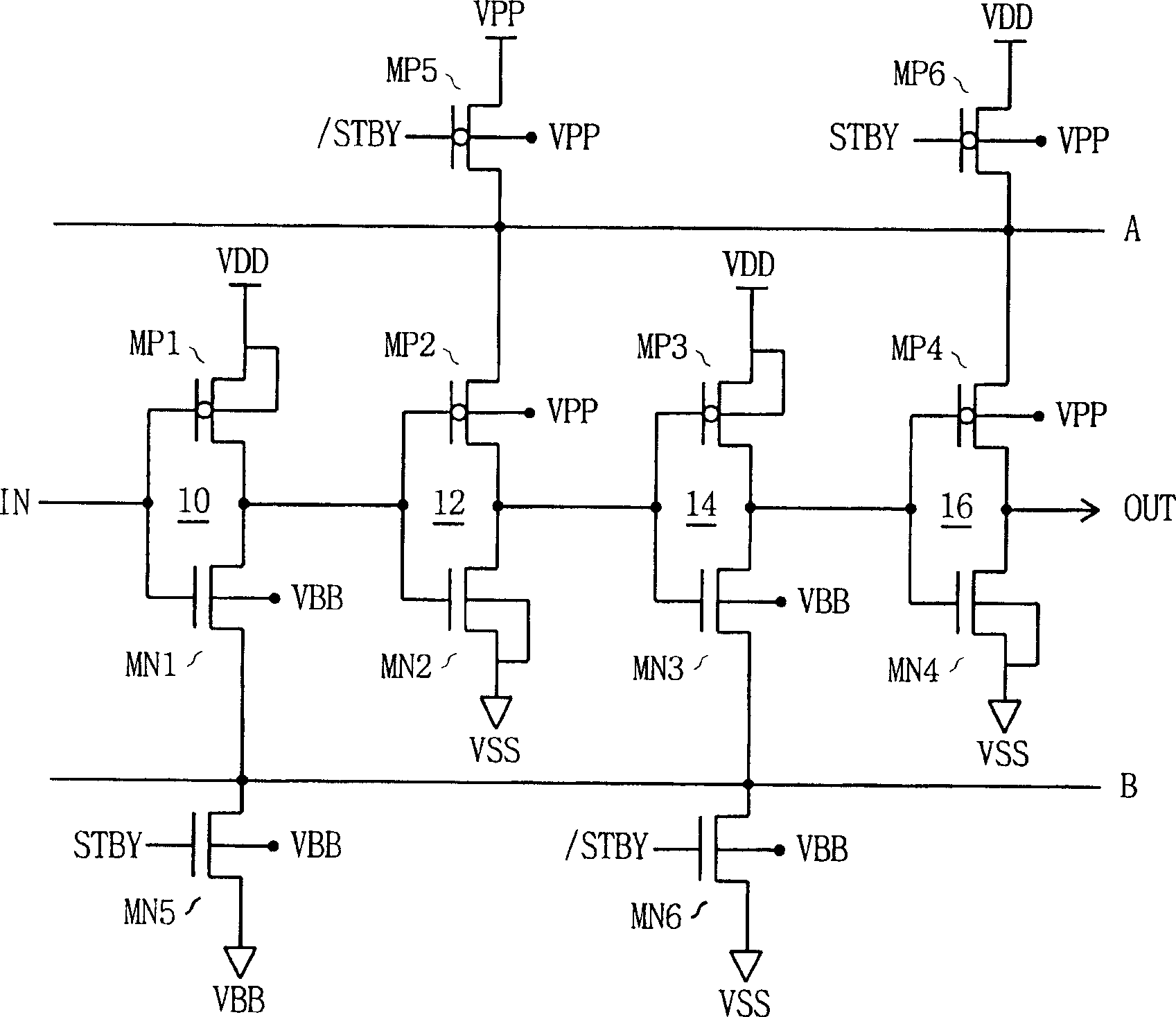

[0020] figure 1 A chain of CMOS inverters according to one embodiment of the invention is shown. As shown, the first-fourth CMOS inverters 10, 12, 14 and 16 are connected in series between the first inverter 10 receiving the input IN and the fourth inverter 16 generating the output OUT. Each of the first-fourth inverters 10, 12, 14 and 16 includes a PMOS transistor connected in series with an NMOS transistor.

[0021] In particular, the first inverter 10 comprises a first PMOS transistor MP1 connected in series with a first NMOS transistor MN1 between a first high potential or voltage VDD (eg 3 volts) and a low potential or voltage line B. As described in detail below, the low potential line B can carry a first low potential VSS (such as ground) or a second low potential VB...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More