Multilayer chip capacitor

A multi-layer chip and capacitor technology, applied in the direction of laminated capacitors, capacitors, fixed capacitor dielectrics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

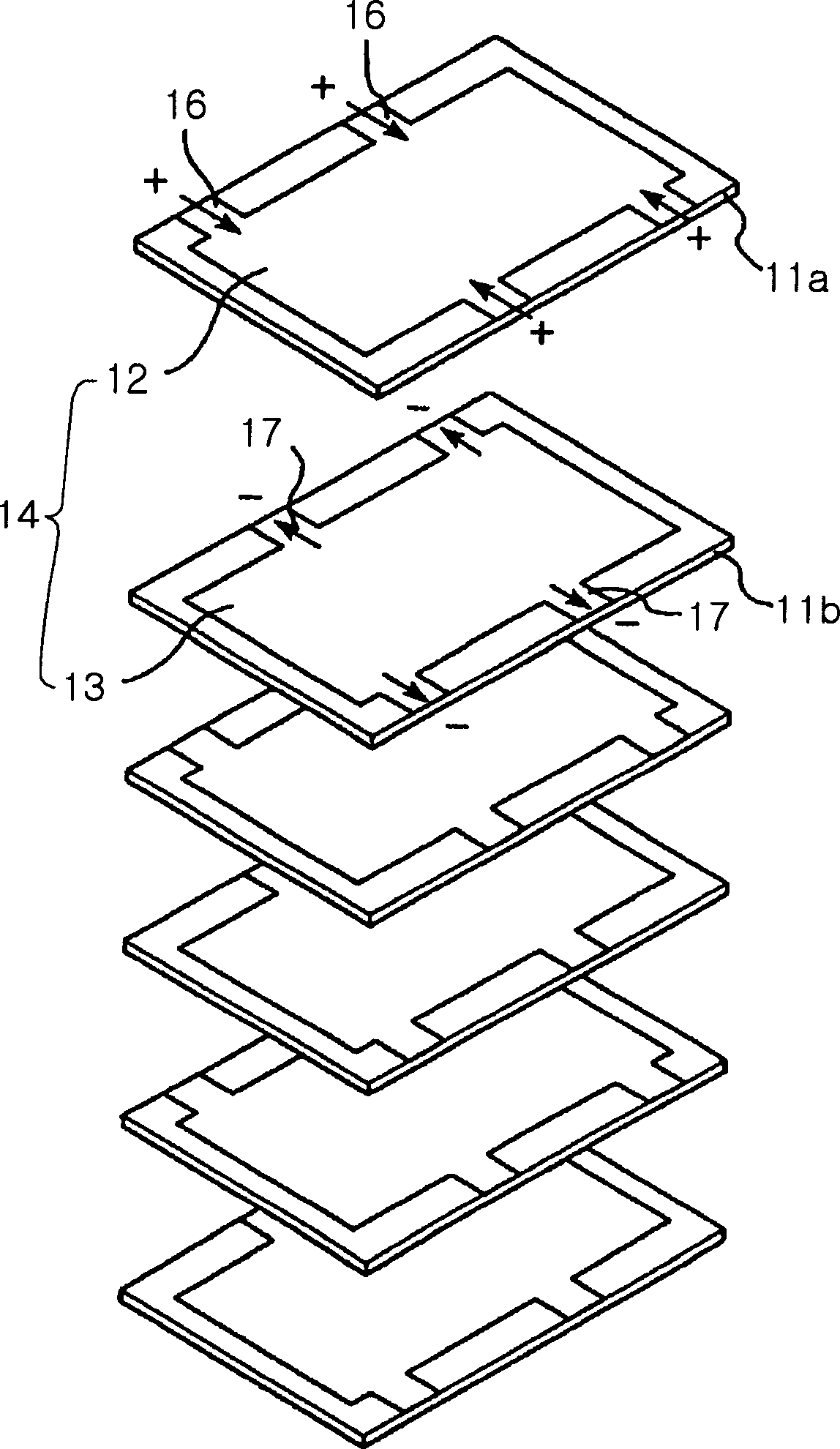

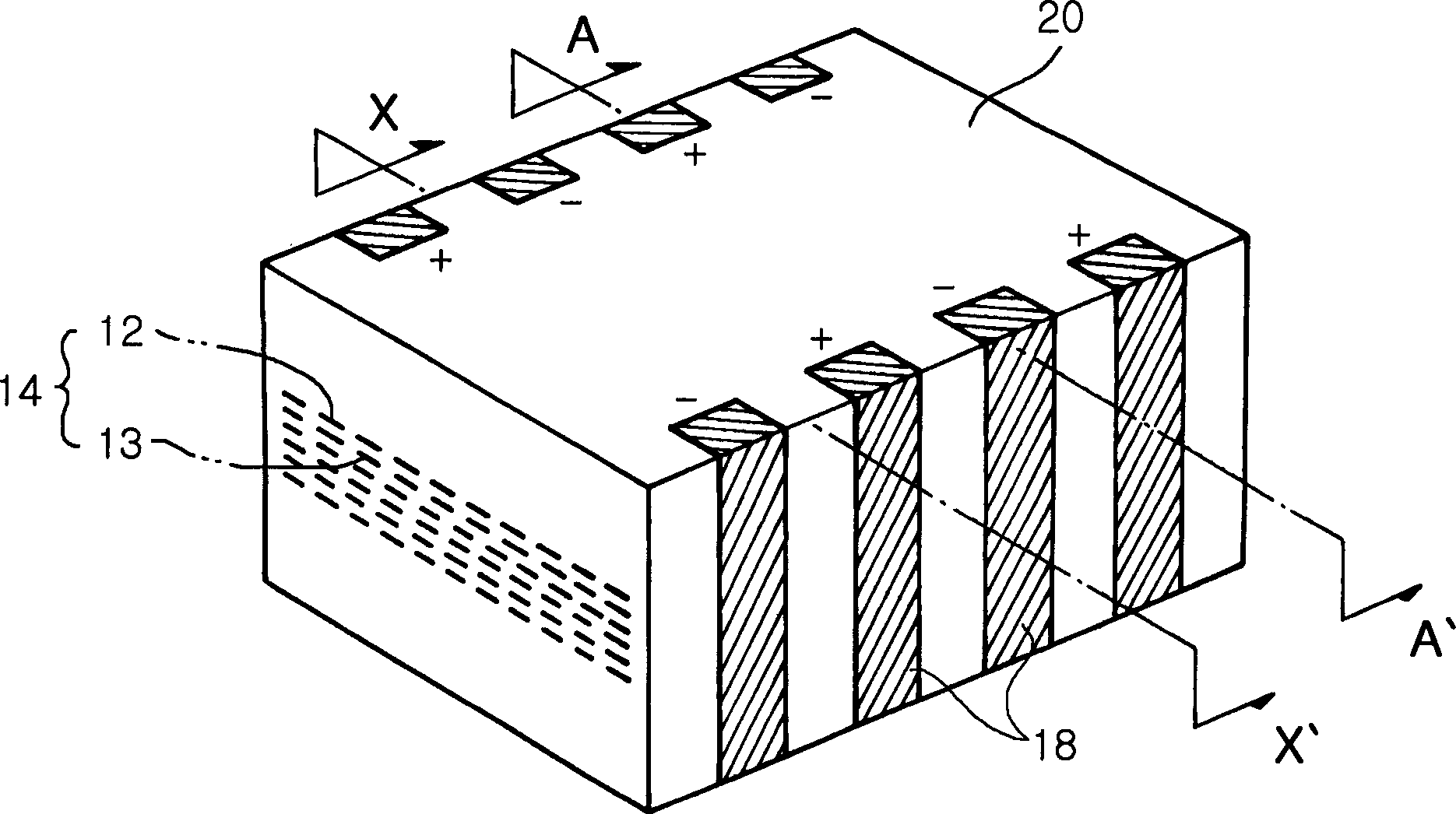

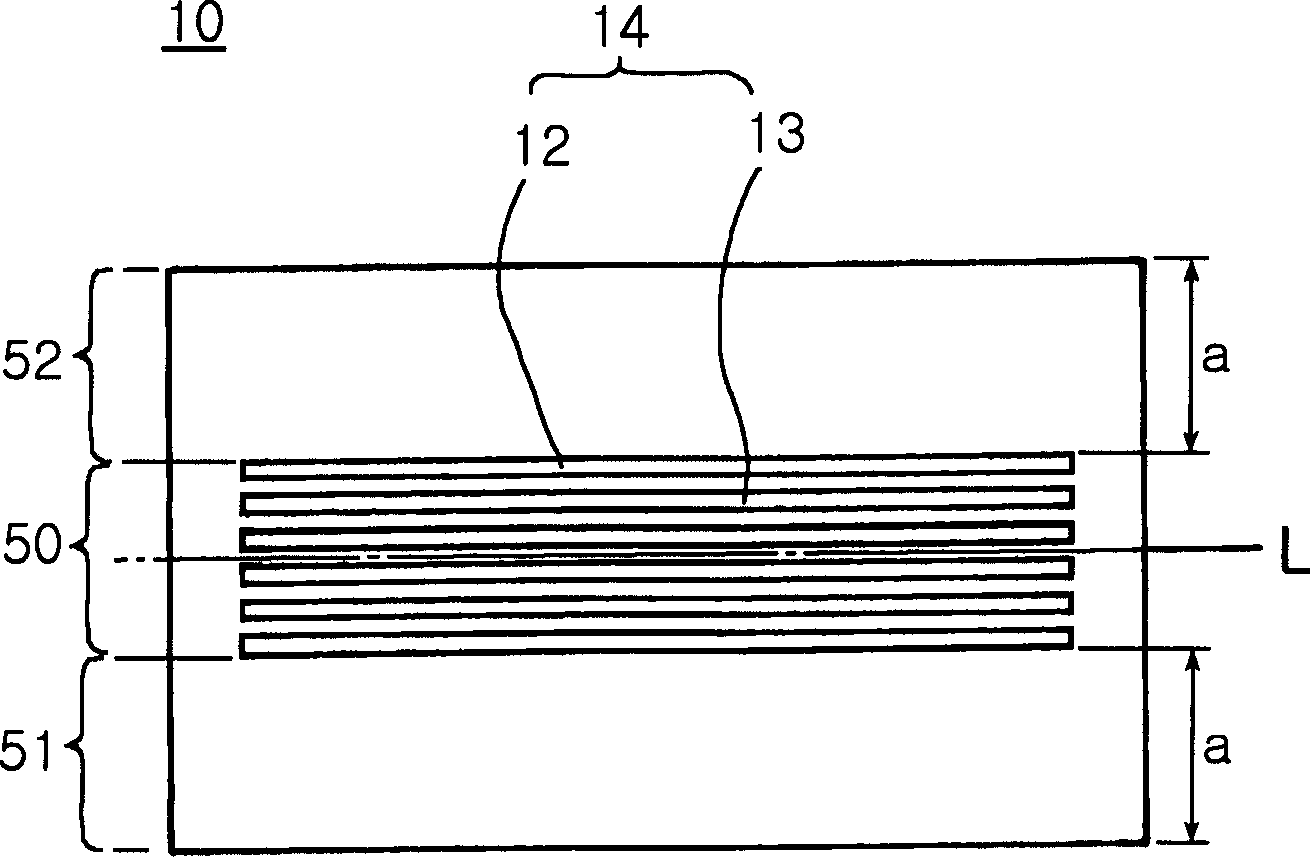

[0091] The present applicant conducted the following experiments to compare the ESL characteristics of conventional multilayer chip capacitors with multilayer chip capacitors according to three examples (first to third embodiments) of the present invention in order to observe the advantages of the present invention. Improvement of ESL characteristics of laminated chip capacitors. A conventional multilayer chip capacitor has an internal electrode structure as shown in FIG. 1a and a symmetrical cross-sectional structure as shown in FIG. 1c. The capacitors of the first to third examples have Figure 13 The internal electrode structure is shown. The multilayer chip capacitor of the first embodiment has Figure 4 As shown in the upper and lower asymmetric cross-sectional structure, the capacitor of the second embodiment has Figure 10 The upper and lower asymmetric cross-sectional structures shown, and the capacitor of the third embodiment have Figure 11 The upper and lower sym...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More