Chip packing structure and method

A technology of chip encapsulation and encapsulation method, which is applied in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., and can solve problems such as the influence of reliability of electronic components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The chip packaging method proposed by the present invention and the package structure produced by it will be described below through different embodiments.

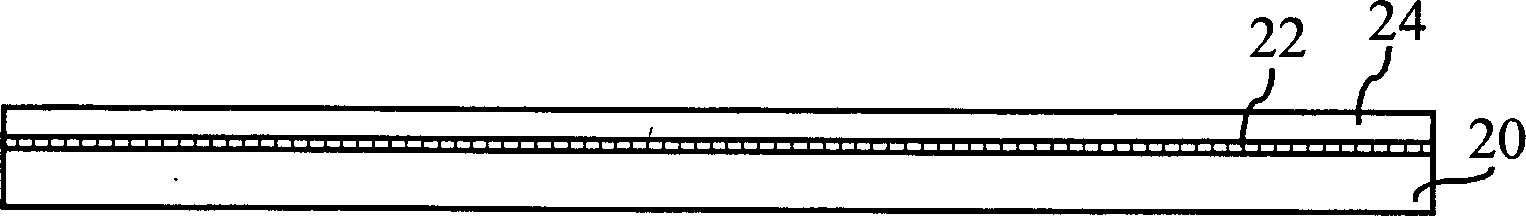

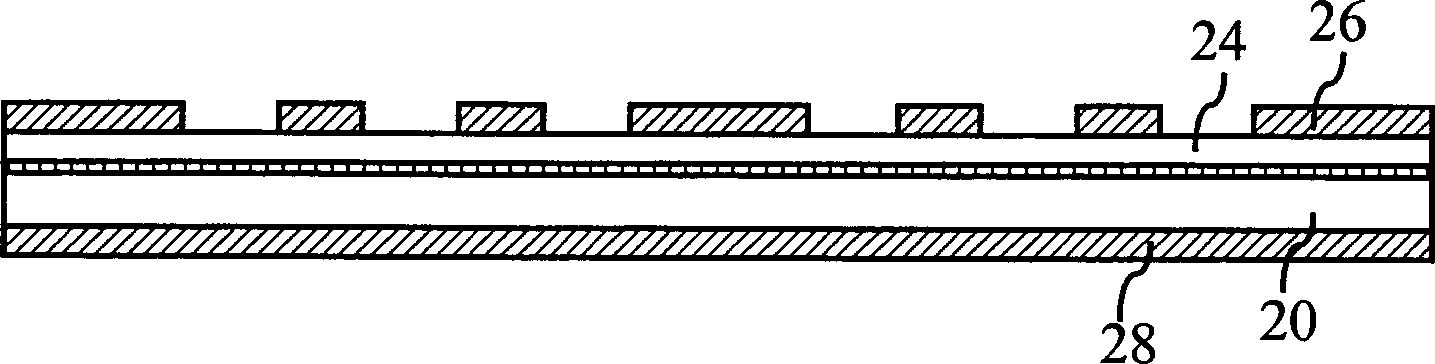

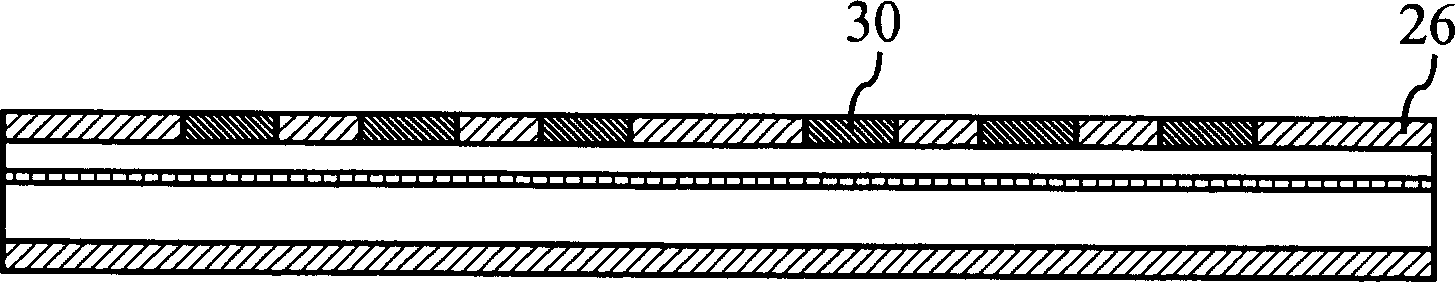

[0022] Figure 1(a) to Figure 1(h) Shown is the cross-sectional view of each step of the packaging method of the chip packaging structure of the present invention. First, as shown in FIG. An adhesive layer 22 and a conductive layer 24 are sequentially arranged on the surface from bottom to top, wherein the carrier board 20, the adhesive layer 22 and the conductive layer 24 can be integrated into a commercialized structure, or can be divided into three steps. , first use the pasting method, printing, spin coating, sputtering method, electroless plating method or electroplating method, such as the sputtering method to set the adhesive layer 22 on the carrier plate 20, and then use the pasting method, printing, sputtering method, The electroless plating method or the electroplating method disposes the conductive layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More