Semiconductor package structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of substrate exposure, yield problem, and package body easily damped, and achieve stable packaging structure , the effect of enhancing the heat dissipation capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

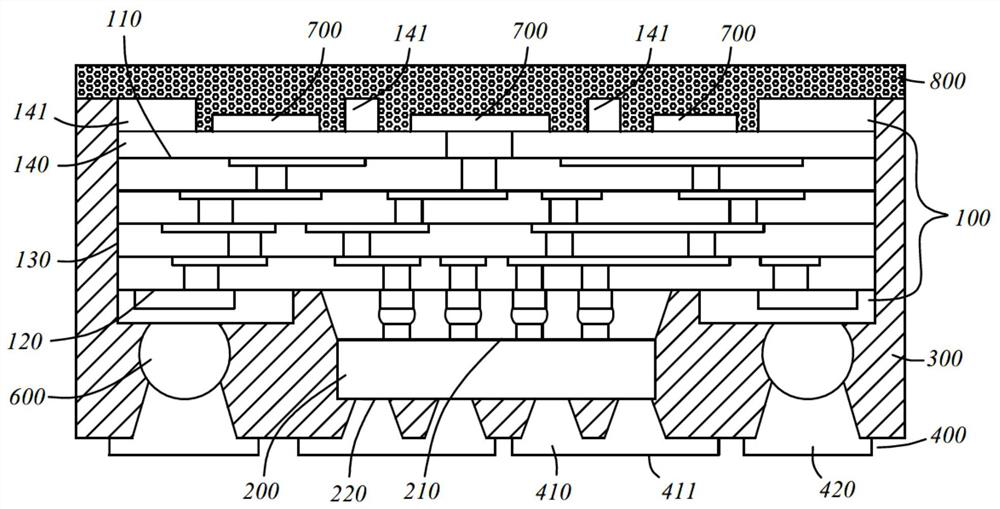

[0103] ginseng figure 1 As shown, in the first embodiment of the present invention, the semiconductor package structure includes a main substrate 100 , a chip 200 , a plastic encapsulation layer 300 and a back gold layer 400 .

[0104] Specifically, the main body substrate 100 includes an upper surface circuit 110, an opposite lower surface circuit 120, and a side surface 130 connecting the upper surface circuit 110 and the lower surface circuit 120, and the upper surface circuit 110 and the lower surface circuit 120 of the main body substrate 100 It should be noted that the main substrate 100 mentioned in the embodiment of the present invention can be stacked using a homogeneous or heterogeneous circuit board structure, and the main body is realized by setting an electrical connection structure in the circuit board and stacking each other. The upper and lower sides of the substrate 100 are electrically connected.

[0105] At the same time, the chip 200 includes a first conne...

Embodiment 2

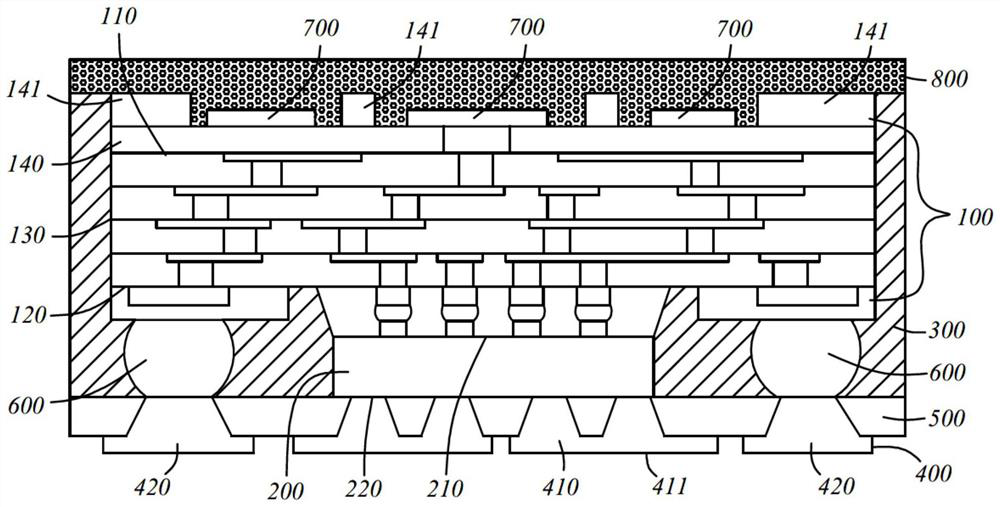

[0113] ginseng figure 2 As shown, the main difference between the second embodiment of the present invention and the first embodiment is that the plastic encapsulation layer 300 does not completely cover the chip 200 and the 3D connection part 600, and the plastic encapsulation layer 300 is flush with the second connection surface 220, The 3D connection part 600 is at least partially exposed.

[0114] At the same time, the semiconductor package structure also includes a stress-buffering dielectric layer 500 covering both the second connection surface 220 and the plastic encapsulation layer 300 , and the first metal connection part 410 is connected to the second connection surface 220 through the stress-buffering dielectric layer 500 , and the extended surface 411 protrudes out of the stress-buffering dielectric layer 500 .

[0115] In the second embodiment of the present invention, the protection of the chip 200 is enhanced by covering the second connection surface 220 and t...

Embodiment 3、 Embodiment 4 and Embodiment 5

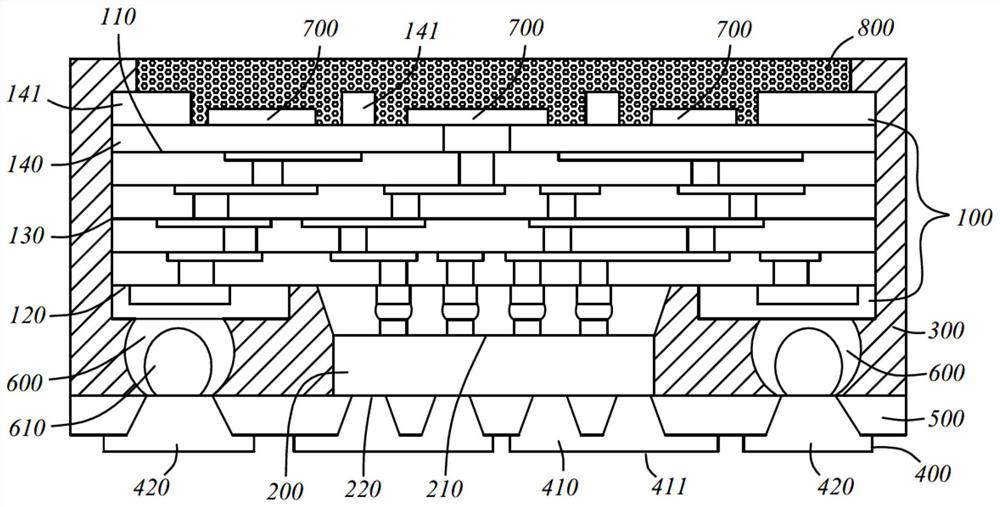

[0118] combine image 3 , Figure 4 with Figure 5 As shown, on the basis of the second embodiment of the present invention, by changing the specific structure of the 3D connection part 600, the present invention also proposes a third embodiment, a fourth embodiment and a fifth embodiment.

[0119] ginseng image 3 As shown, in the third embodiment, the 3D connection part 600 is provided with a metal heat sink 610, specifically, the 3D connection part 600 is set as a solder ball, the metal heat sink 610 is set as a copper core ball, and the copper core ball is wrapped The 3D connection part 600 is formed by covering and inside the solder ball, which enhances the heat dissipation performance after the connection between the 3D connection part 600 and the second metal connection part 420 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More