Processor unit efficiency control

a technology of efficiency control and processor, applied in computing, instruments, climate sustainability, etc., can solve the problems of significantly increasing the thermal load on the processor or other components within the electronic device, reducing system efficiency and battery life, etc., to reduce the power consumption of the processor complex, reduce the energy cost, and reduce the power consumption of the processor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

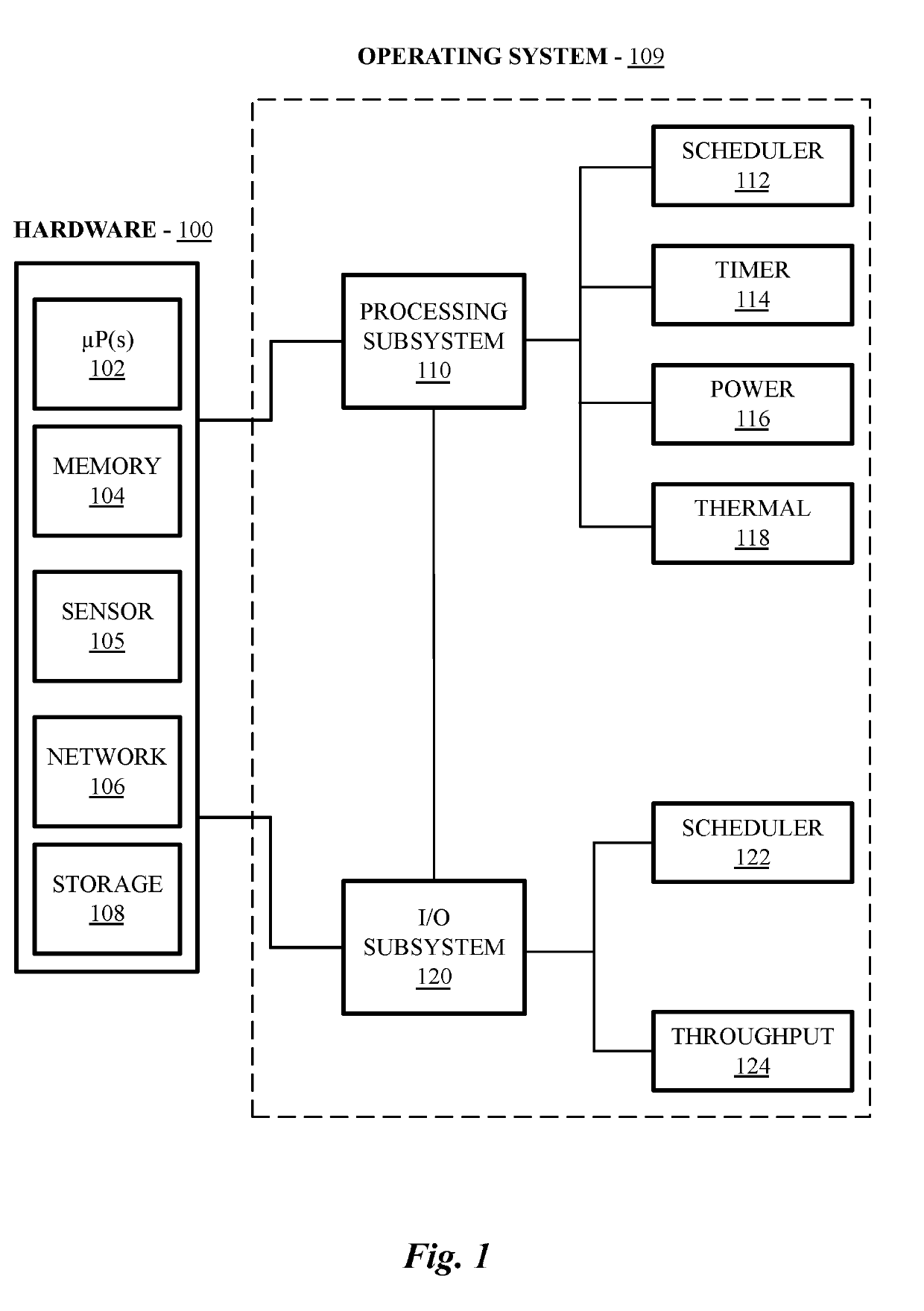

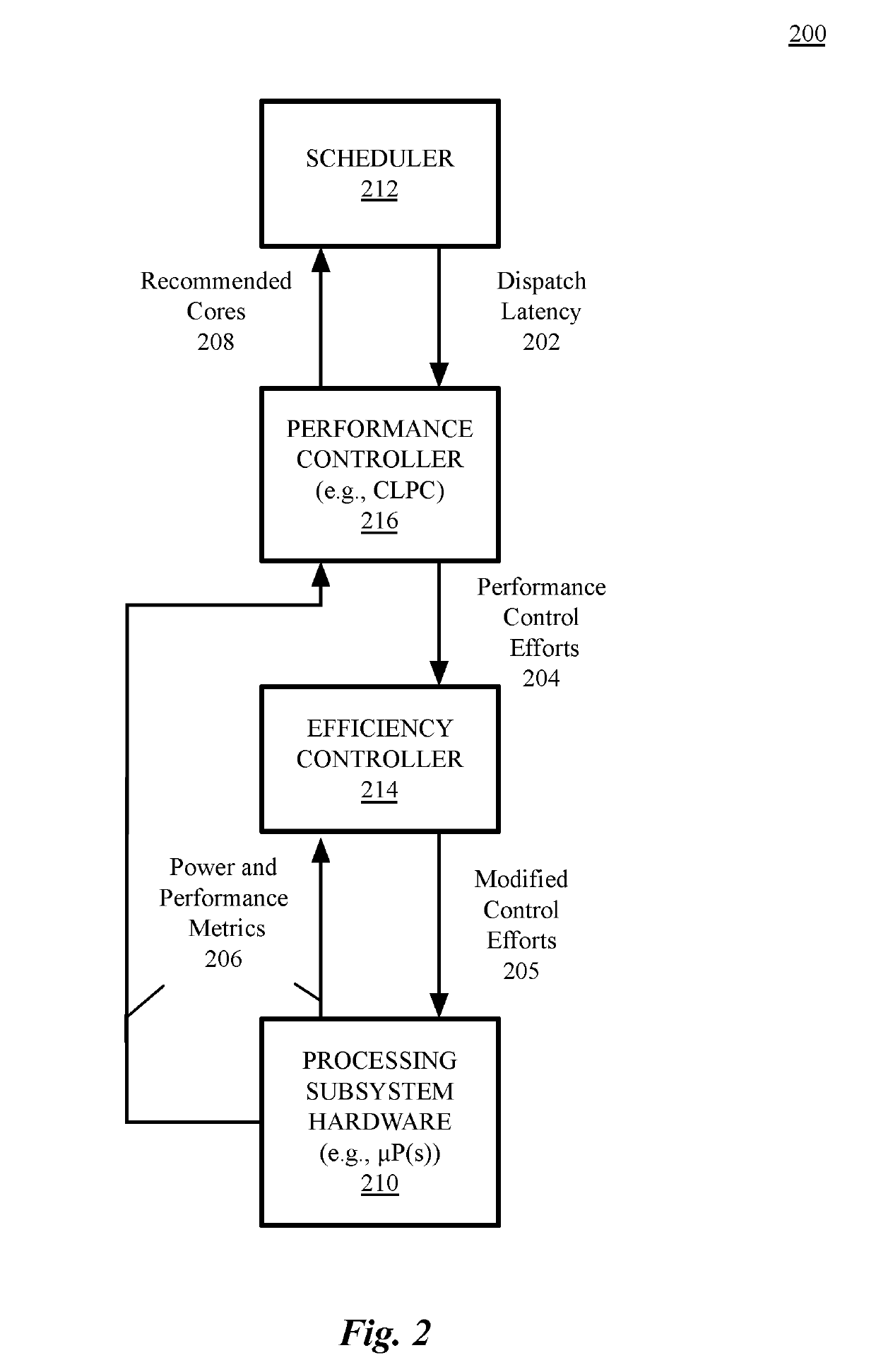

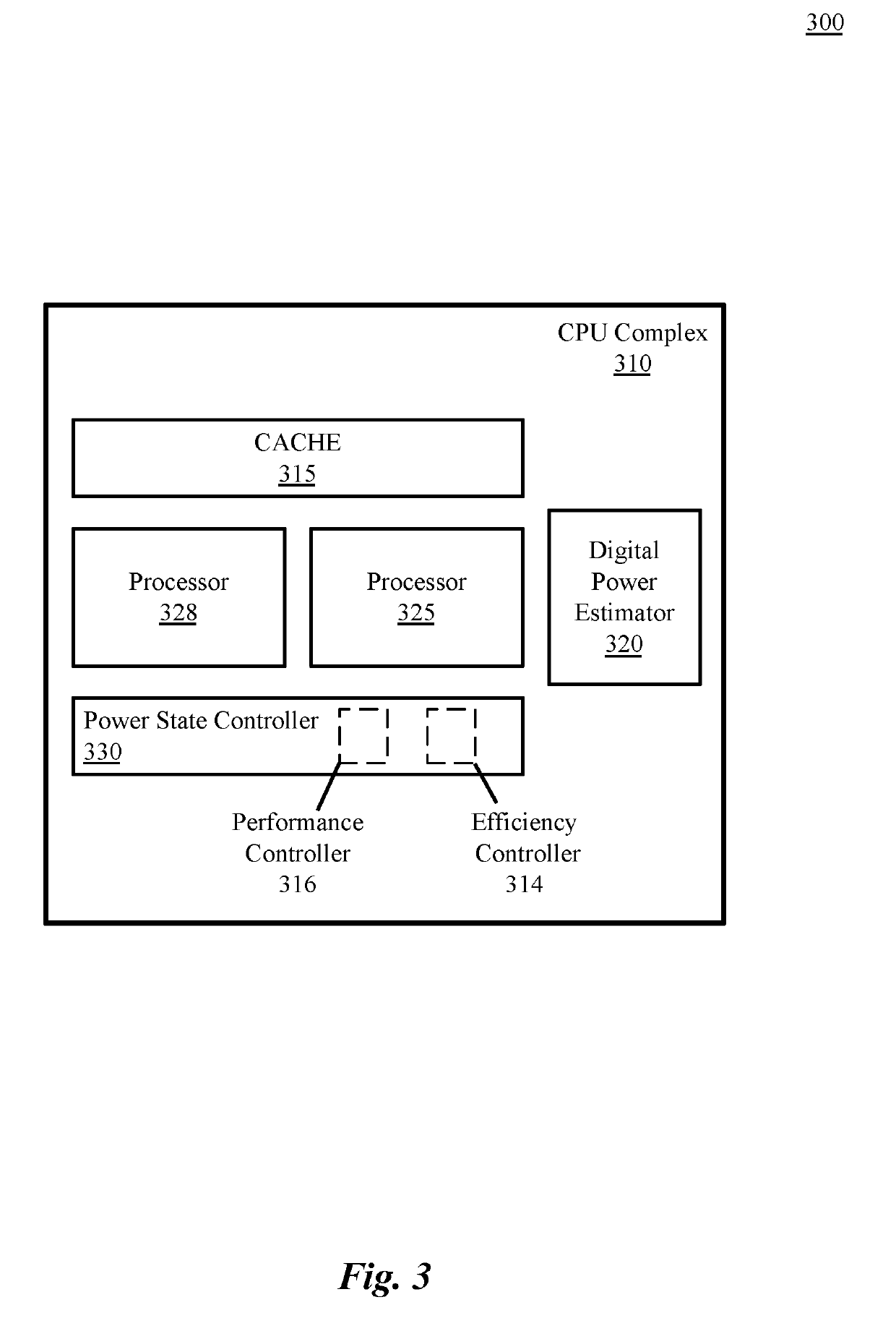

[0024]Various embodiments described herein provide for processor unit efficiency control. In one embodiment an efficiency control system for a data processing system includes an efficiency control module that can be integrated within an efficiency controller. The efficiency control effort module can be configured to determine a processor efficiency metric and limit the maximum levels of processor performance to workloads that execute efficiently on the processor, while causing the processor to execute inefficient workloads at a lower level of processor performance. In one embodiment the processing efficiency is determined as a measurement of energy consumed per instruction. The energy consumption estimates can be analyzed in light of instruction rate metrics reported by a processor or a group of processors.

[0025]Reference in the specification to “one embodiment” or “an embodiment” means that a particular feature, structure, or characteristic described in conjunction with the embodim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More