Patents

Literature

557results about "Single machine energy consumption reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

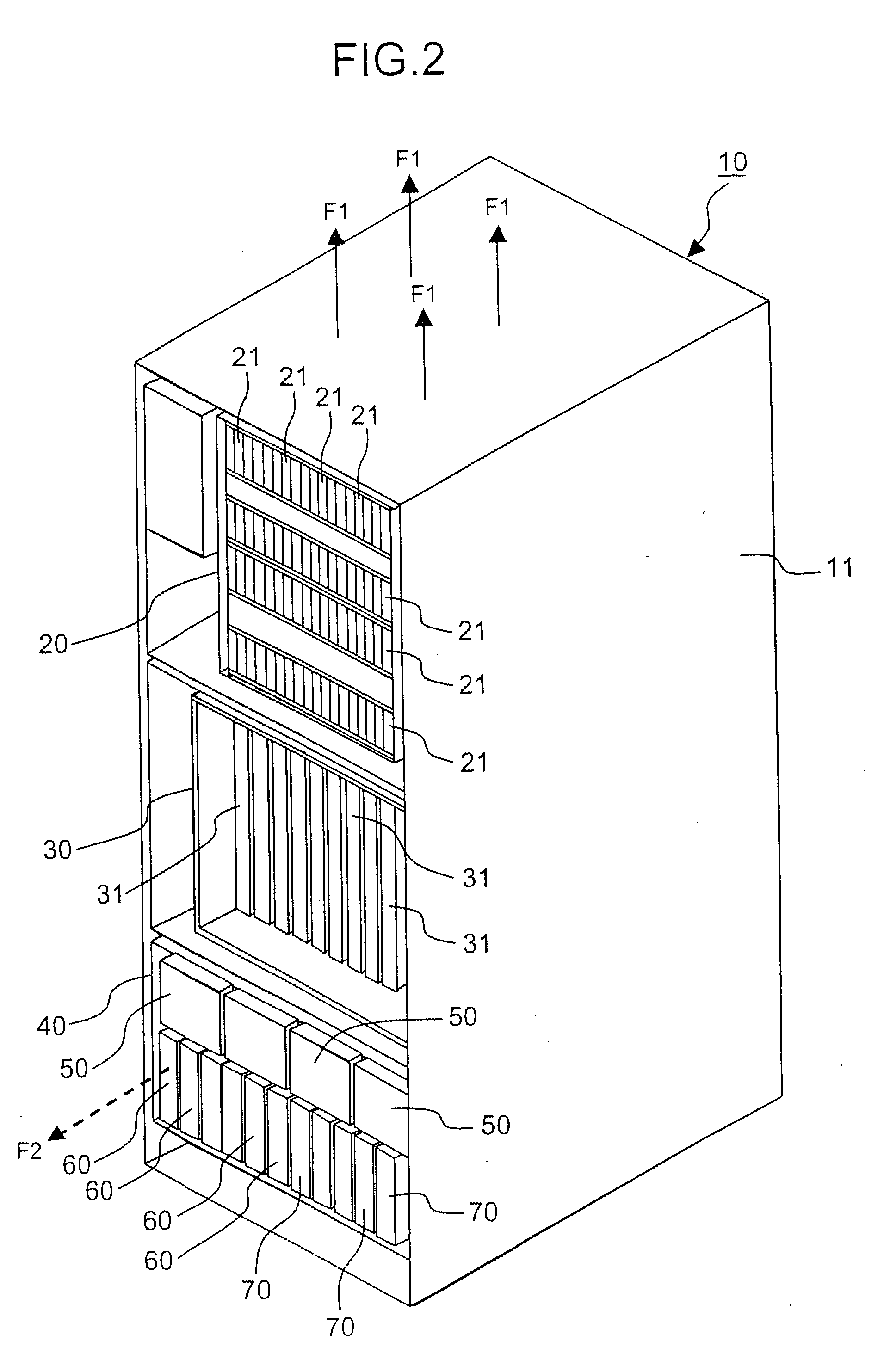

Computer rack heat extraction device

InactiveUS6412292B2More revenueExcessive coolingDucting arrangementsDigital data processing detailsAppliance componentEngineering

An air conditioning cooling apparatus and method which includes the steps of supplying cooling air generated from a cooling apparatus into an air passageway formed below a floor; guiding the cooling air within the air passageway into an equipment assembly disposed on the floor through an opening located in the floor; communicating the cooling air introduced into the equipment assembly into a plenum and introducing the air released from within the equipment into the plenum and communicating the released air through the cooling apparatus for cooling the released air. The method permits temperature differential between the air supplied to the air passageway and the air introduced into the plenum from the equipment assembly to be 45.degree. F. to substantially 40.degree. F. so as to reduce the power necessary for operating on the fan of the blowing apparatus. The equipment assembly utilizes an air flow control mechanism so as to substantially evenly distribute cooling air to the equipment.

Owner:EATON INTELLIGENT POWER LIMITED

System and method for monitoring a mobile computing product/arrangement

InactiveUS20050222801A1Input/output for user-computer interactionDevices with sensorReal-time computingMobile computing

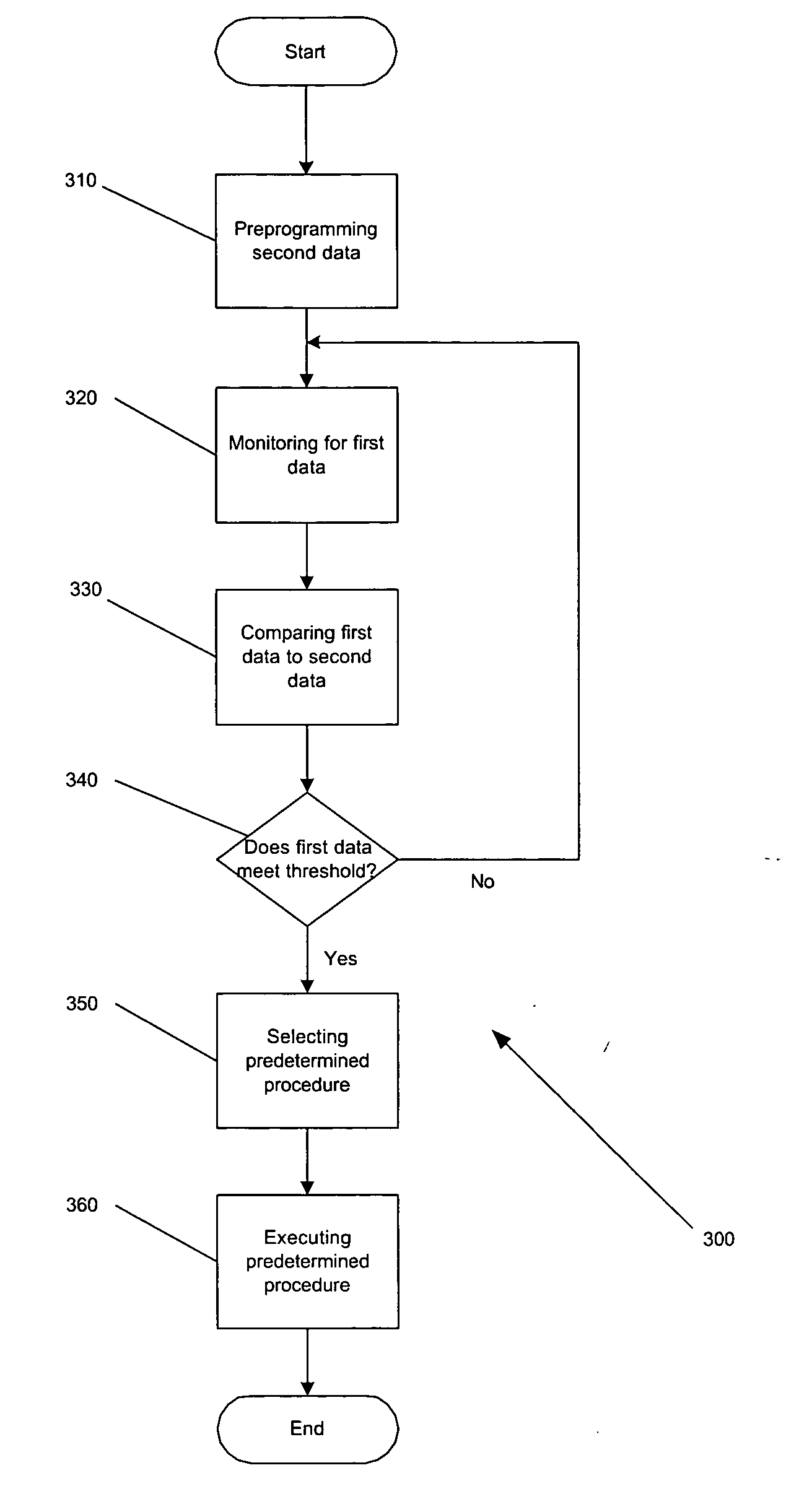

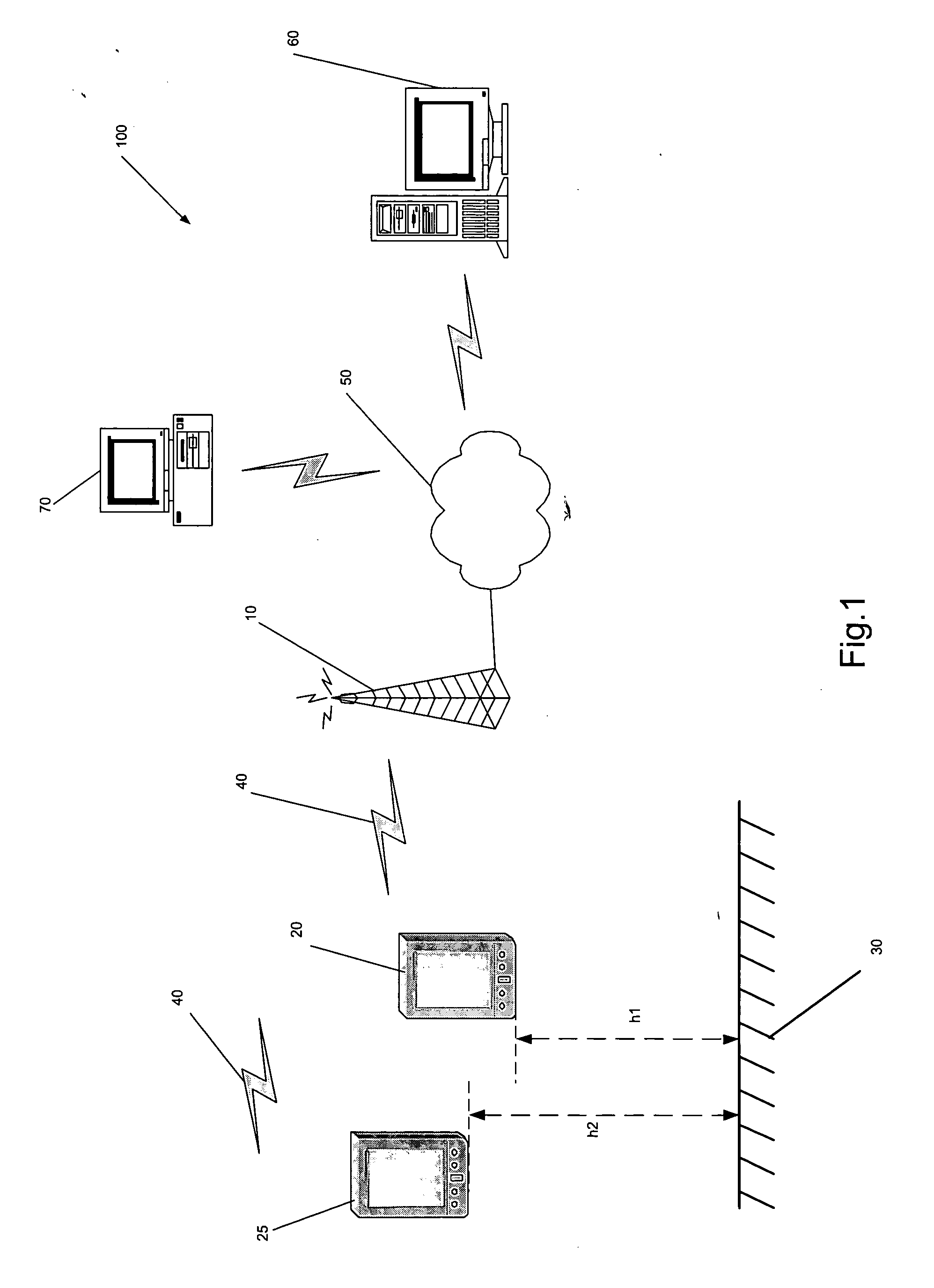

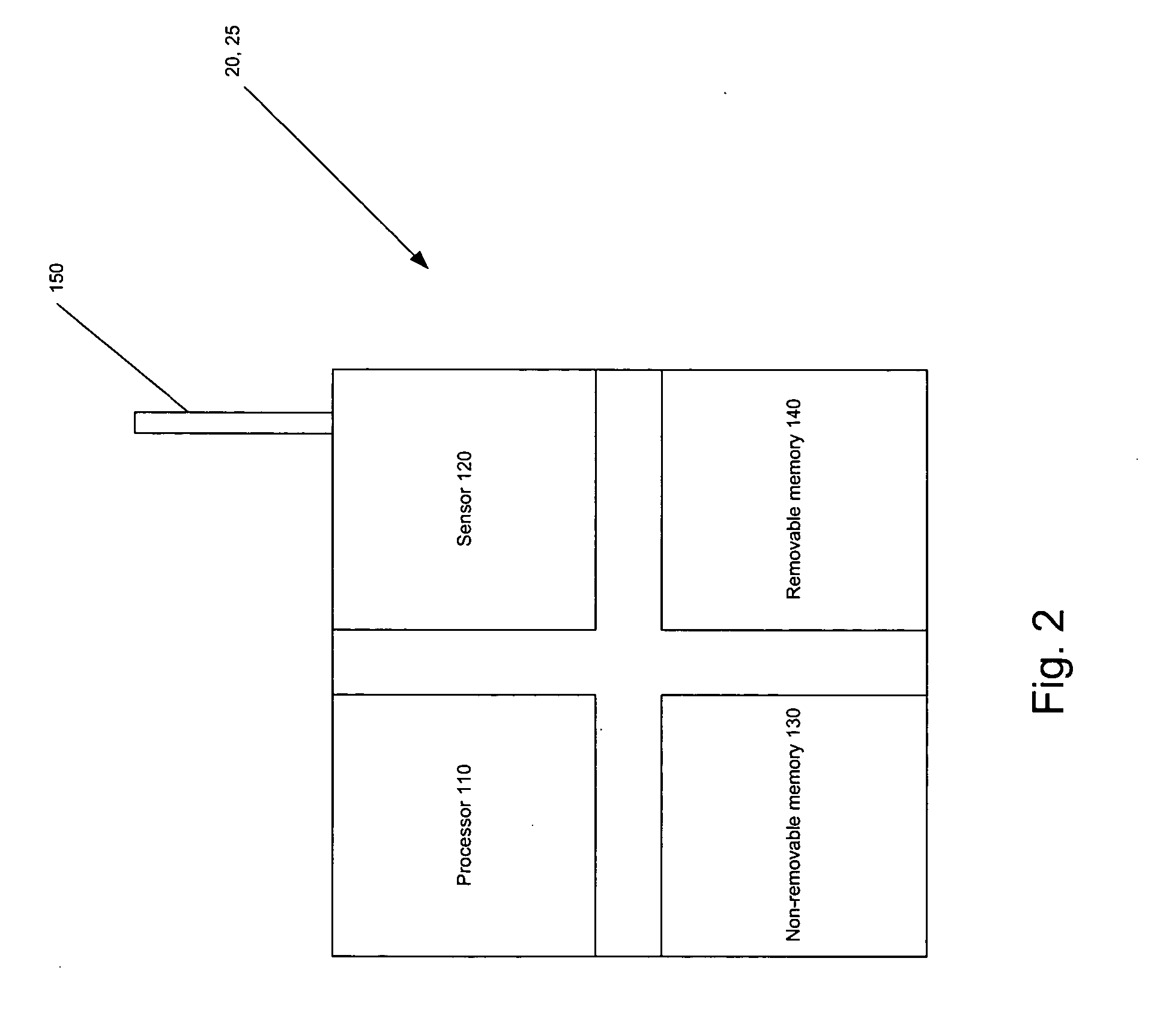

Described is a system and method for monitoring a mobile computing Arrangement. The arrangement may include a sensor and a processor. The sensor detects first data of an event including a directional orientation and a motion of the arrangement. The processor compares the first data to second data to determine if at least one predetermined procedure is to be executed. The second data may include a predetermined threshold range of changes in the directional orientation and the motion. If the predetermined procedure is to be executed, the processor selects the predetermined procedure which corresponds to the event as a function of the first data. Subsequently, the predetermined procedures is executed.

Owner:SYMBOL TECH INC

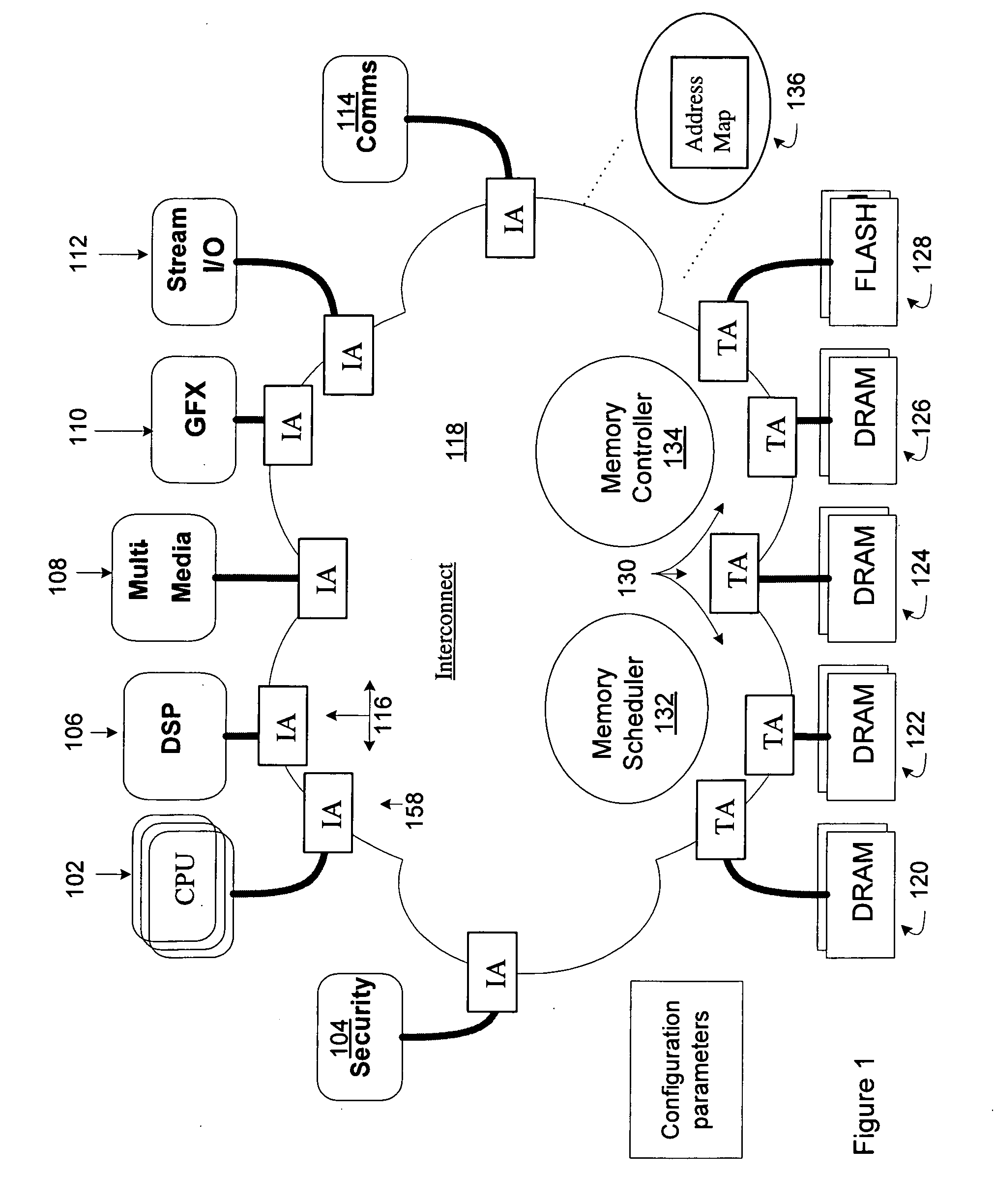

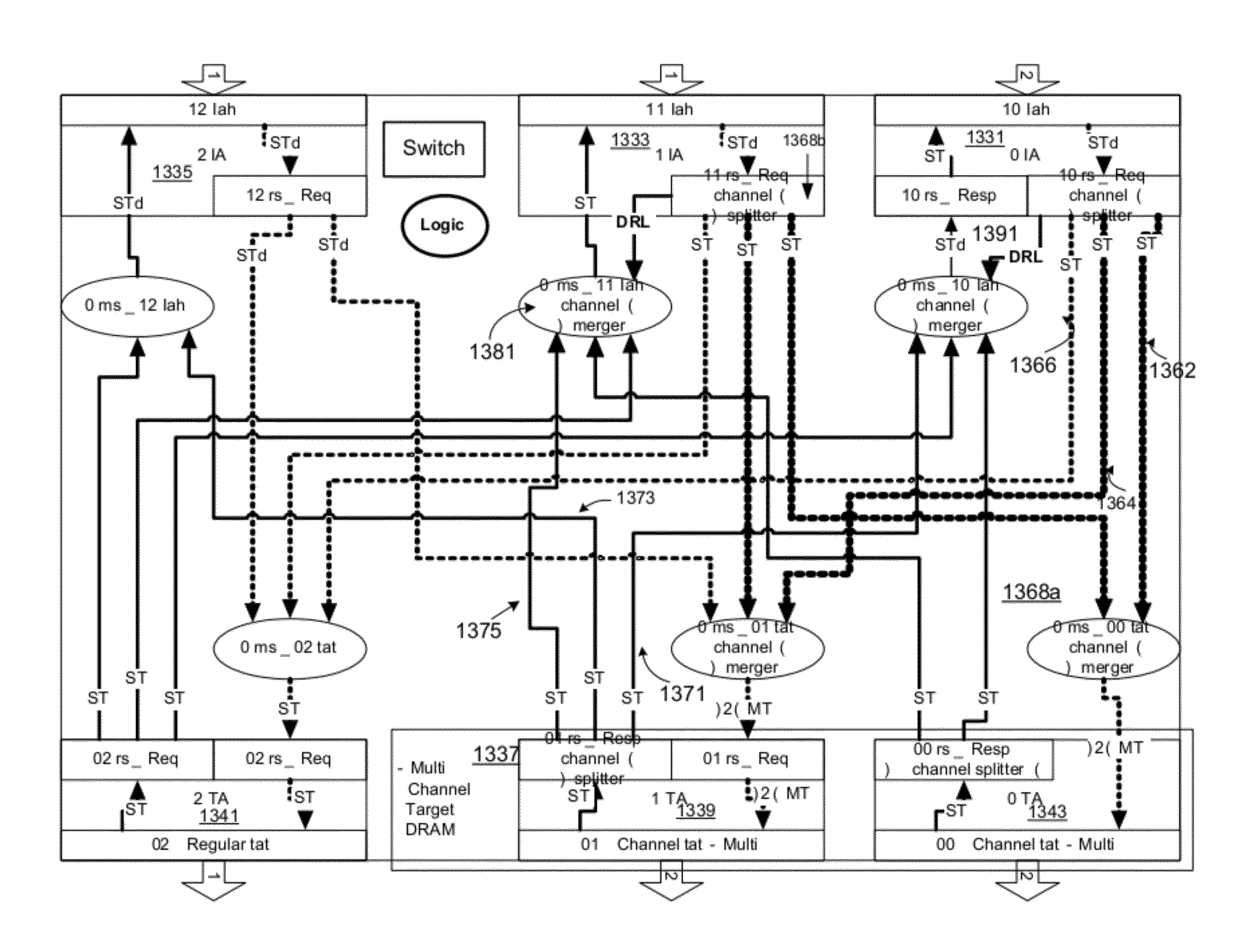

Various methods and apparatus to support outstanding requests to multiple targets while maintaining transaction ordering

ActiveUS20080320476A1Digital computer detailsMultiprogramming arrangementsIntellectual propertyOrder form

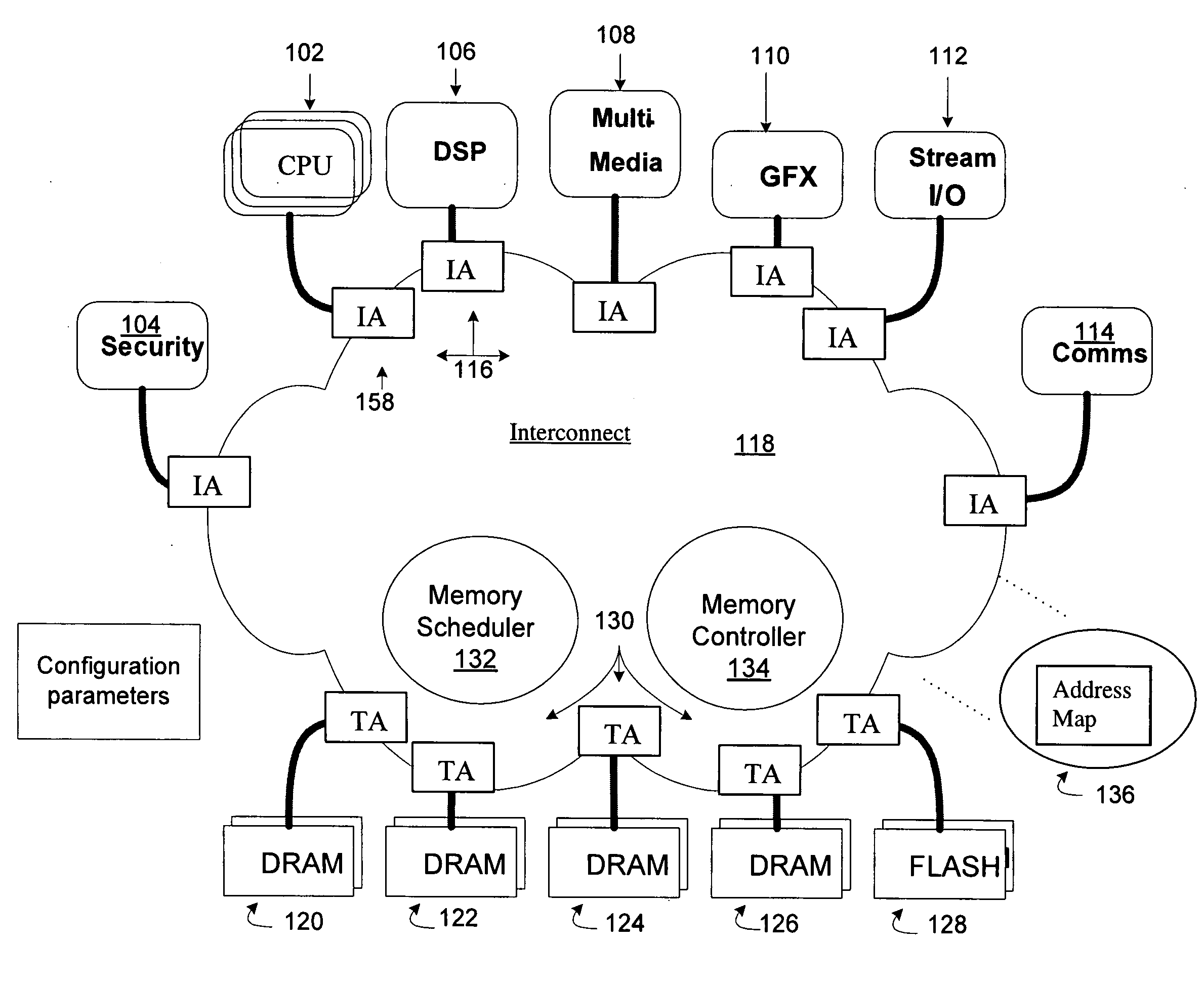

A method, apparatus, and system are described, which generally relate to an integrated circuit having an interconnect that implements internal controls. The interconnect in an integrated circuit communicates transactions between initiator Intellectual Property (IP) cores and target IP cores coupled to the interconnect. The interconnect implements logic configured to support multiple transactions issued from a first initiator IP core to the multiple target IP cores while maintaining an expected execution order within the transactions. The logic supports a second transaction to be issued from the first initiator IP core to a second target IP core before a first transaction issued from the same first initiator IP core to a first target IP core has completed while ensuring that the first transaction completes before the second transaction and while ensuring an expected execution order within the first transaction and second transaction are maintained. The logic does not include any reorder buffering.

Owner:META PLATFORMS TECH LLC

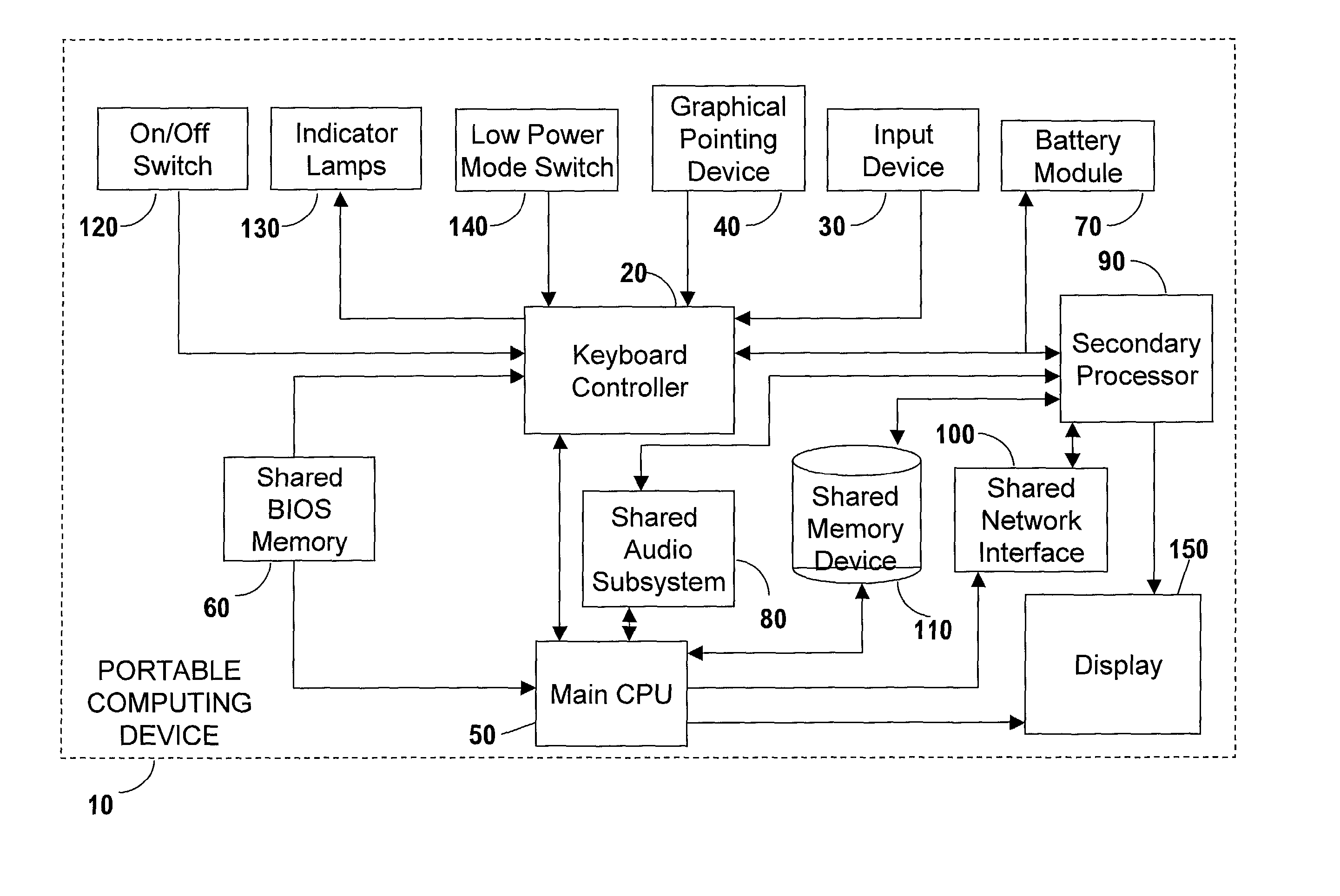

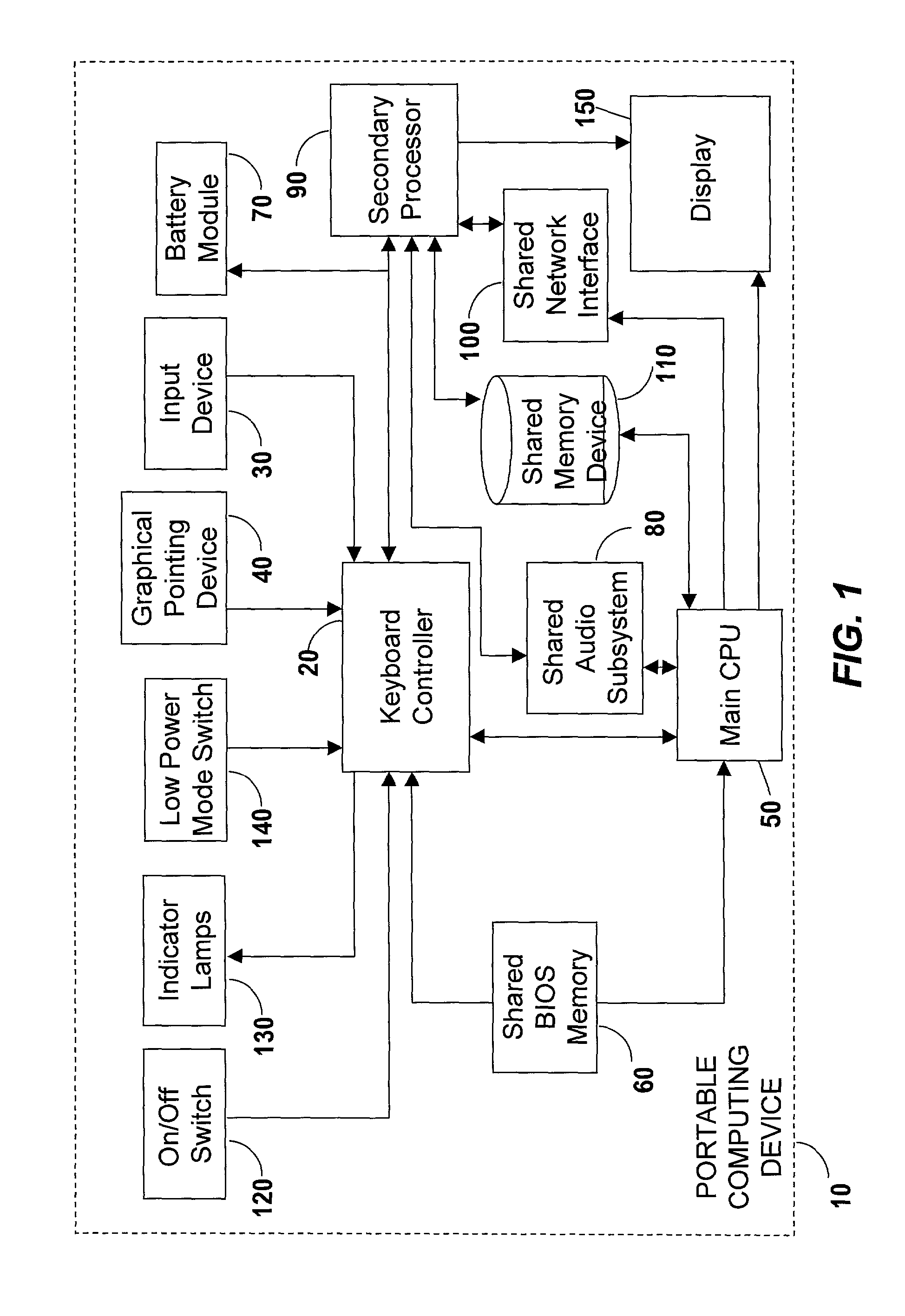

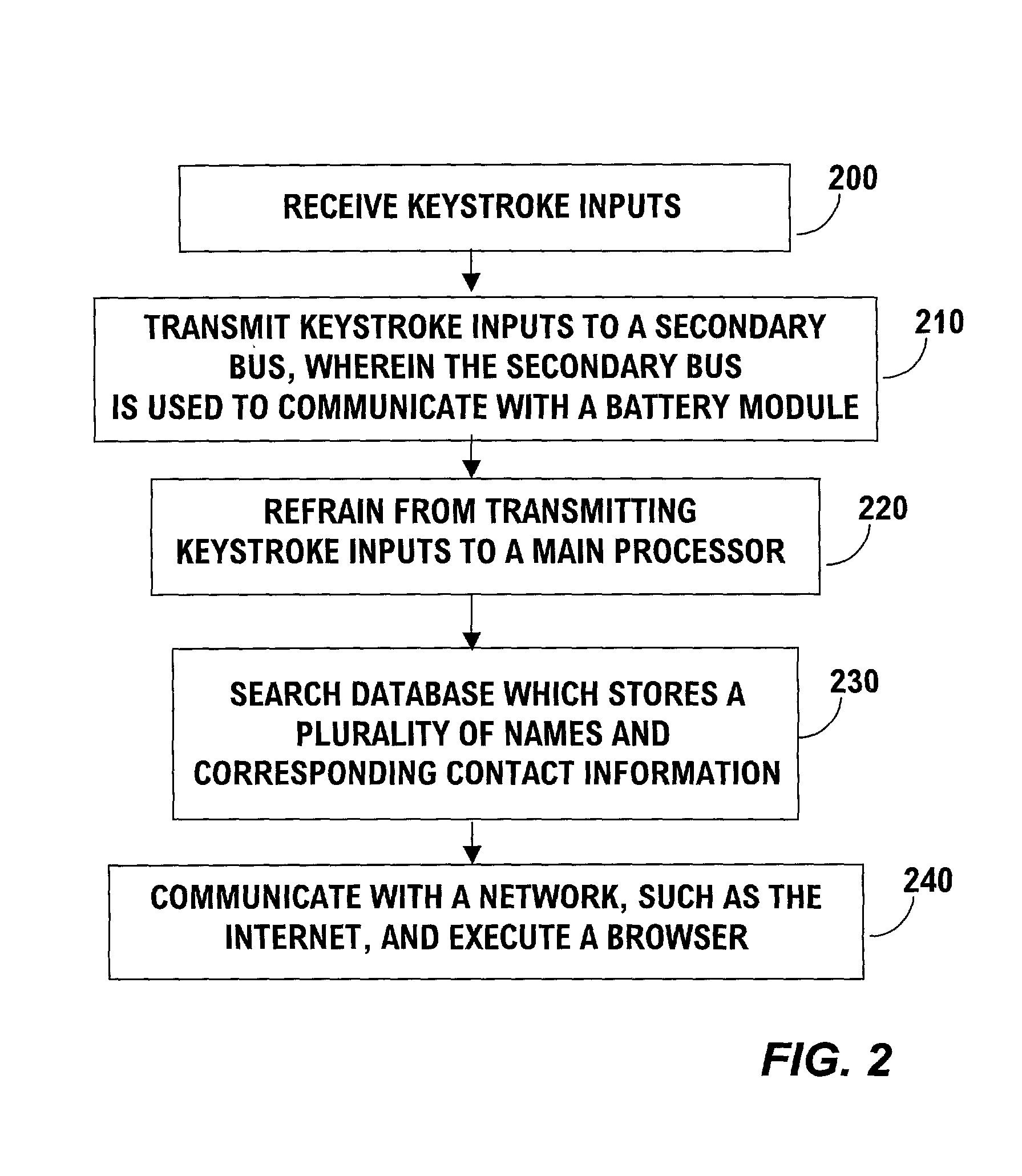

Computing device having a low power secondary processor coupled to a keyboard controller

InactiveUS20020129288A1Easy to implementSusbset functionality useVolume/mass flow measurementPower modeGraphics

This abstract has been included pursuant to Section 1.72(b) of the Rules for Patent and Trademark Cases, Title 37 of the Code of Federal Regulations. This abstract is intended only to enable the Patent and Trademark Office and the public to generally determine the nature of the technical disclosure. This abstract is not intended to aid in the interpretation of the scope of any claim. A portable computing device includes a keyboard controller that receives keystroke information as well as inputs from a graphical pointing device and conveys these to a main central processing unit. The keyboard controller additionally communicates with a battery module through a second interface in order to monitor and control the charging of the module. A low power secondary processor is interfaced to the keyboard controller through the second interface in order to receive keystroke information as well as information from the graphical pointing device. When the keyboard controller is instructed to do so, keystroke and graphical pointing information are conveyed exclusively to the secondary processor, thereby enabling the portable computing device to perform some functions without requiring the main central processing unit to be operational and thus operate in a low power mode.

Owner:HEWLETT PACKARD DEV CO LP

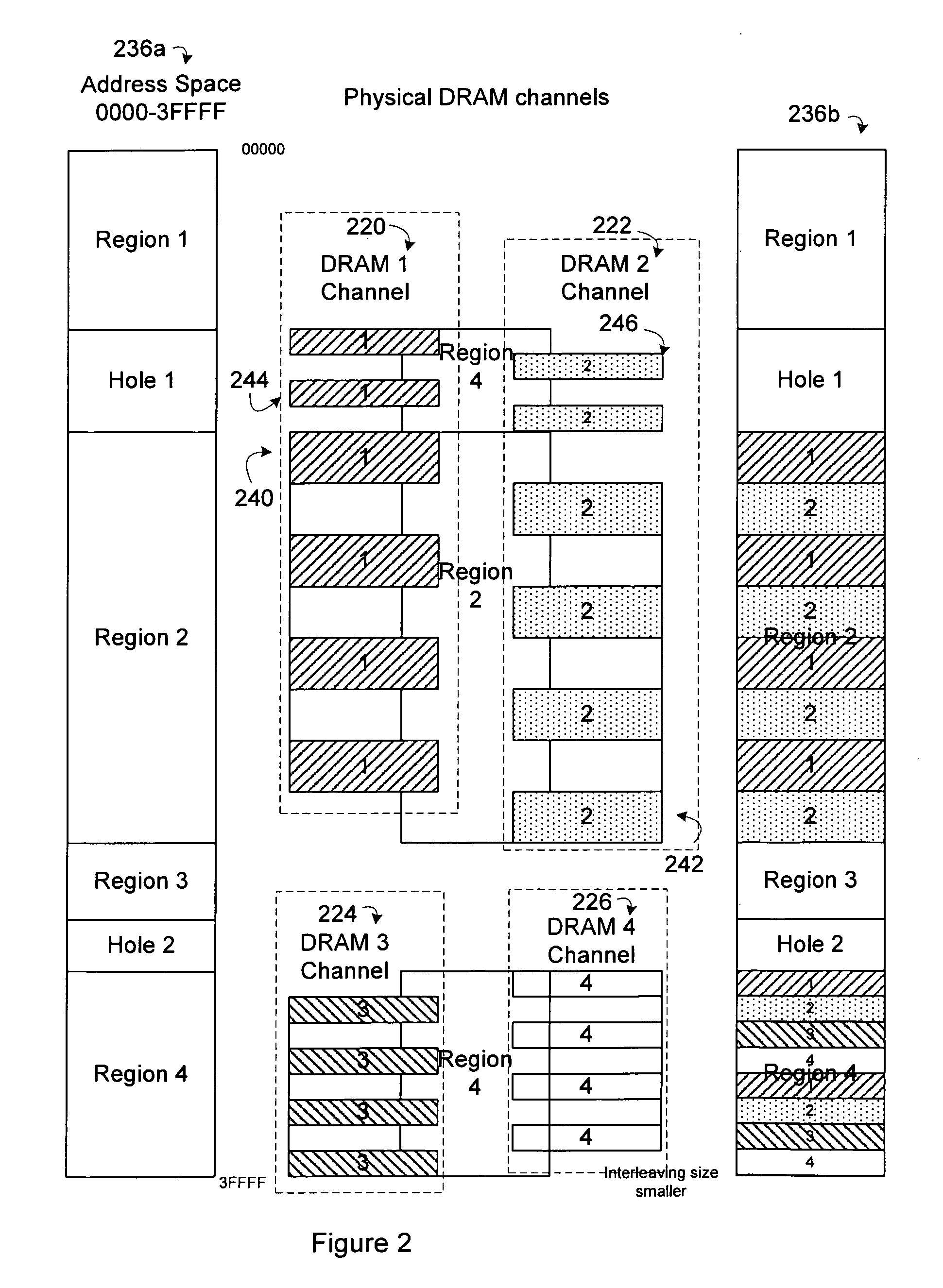

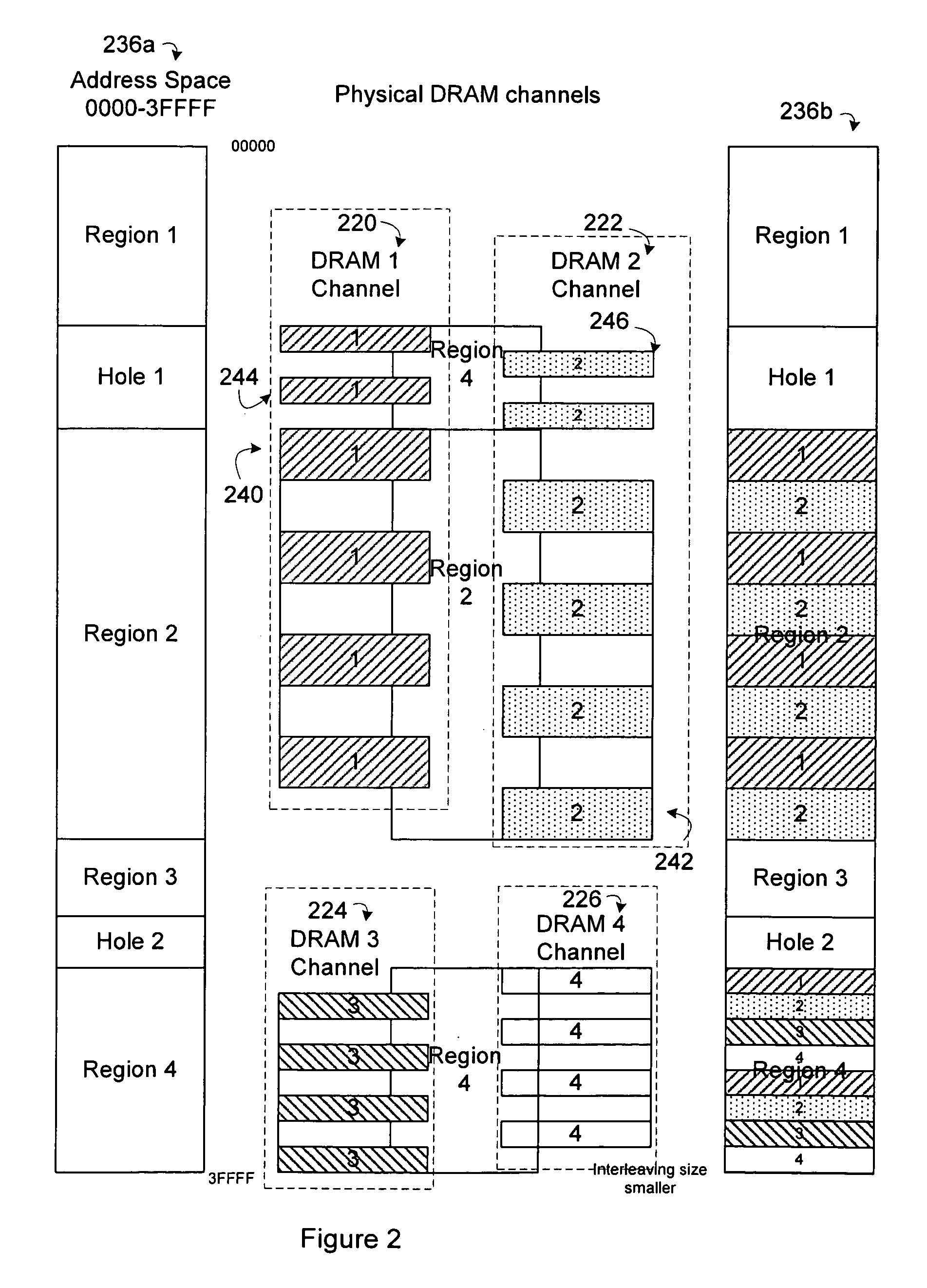

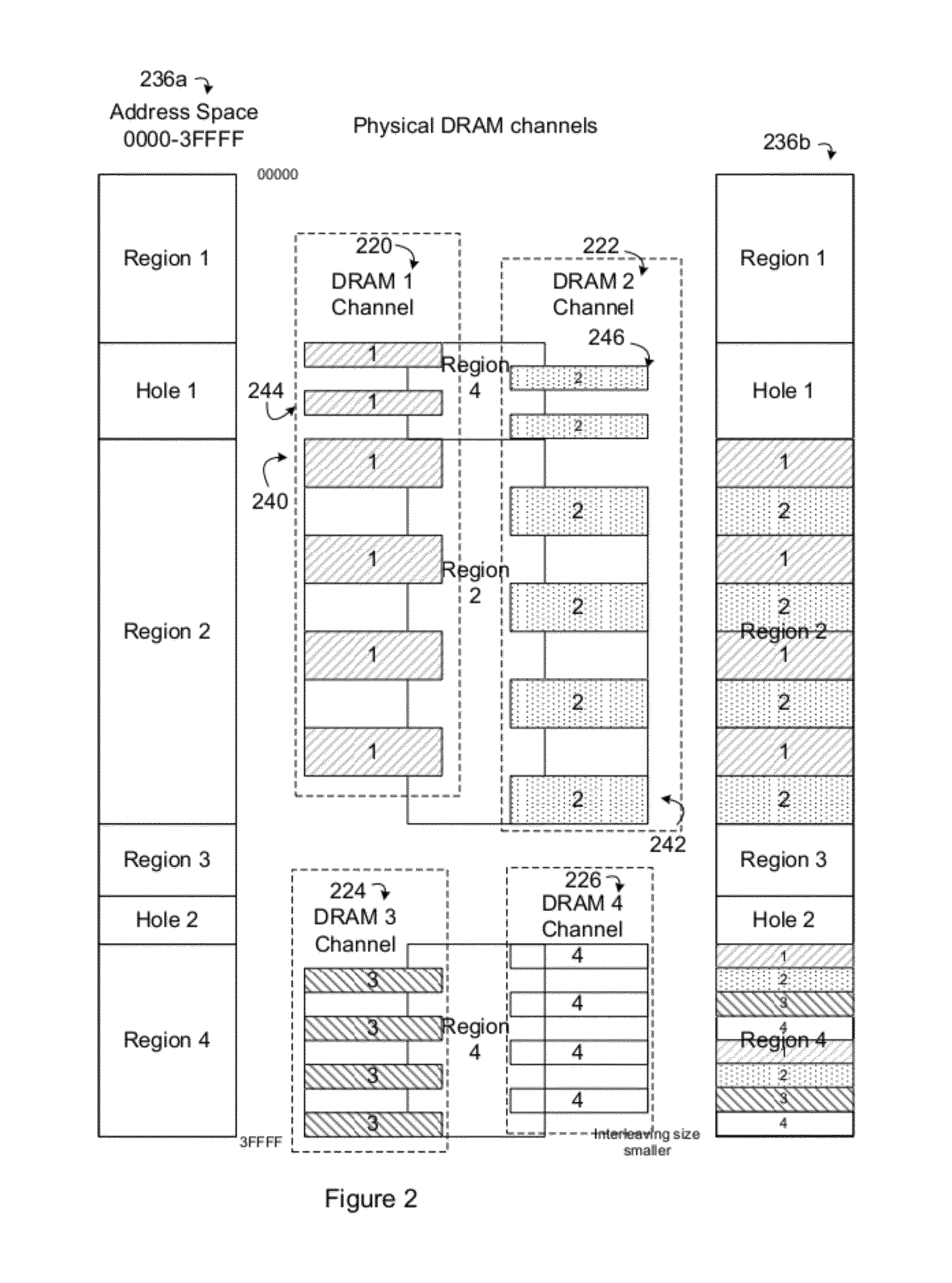

Various methods and apparatus to support transactions whose data address sequence within that transaction crosses an interleaved channel address boundary

ActiveUS20080320254A1Memory adressing/allocation/relocationDigital computer detailsEmbedded systemAddress space

A method, apparatus, and system are described, which generally relate to an interconnect routing transactions to target IP cores, including two or more channels making up a first aggregate target. The two or more channels populate an address space assigned to the first aggregate target and appear as a single target to the initiator IP cores. The interconnect implements chopping logic to chop an individual transaction from a first initiator IP core whose address sequence crosses a channel address boundary from a first channel to a second channel within the first aggregate target into two or more burst transactions. A first chopped burst transaction is chopped to fit within the address boundaries of the first channel and a second chopped burst transaction is chopped to fit within the address boundaries of the second channel.

Owner:META PLATFORMS TECH LLC

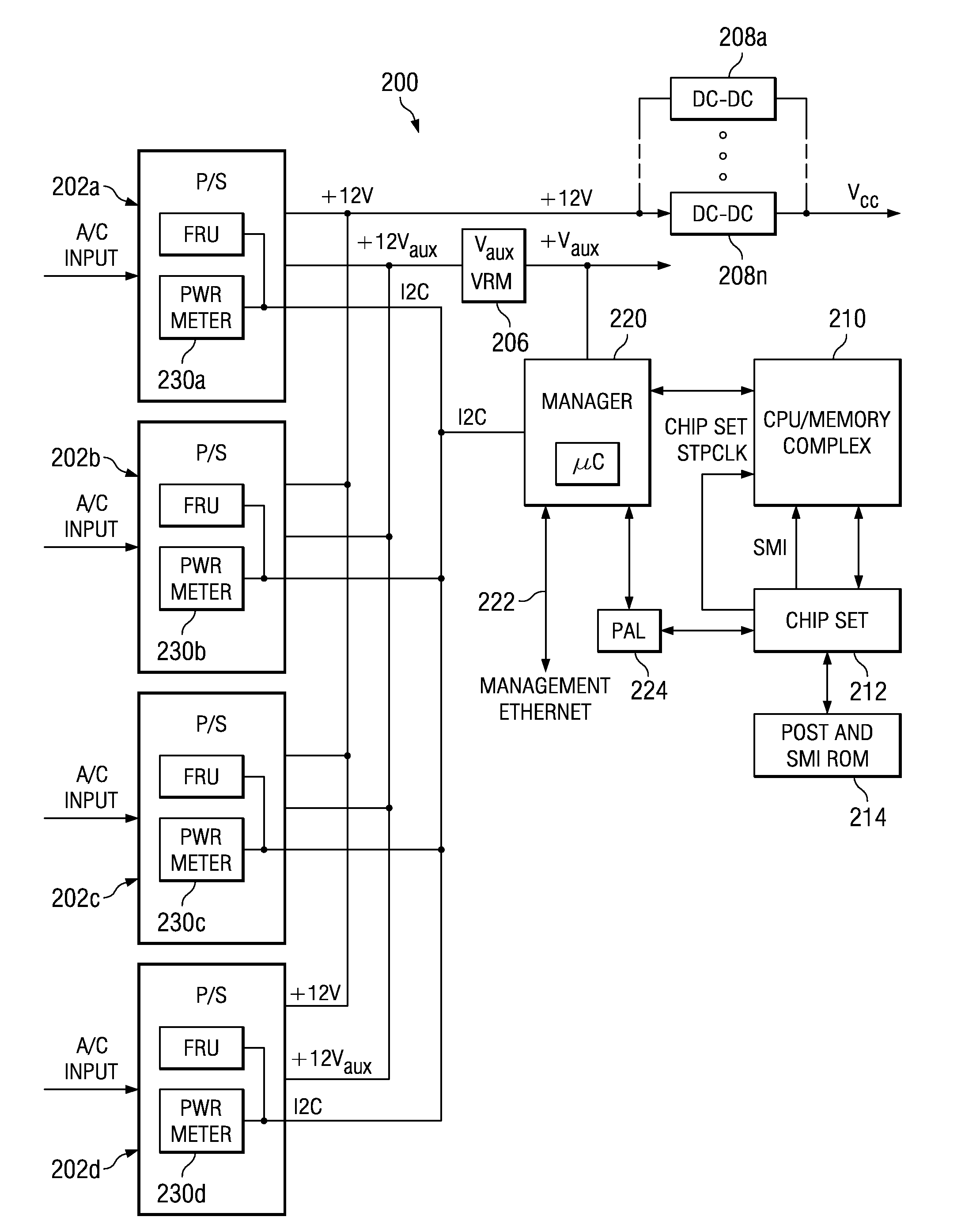

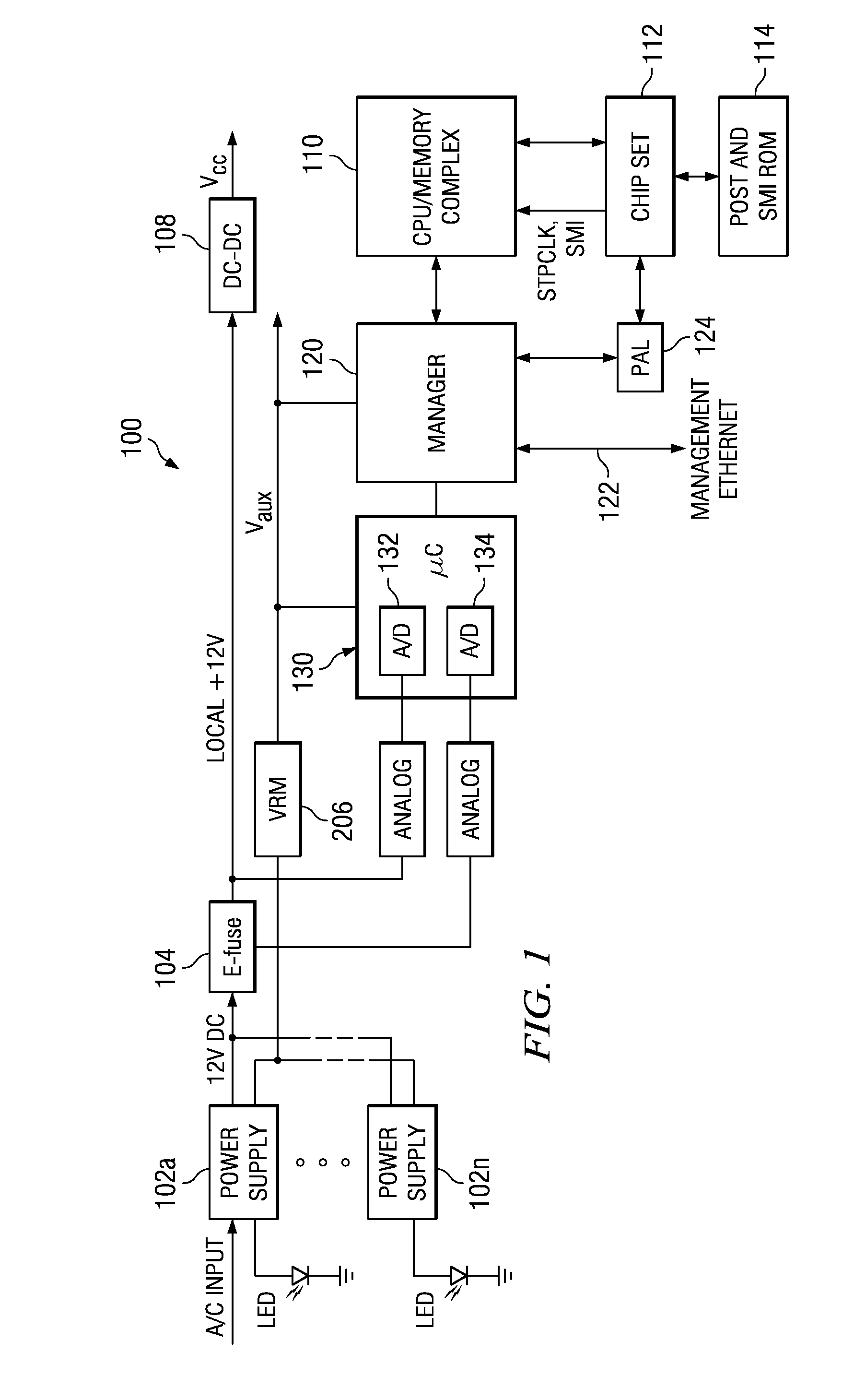

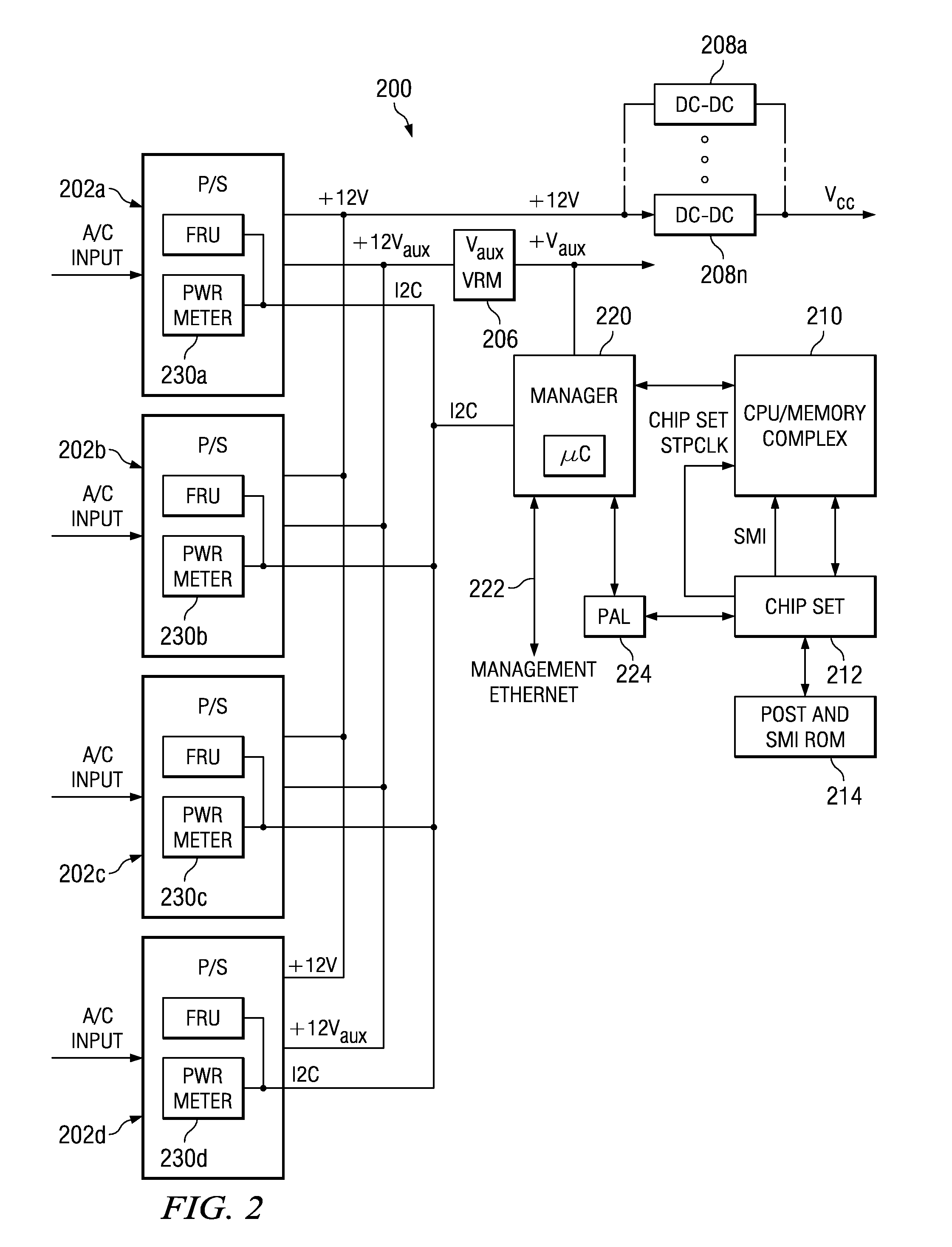

Dynamic Converter Control for Efficient Operation

ActiveUS20080320322A1Electric signal transmission systemsBatteries circuit arrangementsDynamic managementPower consumption

Dynamically managing power consumption in a computer system having at least two parallel power converters in order to improve efficiency. A maximum power capacity for each of the power converters is determined and then power consumption of the computer system is monitored. If the power consumption of the computer system can be provided by less than all of the parallel power converters then one or more of the power converters is turned off, such that a reduced number of parallel power converters remains turned on. A reduced maximum power capacity of the reduced number of parallel power converters is determined and a power cap value is set for the computer system that is less than or equal to the reduced maximum power capacity. The computer system is throttled at the power cap to prevent power consumption of the computer system from exceeding the power cap value.

Owner:VALTRUS INNOVATIONS LTD

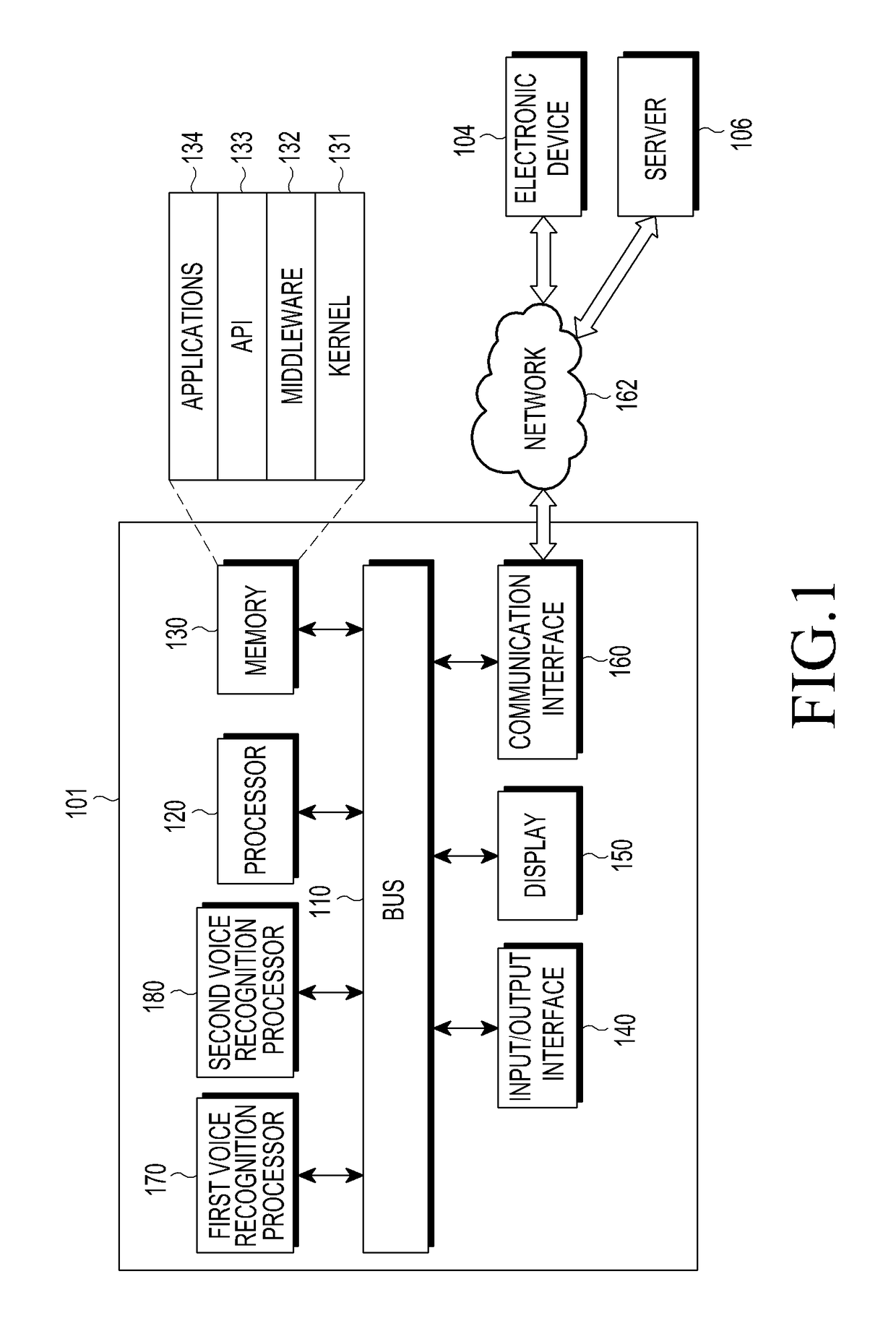

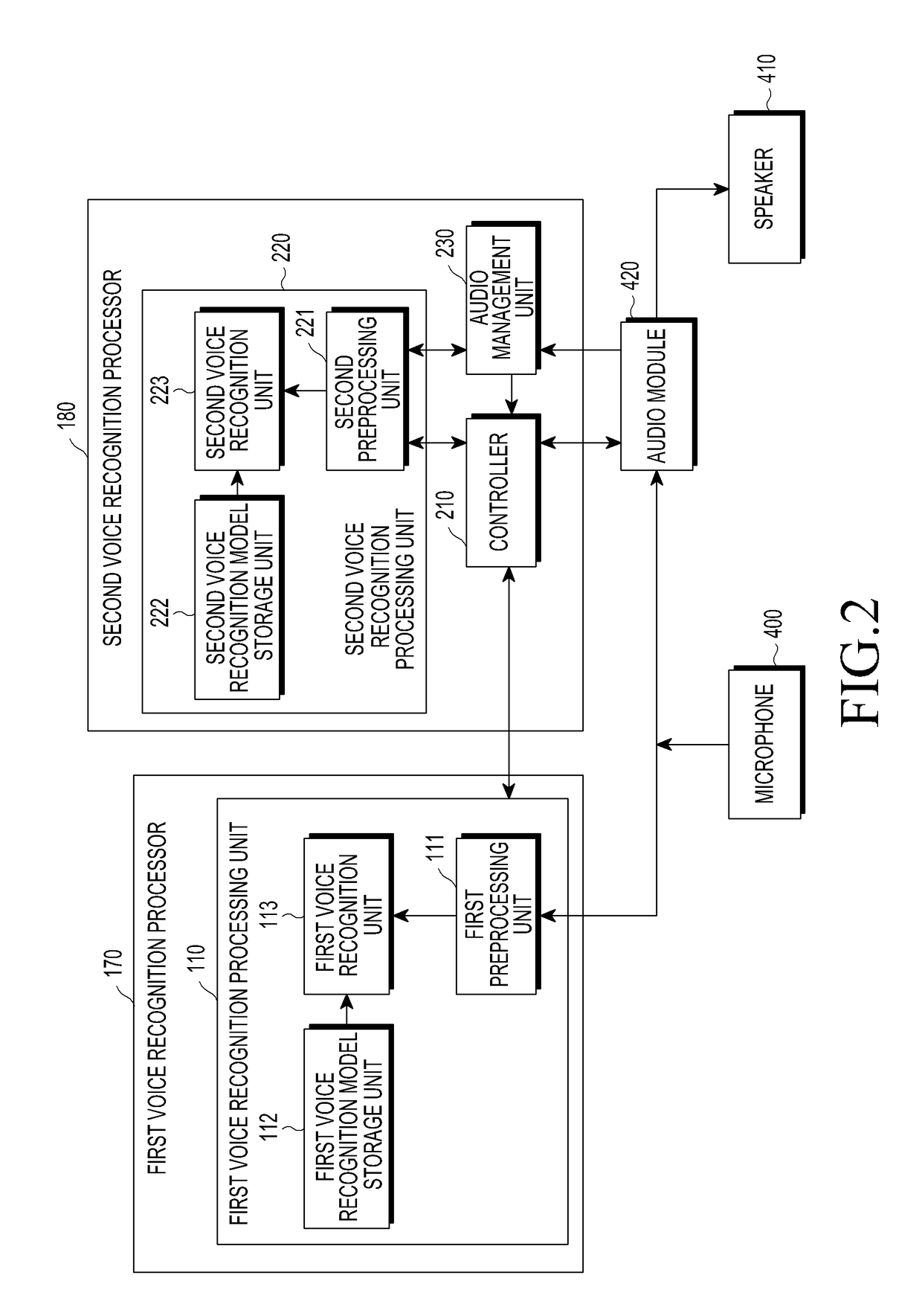

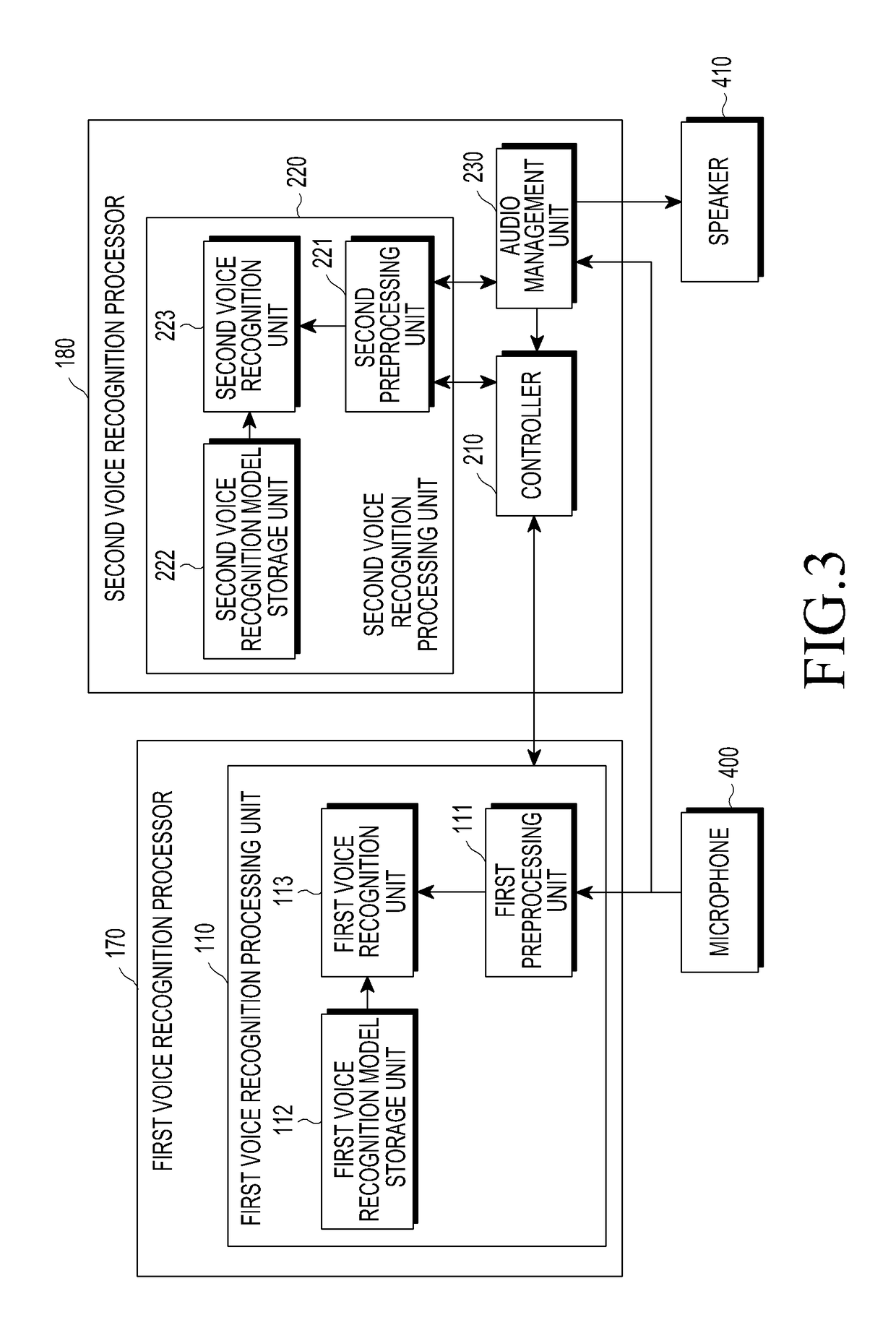

Electronic device and method for voice recognition using a plurality of voice recognition engines

ActiveUS10192557B2Reduce power consumptionHigh performance voice recognitionDigital data processing detailsSpeech recognitionIdentification deviceSpeech sound

Owner:SAMSUNG ELECTRONICS CO LTD

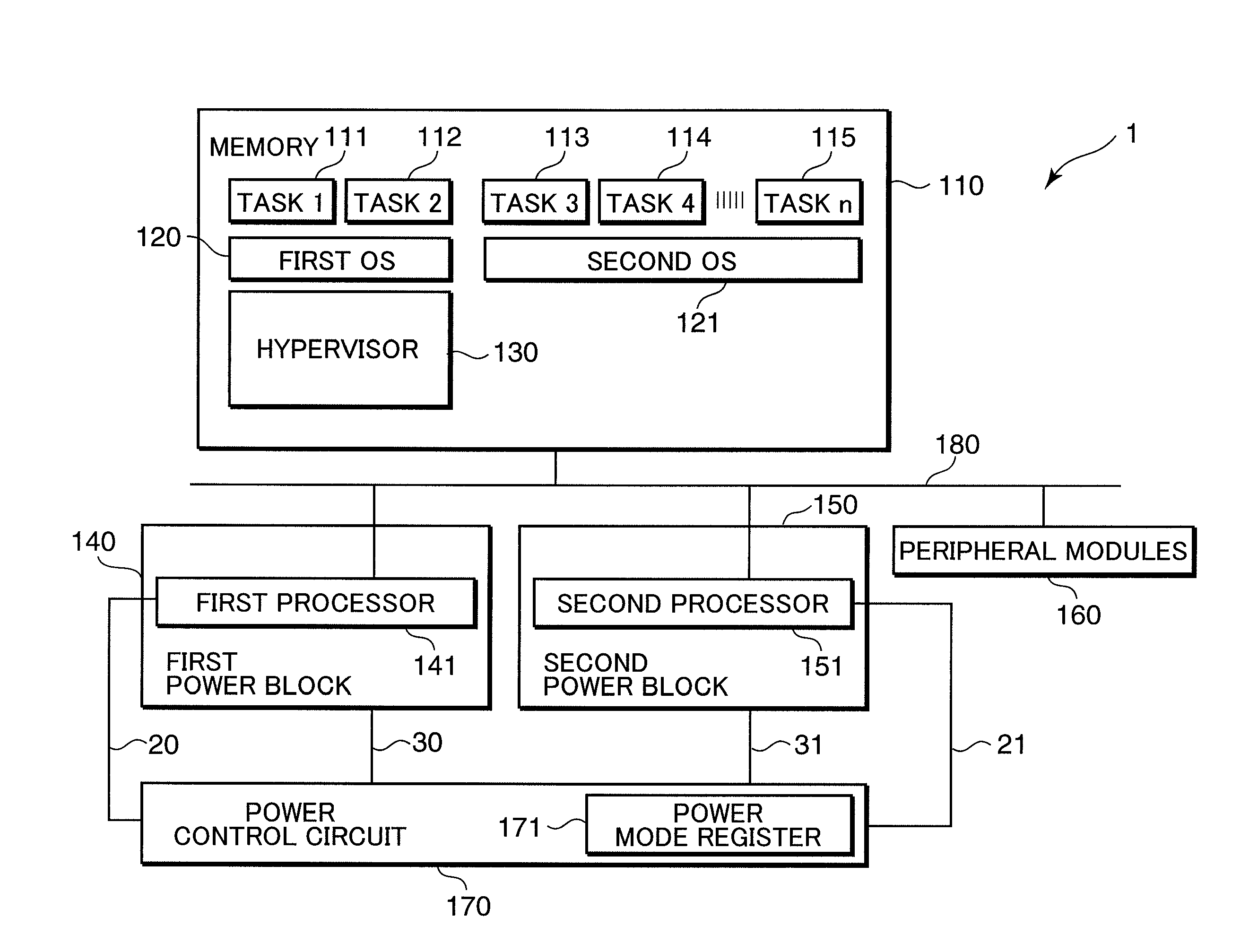

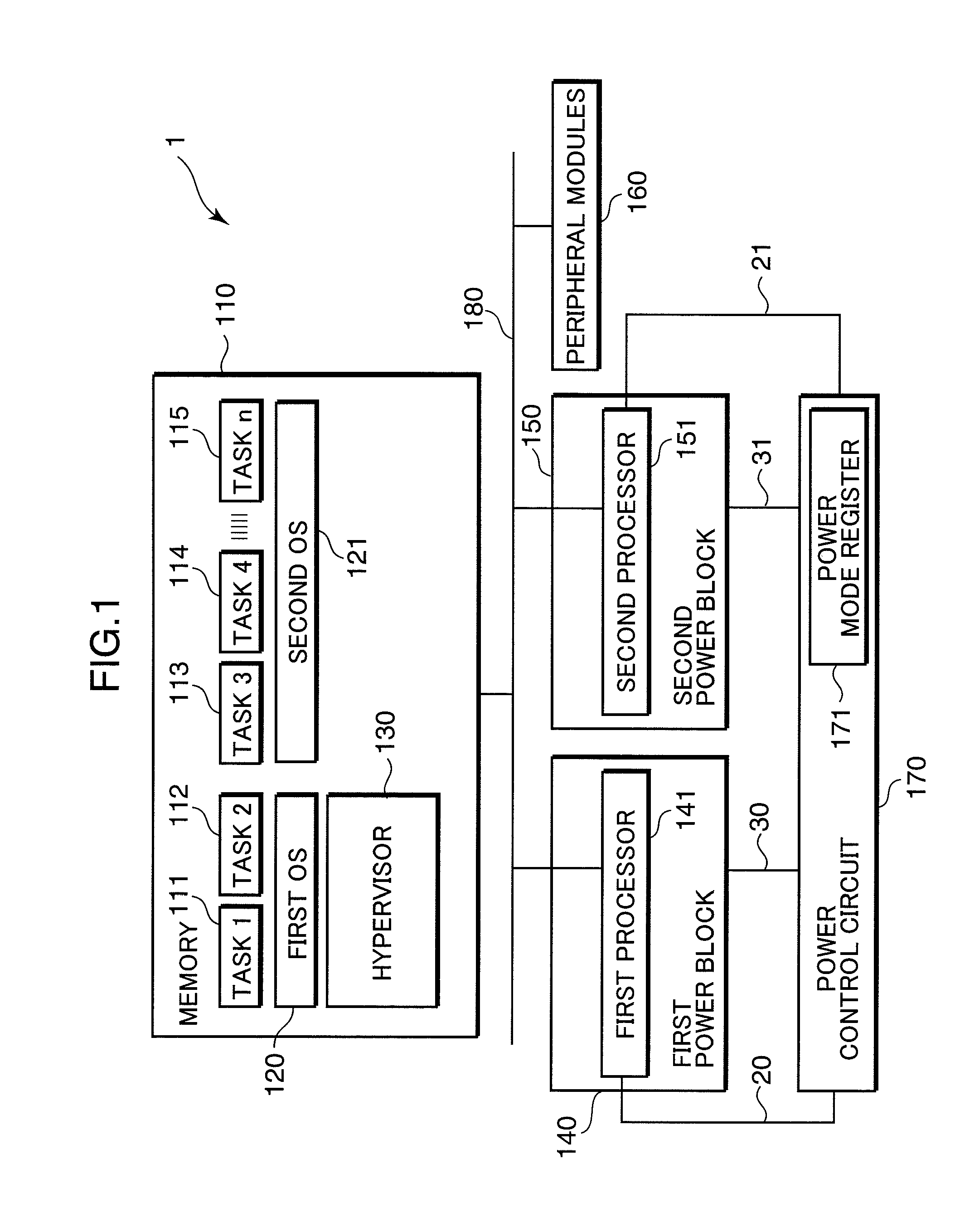

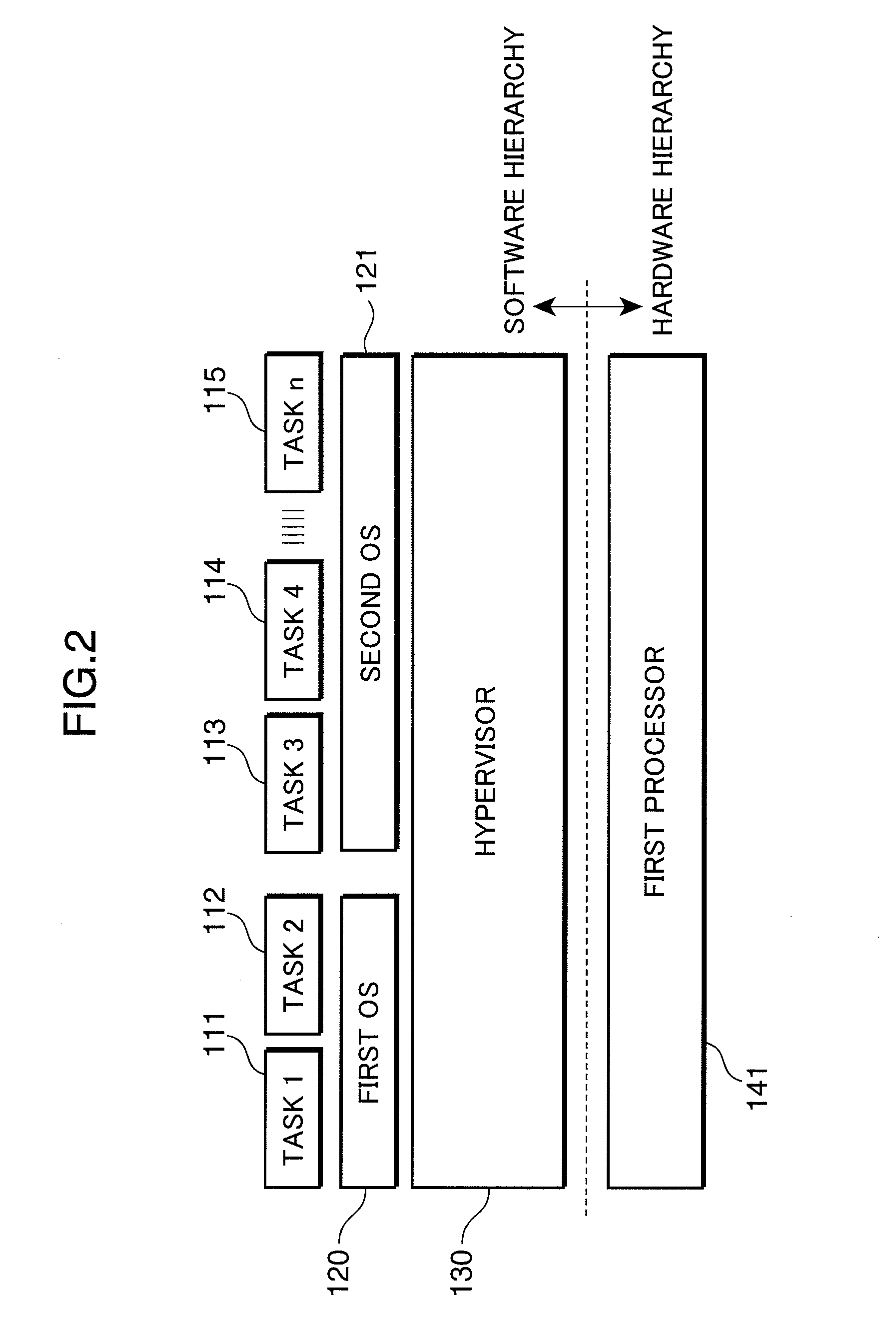

Multiprocessor control apparatus, multiprocessor control method, and multiprocessor control circuit

ActiveUS20100185833A1Reduce power consumptionReduce the number of timesMemory architecture accessing/allocationSusbset functionality useMulti processorParallel computing

An object of the invention is to reduce the electric power consumption resulting from temporarily activating a processor requiring a large electric power consumption, out of a plurality of processors. A multiprocessor system (1) includes: a first processor (141) which executes a first instruction code; a second processor (151) which executes a second instruction code, a hypervisor (130) which converts the second instruction code into an instruction code executable by the first processor (141); and a power control circuit (170) which controls the operation of at least one of the first processor (141) and the second processor (151). When the operation of the second processor (151) is suppressed by the power control circuit (170), the hypervisor (130) converts the second instruction code into the instruction code executable by the first processor (141), and the first processor (141) executes the converted instruction code.

Owner:GK BRIDGE 1

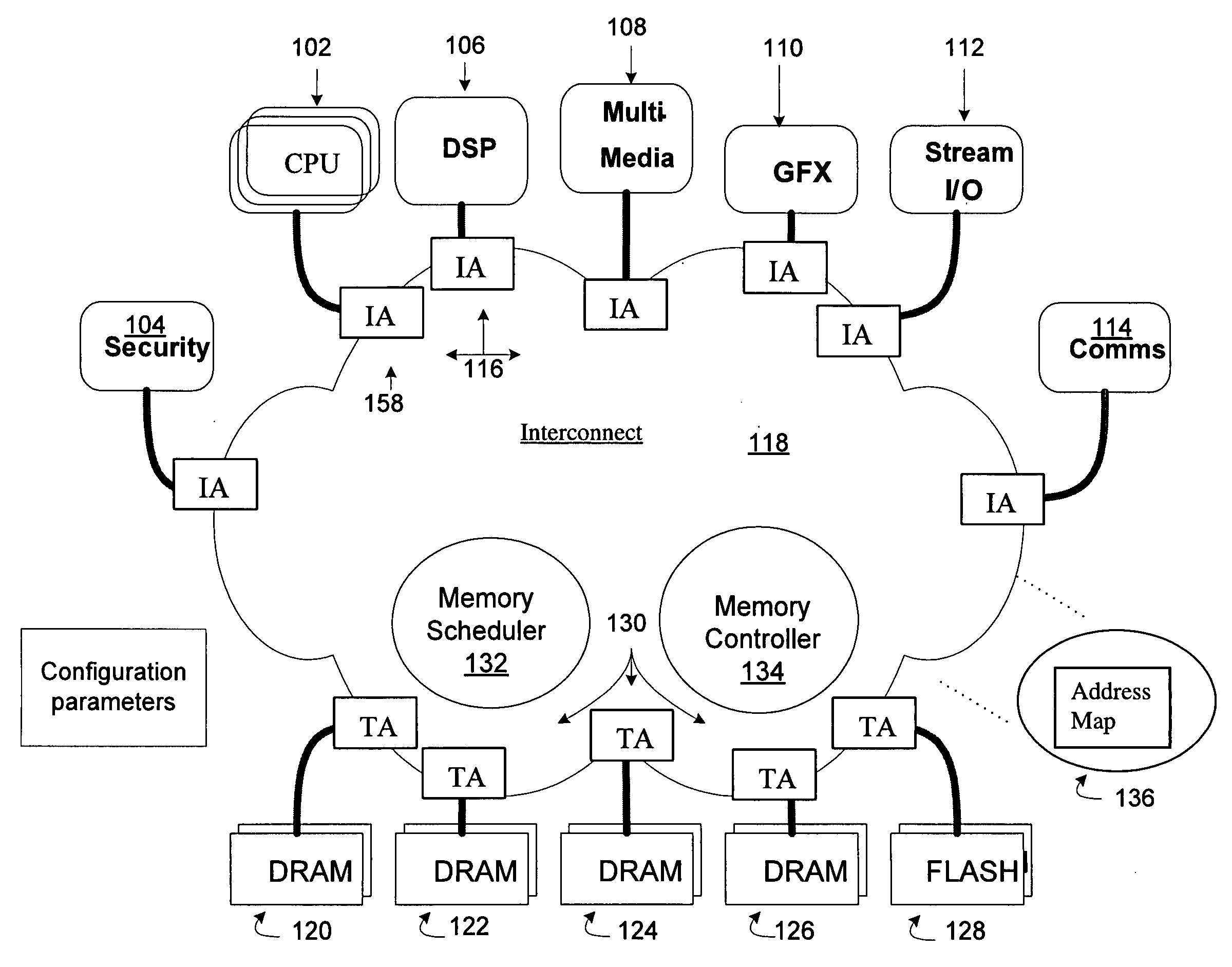

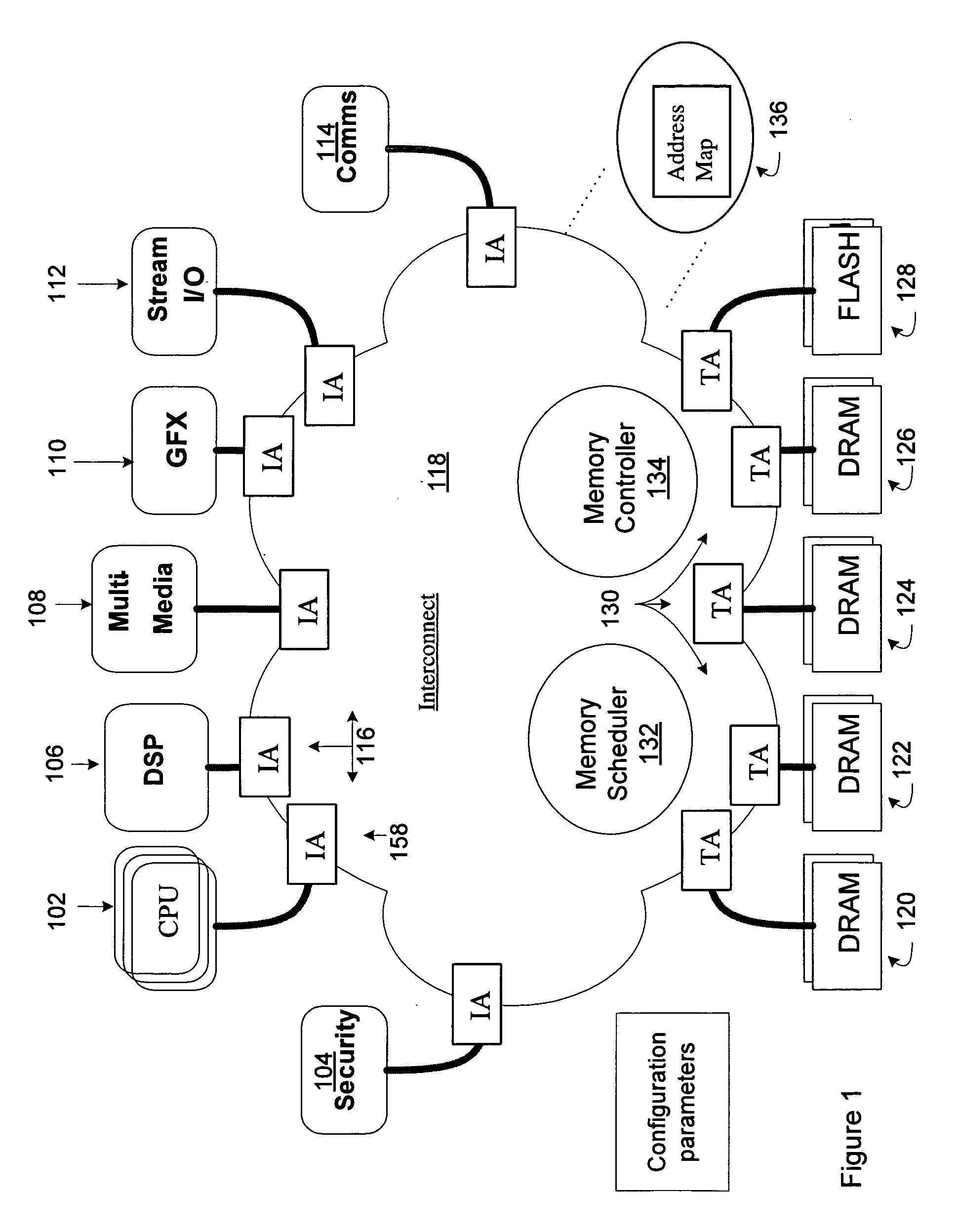

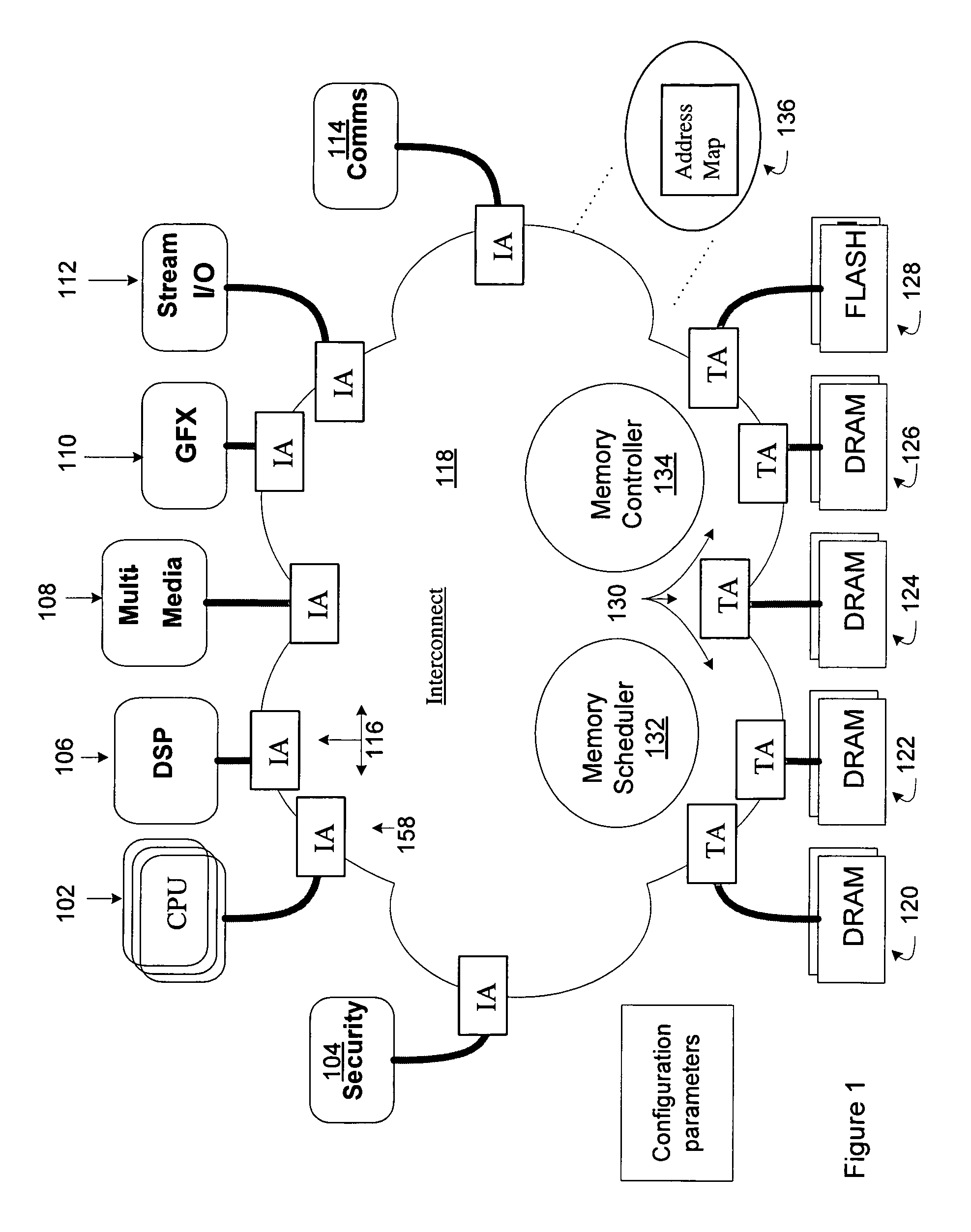

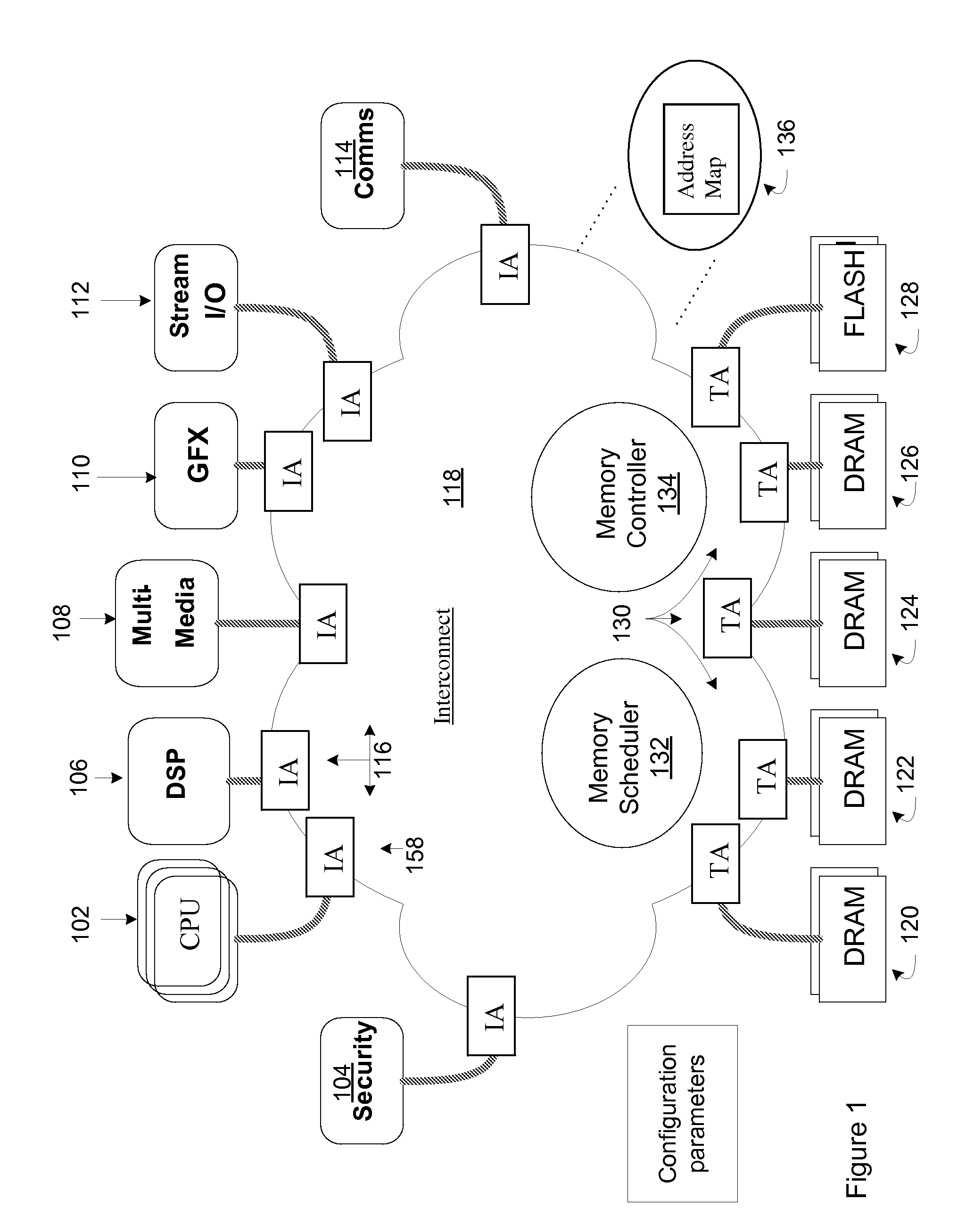

Interconnect implementing internal controls

ActiveUS20080320268A1Memory adressing/allocation/relocationDigital computer detailsIntellectual propertyParallel computing

In an embodiment, an interconnect for an integrated circuit communicates transactions between one or more initiator Intellectual Property (IP) cores and multiple target IP cores coupled to the interconnect. Two or more memory channels make up a first aggregate target of the target IP cores. The two or more memory channels populate an address space assigned to the first aggregate target and appear as a single target to the initiator IP cores. The interconnect implements chopping logic to chop individual two-dimensional (2D) transactions that cross the memory channel address boundaries from a first memory channel to a second memory channel within the first aggregate target into two or more 2D transactions with a height value greater than one, as well as stride and width dimensions, which are chopped to fit within memory channel address boundaries of the first aggregate target.

Owner:META PLATFORMS TECH LLC

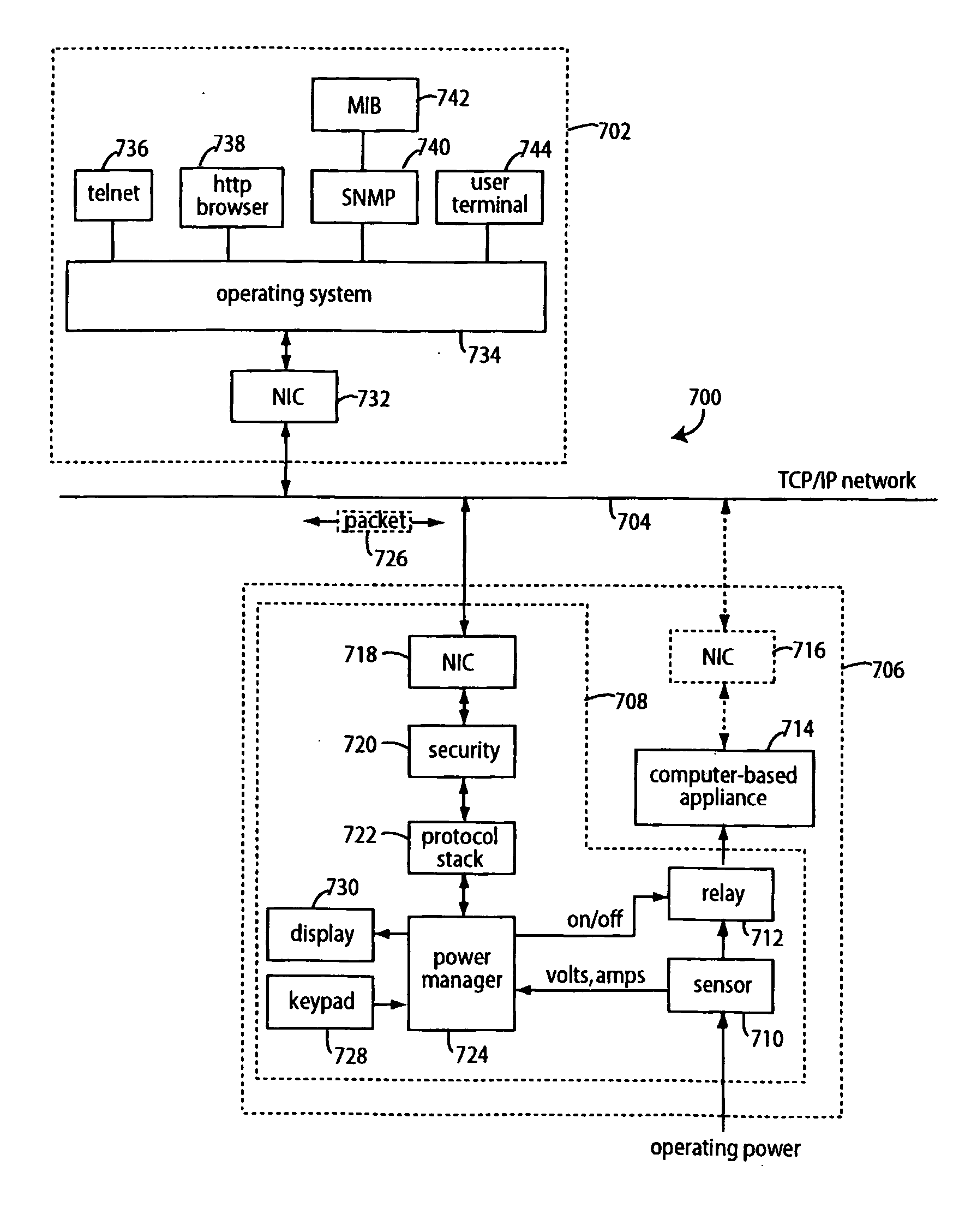

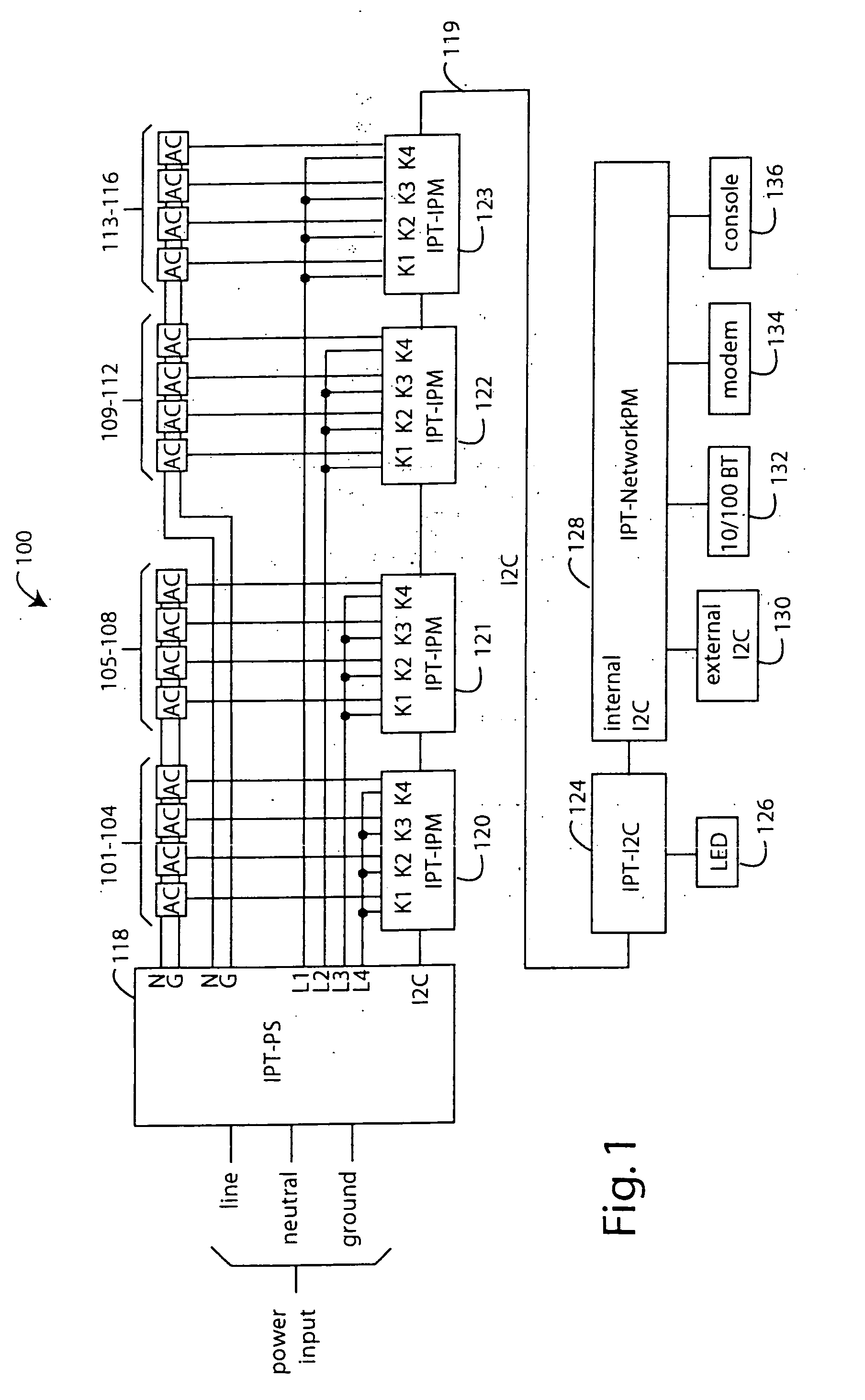

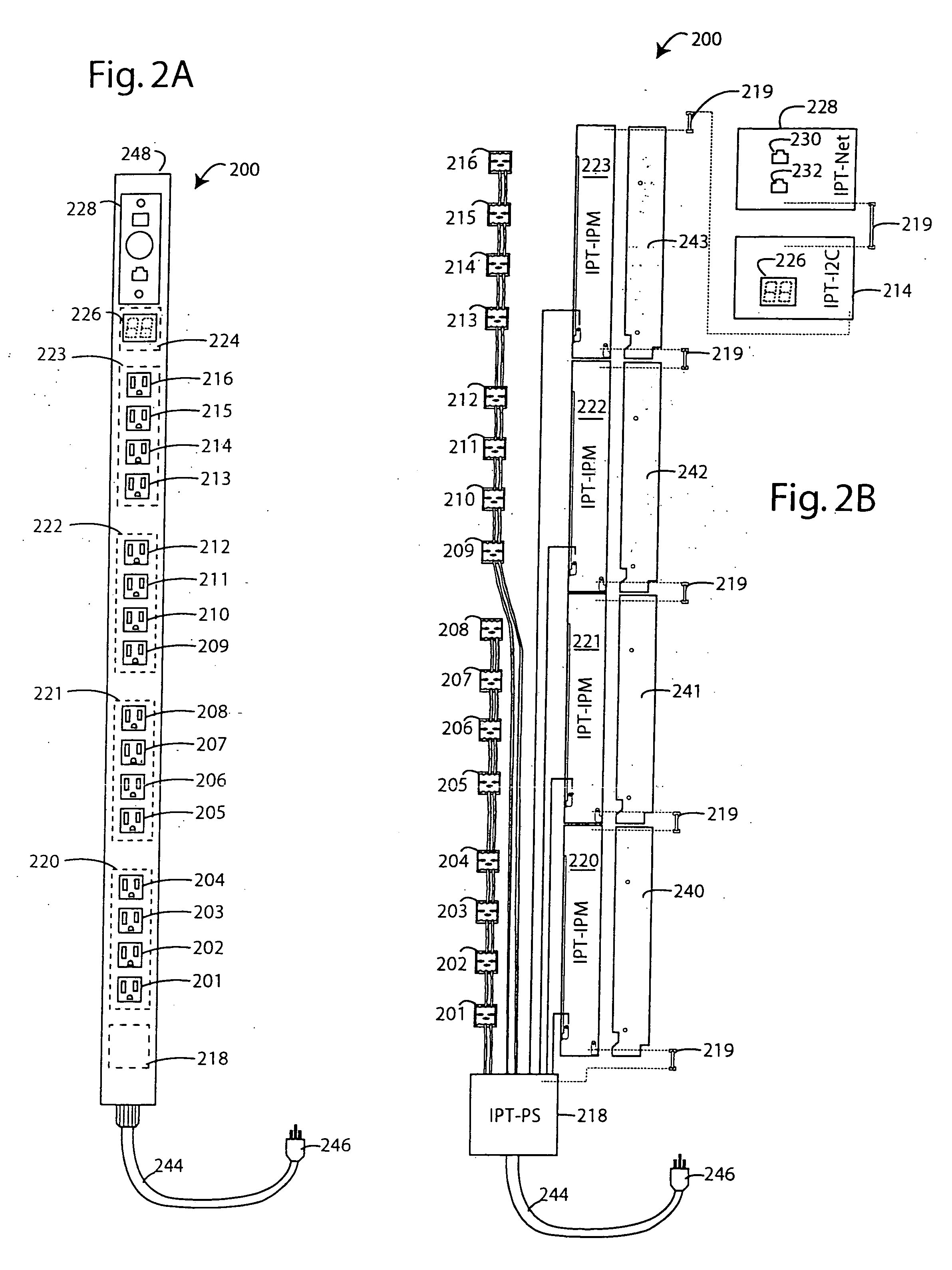

Network power management system

InactiveUS20050223090A1Vertical rackmount spaceReduce needCoupling device connectionsElectric signal transmission systemsOperational systemEmbedded operating system

Owner:SERVER TECHNOLOGY

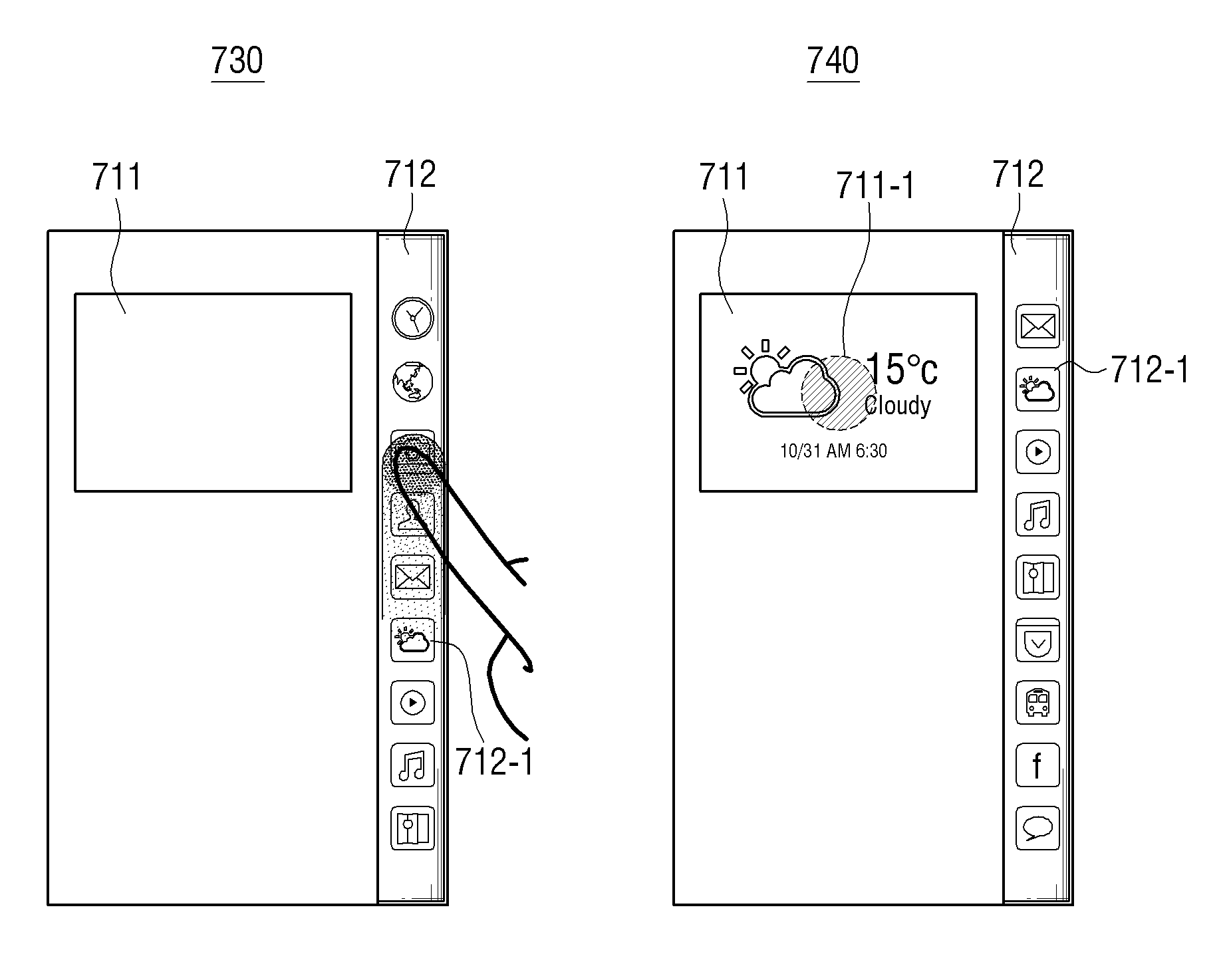

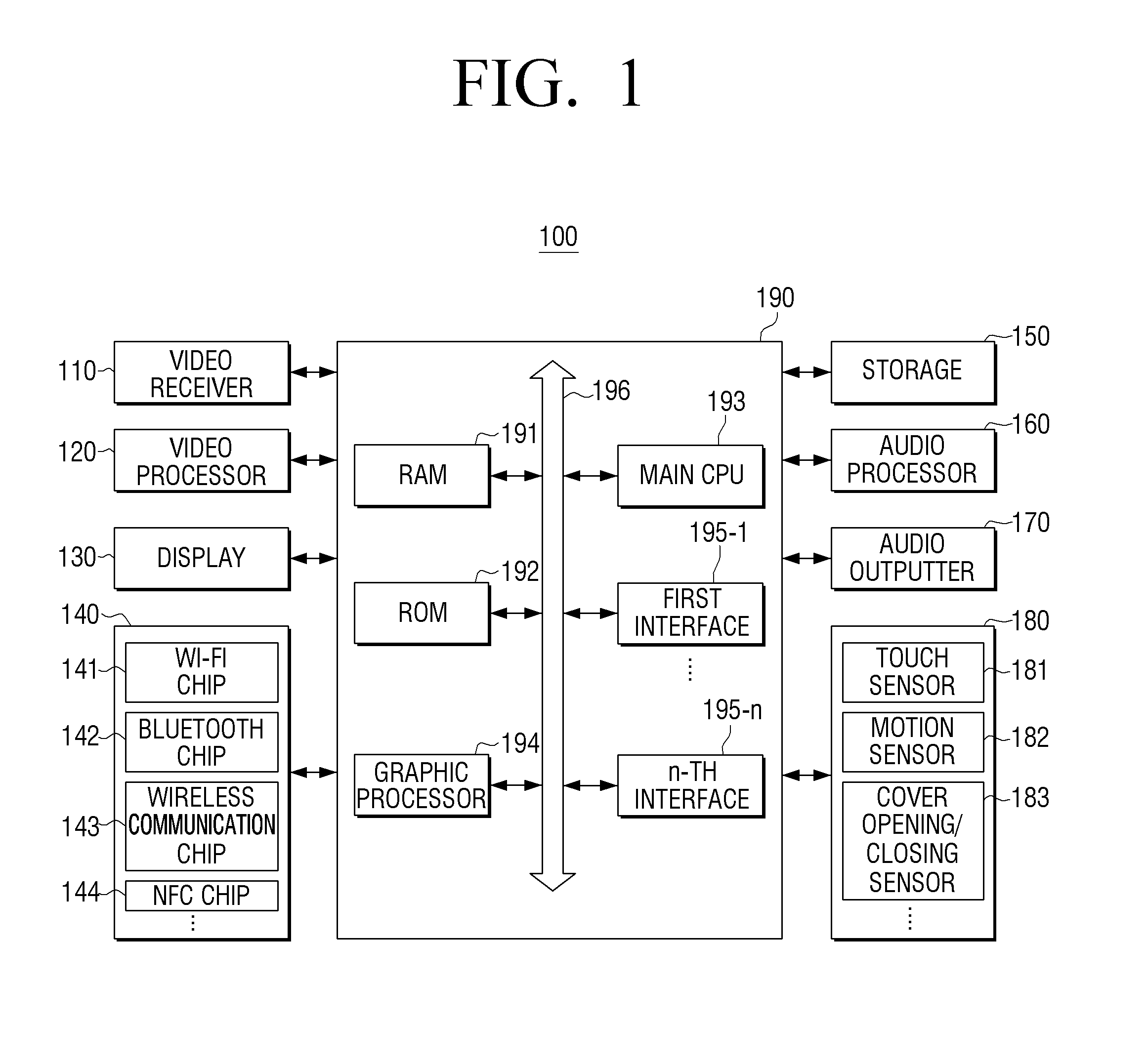

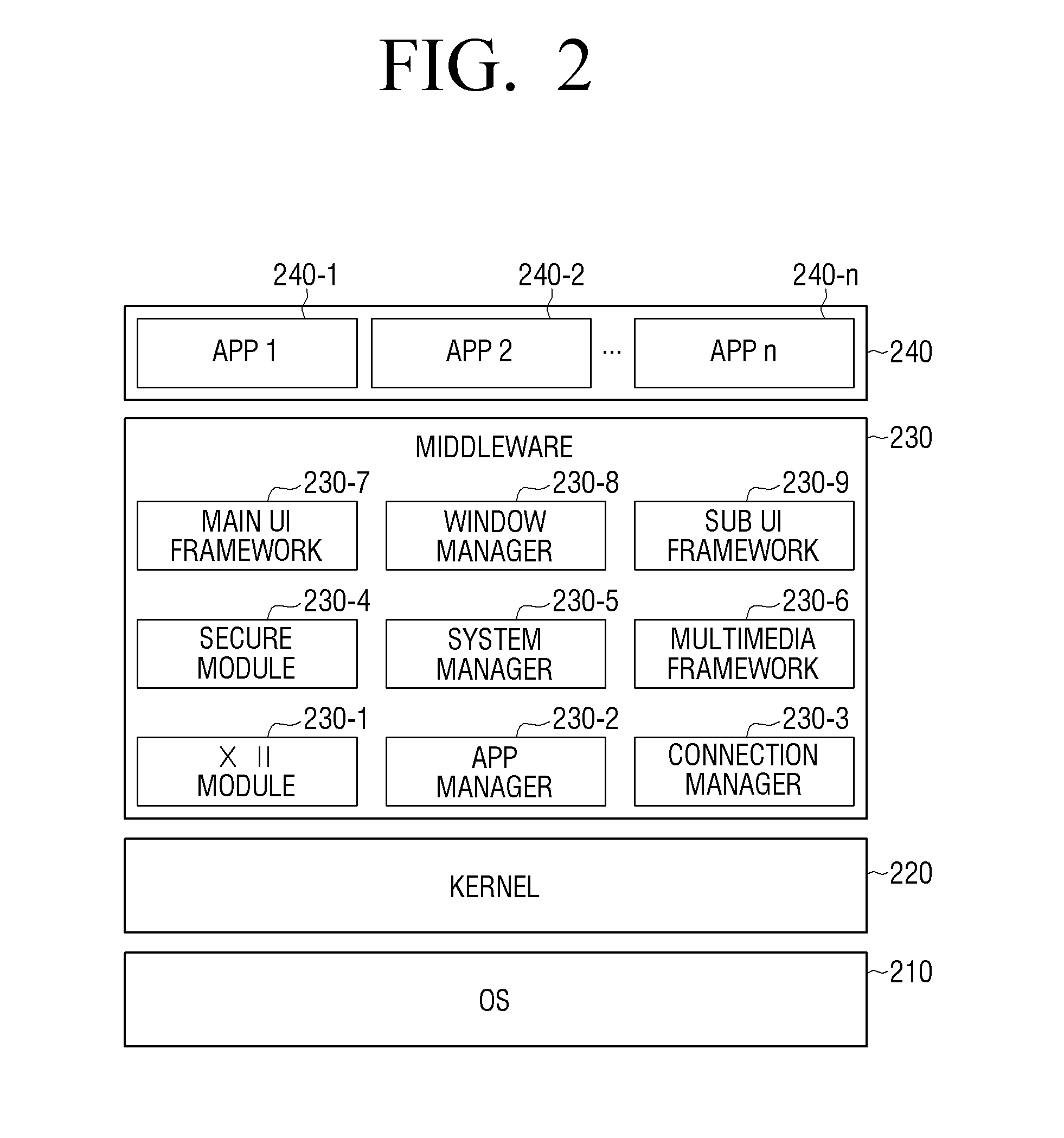

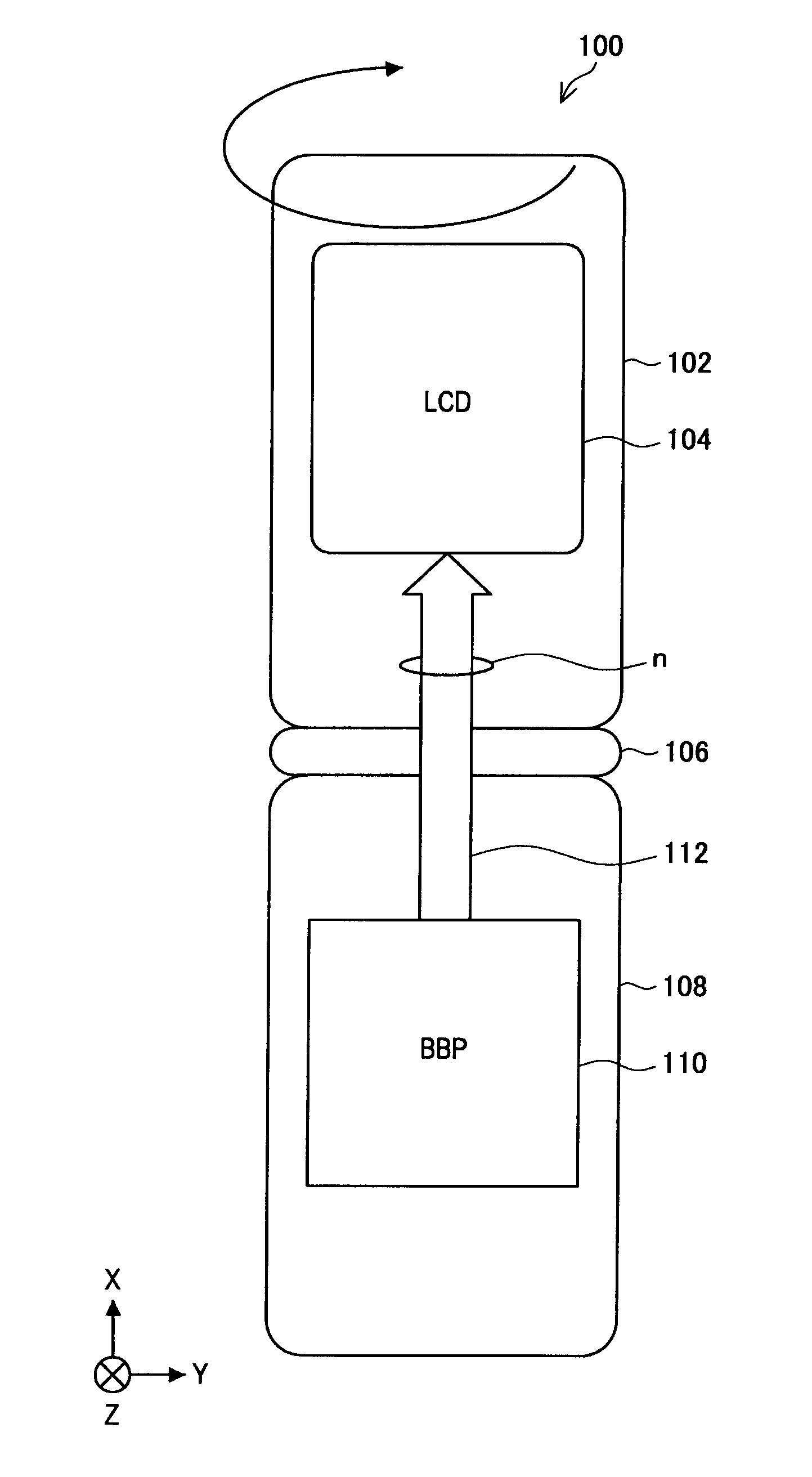

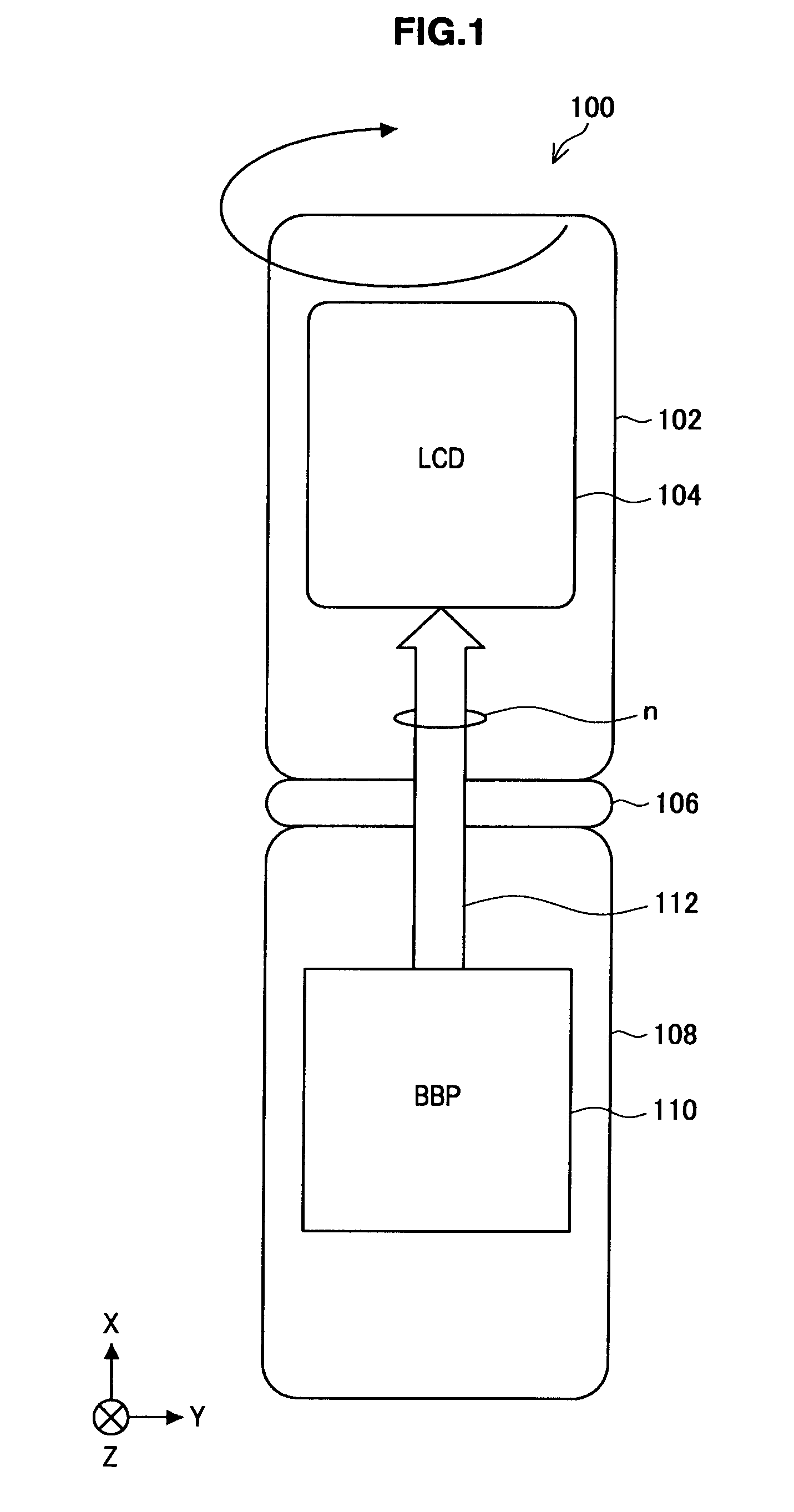

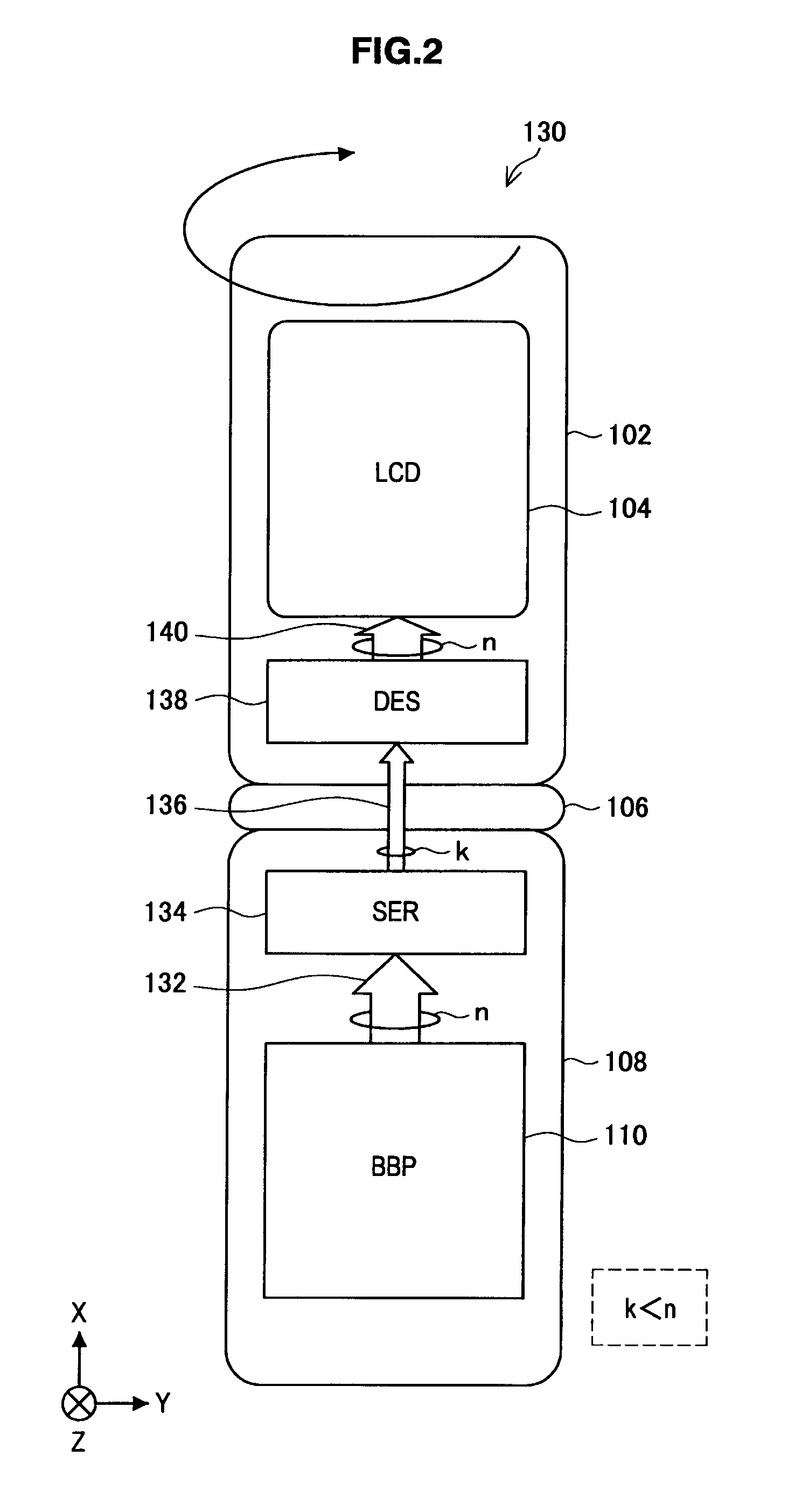

Portable terminal and display method thereof

ActiveUS20150378592A1Television system detailsDigital data processing detailsComputer graphics (images)User input

A portable terminal having a cover that includes a transparent region and a display method thereof are provided. The display method includes displaying a UI element on an exposed display region in a state that the display region is covered by a cover, and controlling the display region that corresponds to the transparent region in response to a user input for selecting the UI element.

Owner:SAMSUNG ELECTRONICS CO LTD

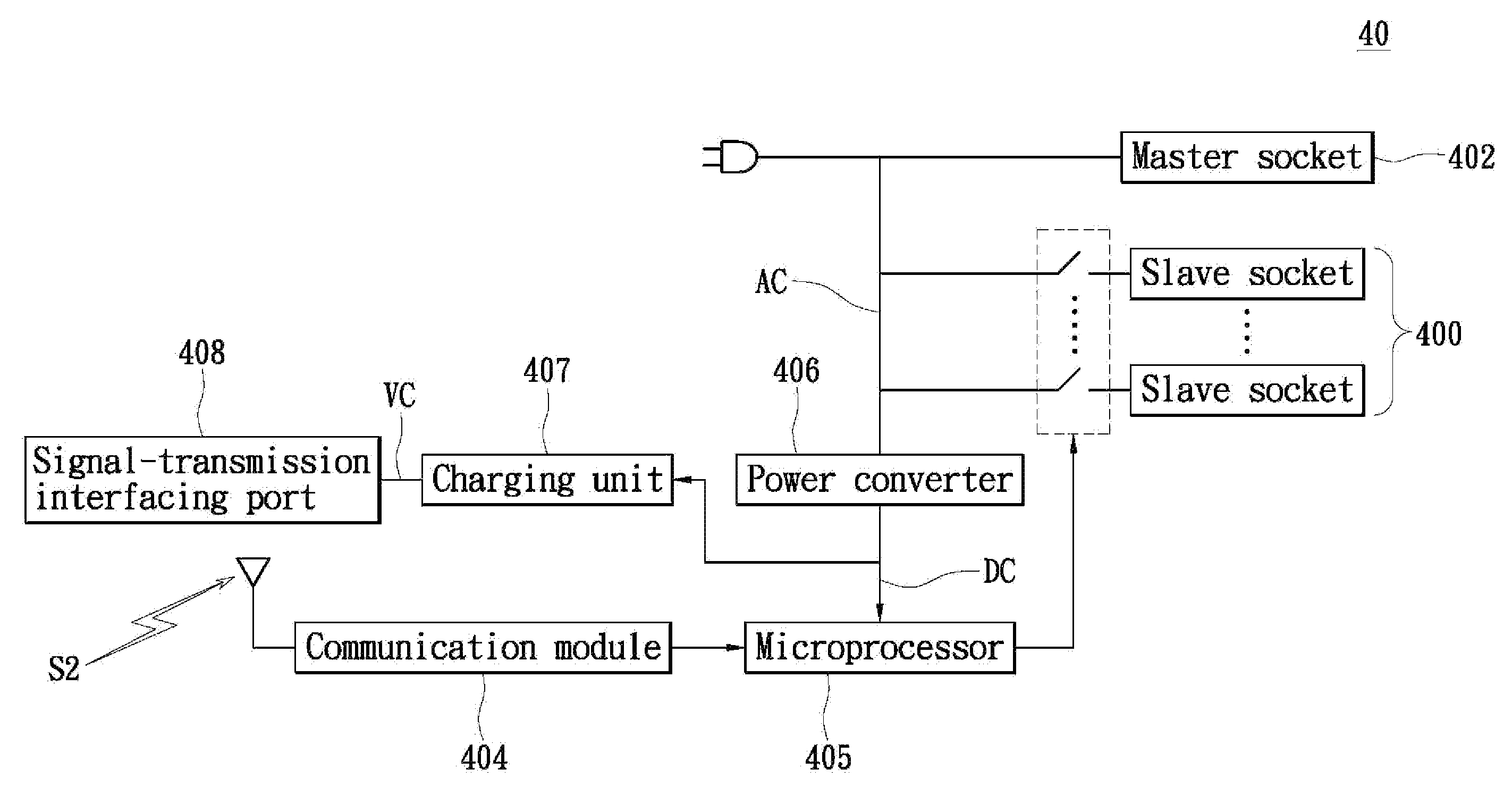

Wireless-Controlled Power-Saving Apparatus

InactiveUS20100164284A1Dc network circuit arrangementsElectric signal transmission systemsWireless controlEmbedded system

A wireless-controlled power-saving apparatus is disclosed. The apparatus particularly includes a power-saving control strip and a wireless power-detection controller. The power-saving control strip has a master socket and at least one slave socket to be controlled. The strip further includes a receptacle for containing the wireless power-detection controller. More, the wireless power-detection controller connects to an external host for detecting the performance thereof. When the external host boots up, the wireless power-detection controller controls the slave socket to be powered. Or otherwise, when the external host shuts down, the wireless power-detection controller controls the slave socket to be disconnected. Thus the invention achieves the sockets mounted on the power-saving control strip to function a wireless master-slave-correlation operation.

Owner:POWERTECH INDAL

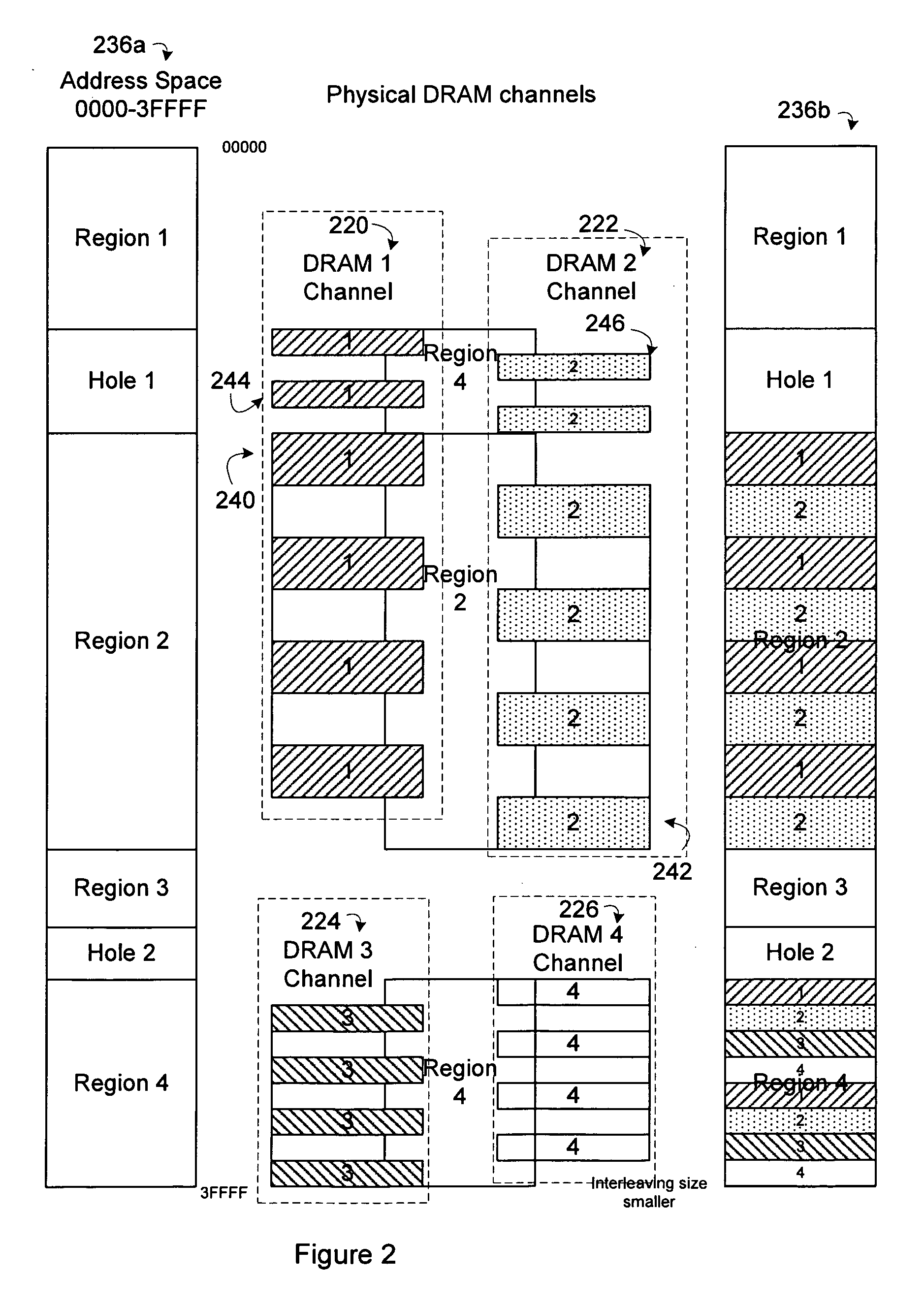

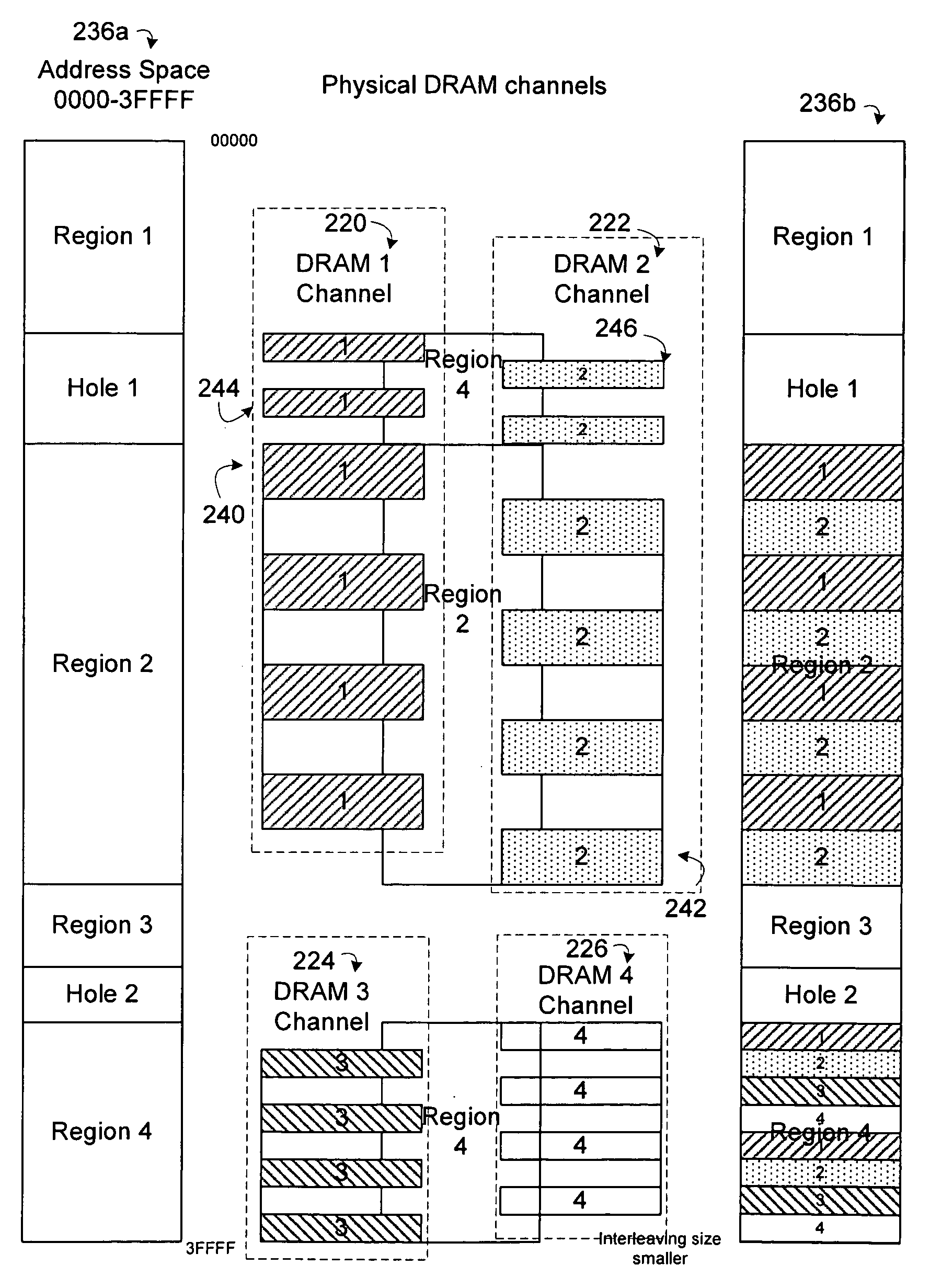

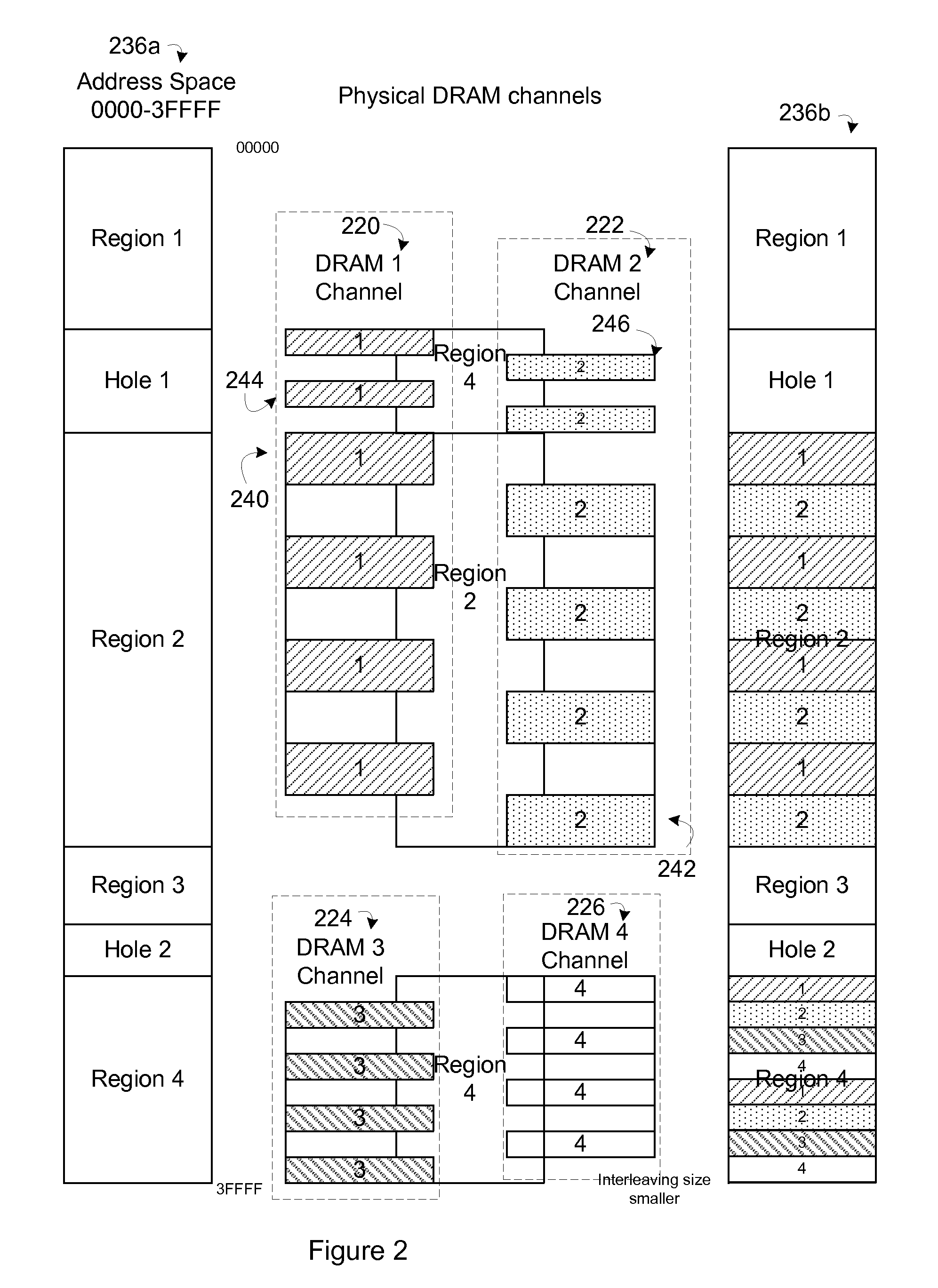

Various methods and apparatus for configurable mapping of address regions onto one or more aggregate targets

InactiveUS20080320255A1Memory adressing/allocation/relocationDigital computer detailsIntellectual propertyInterleaved memory

An interconnect for an integrated circuit communicating transactions between initiator Intellectual Property (IP) cores and multiple target IP cores coupled to the interconnect is generally described. The interconnect routes the transactions between the target IP cores and initiator IP cores in the integrated circuit. A first aggregate target of the target IP cores includes two or more memory channels that are interleaved in an address space for the first aggregate target in the address map. Each memory channel is divided up in defined memory interleave segments and then interleaved with memory interleave segments from other memory channels. An address map is divided up into two or more regions. Each interleaved memory interleave segment is assigned to at least one of those regions and populates the address space for that region, and parameters associated with the regions and memory interleave segments are configurable.

Owner:META PLATFORMS TECH LLC

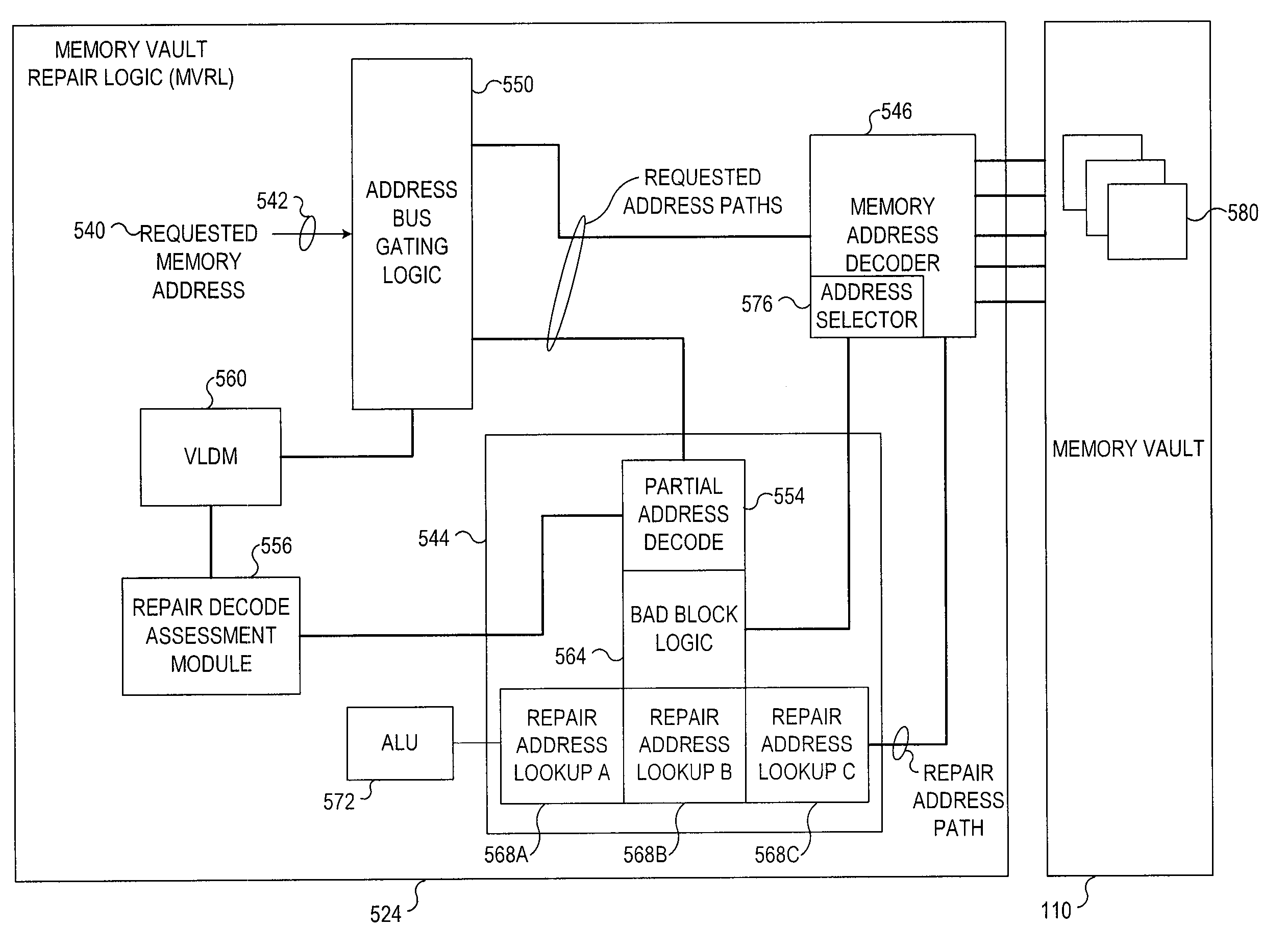

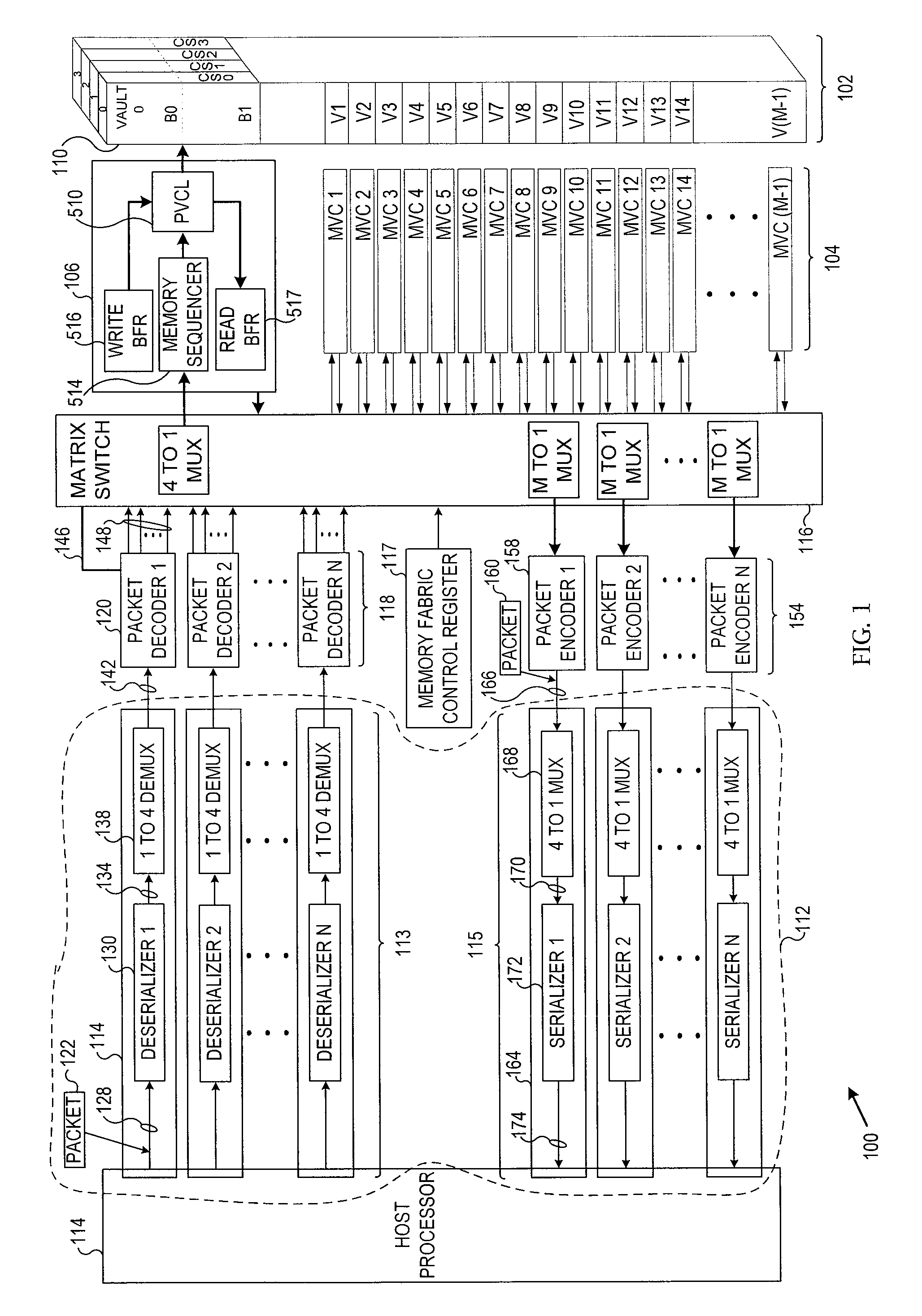

Switched interface stacked-die memory architecture

ActiveUS20100110745A1Efficient power electronics conversionDigital storageMemory addressAddress decoder

Systems and methods disclosed herein include those that may receive a memory request including a requested memory address and may send the memory request directly to an address decoder associated with a stacked-die memory vault without knowing whether a repair address is required. If a subsequent analysis of the memory request shows that a repair address is required, an in-process decode of the requested memory address can be halted and decoding of the repair address initiated.

Owner:MICRON TECH INC

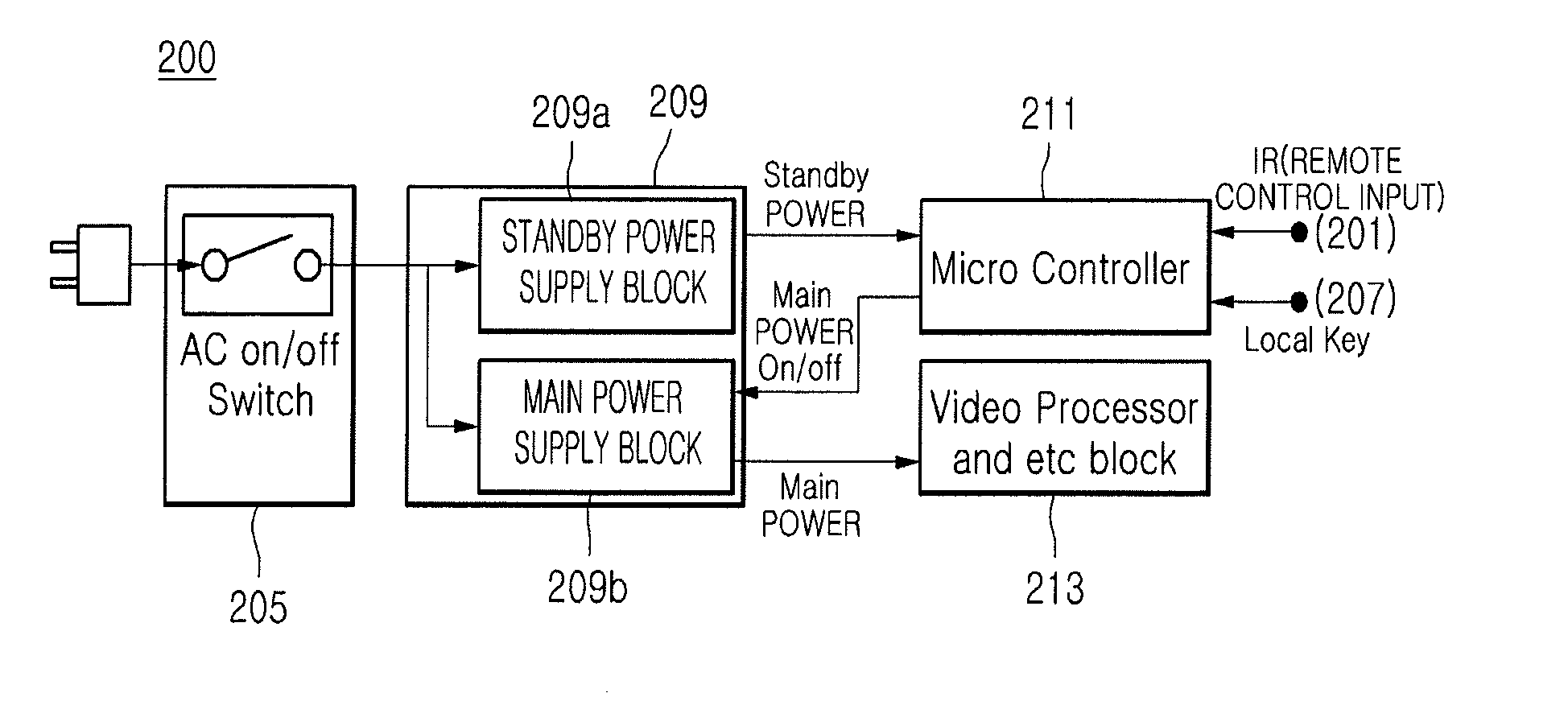

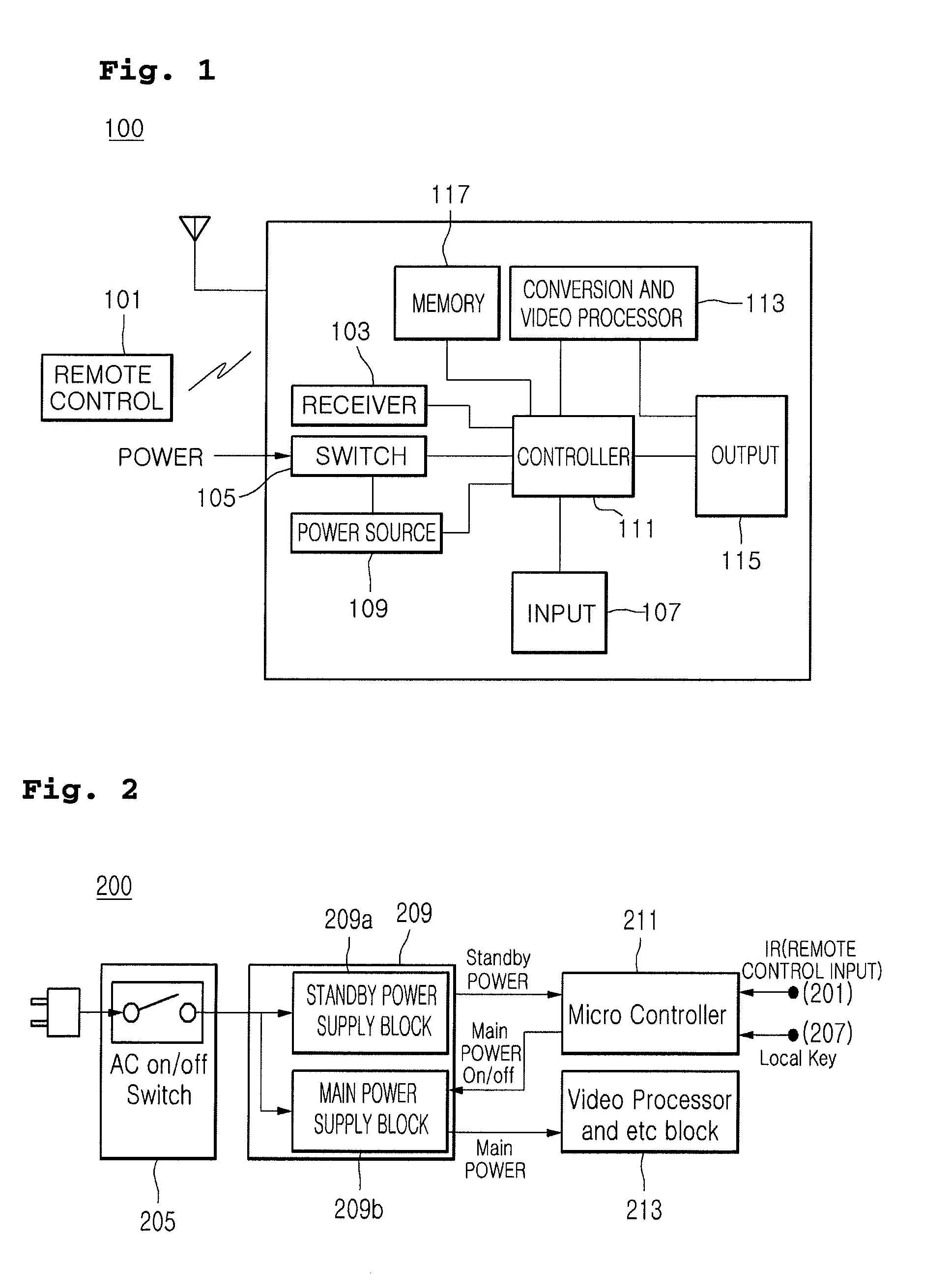

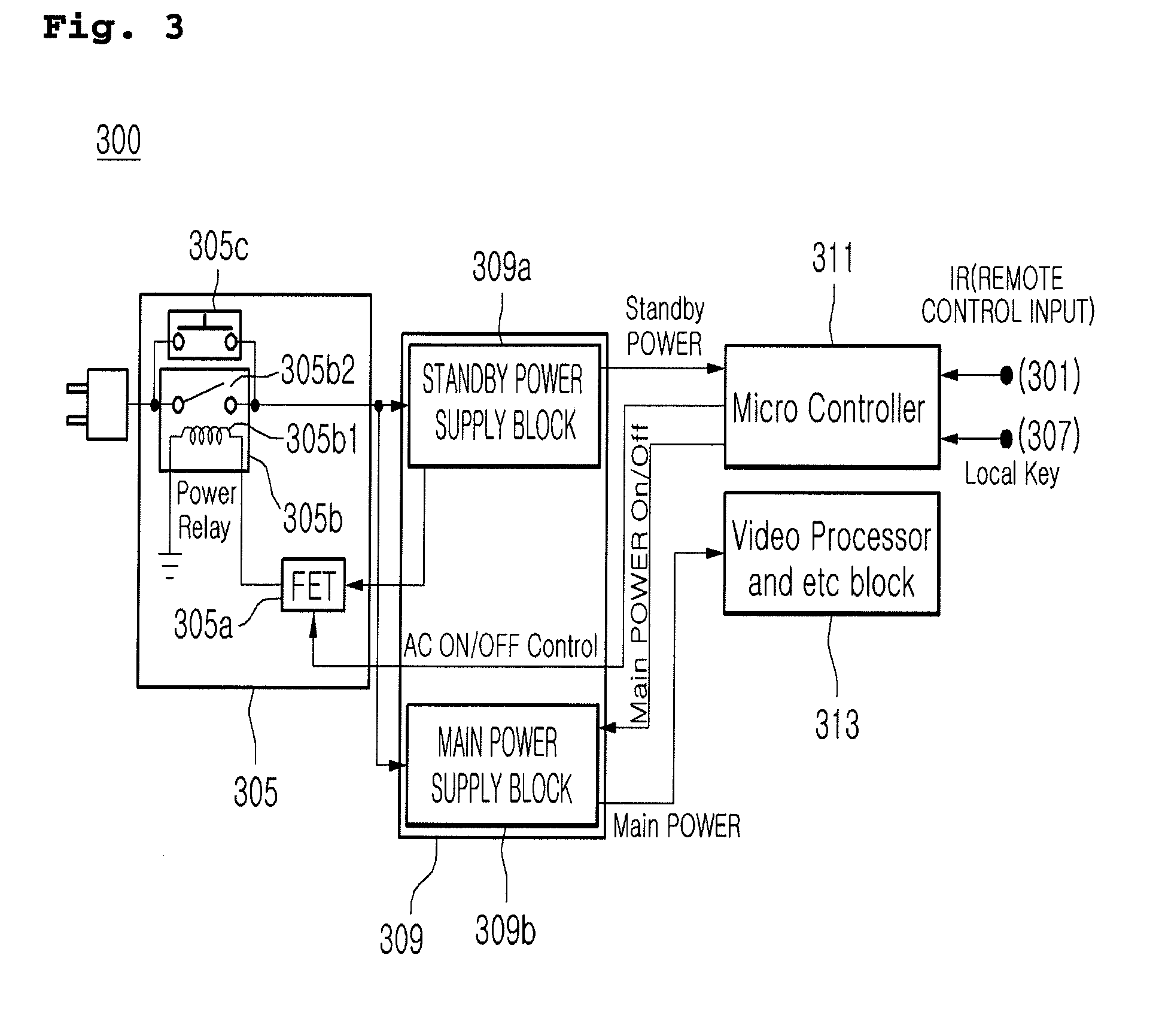

Apparatus and method for controlling input power

An apparatus and method for controlling an input power according to power management modes of a display device. In a saving mode of the power management modes, a power supply to the system is turned OFF according to an organic operation between components of the system. Thus, because the power supply to a power block within the system is turned OFF all, a consumed power is in a substantially zero state, comparable to a state in which a power plug is physically pulled out.

Owner:LG ELECTRONICS INC

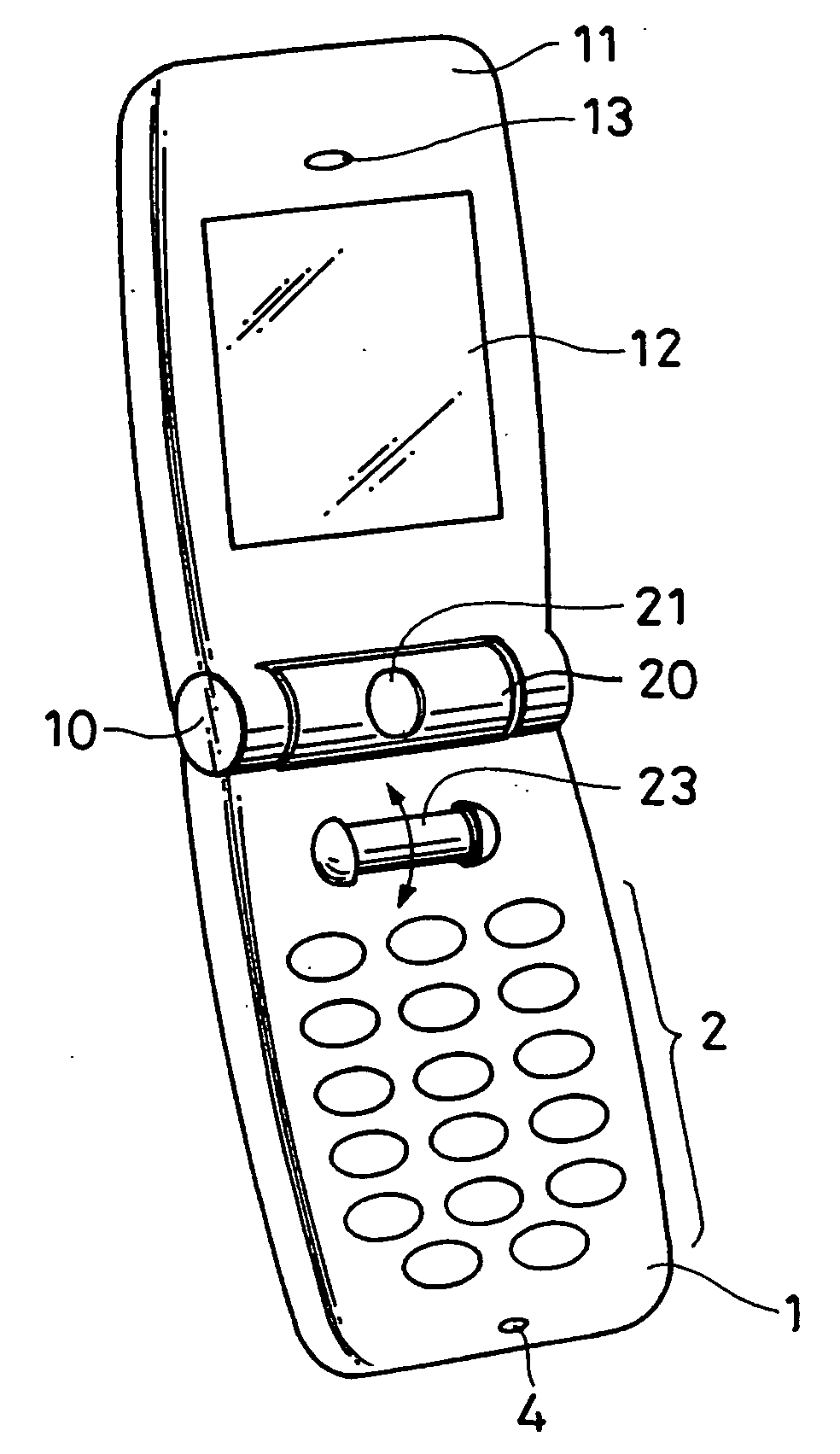

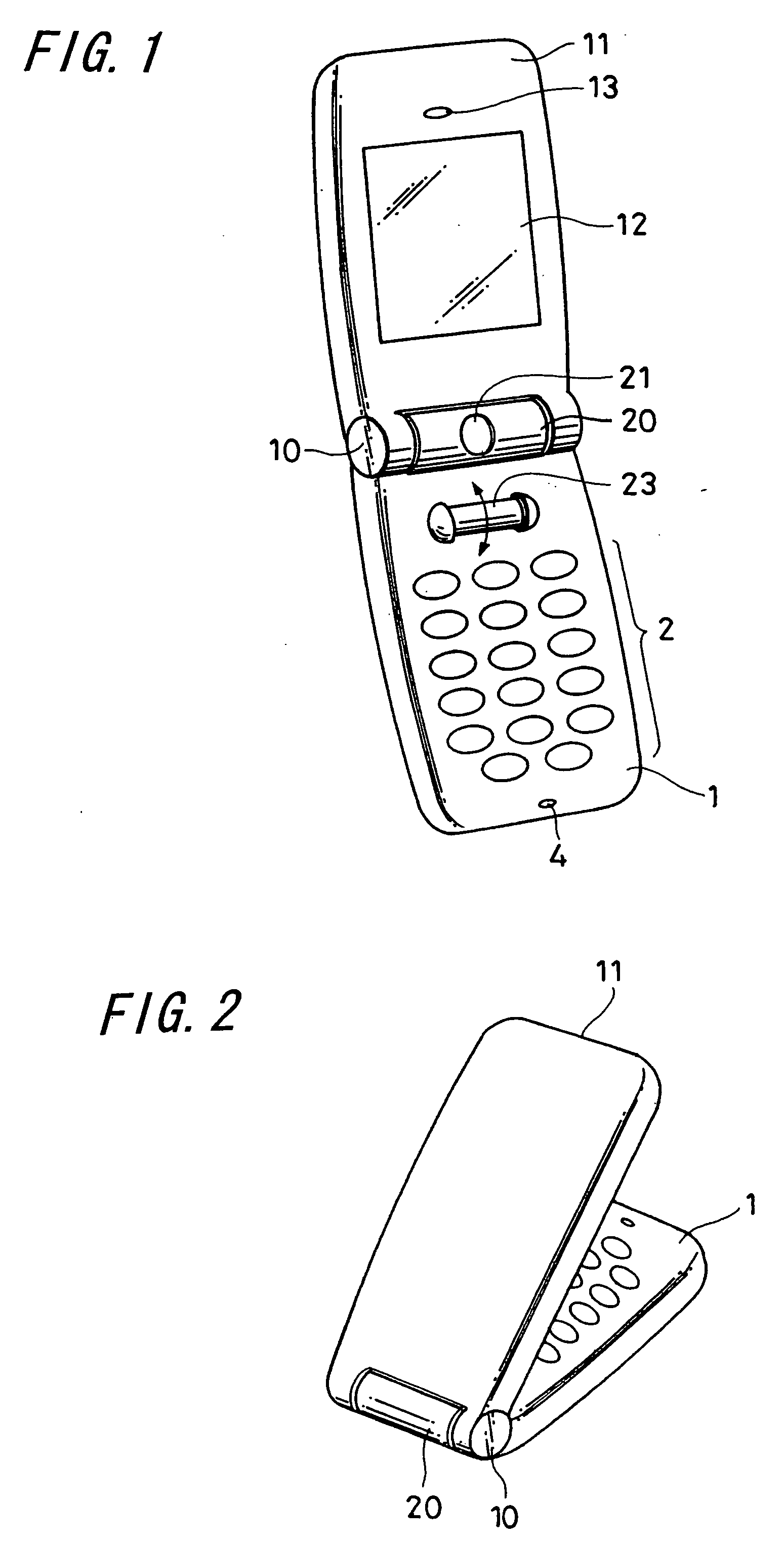

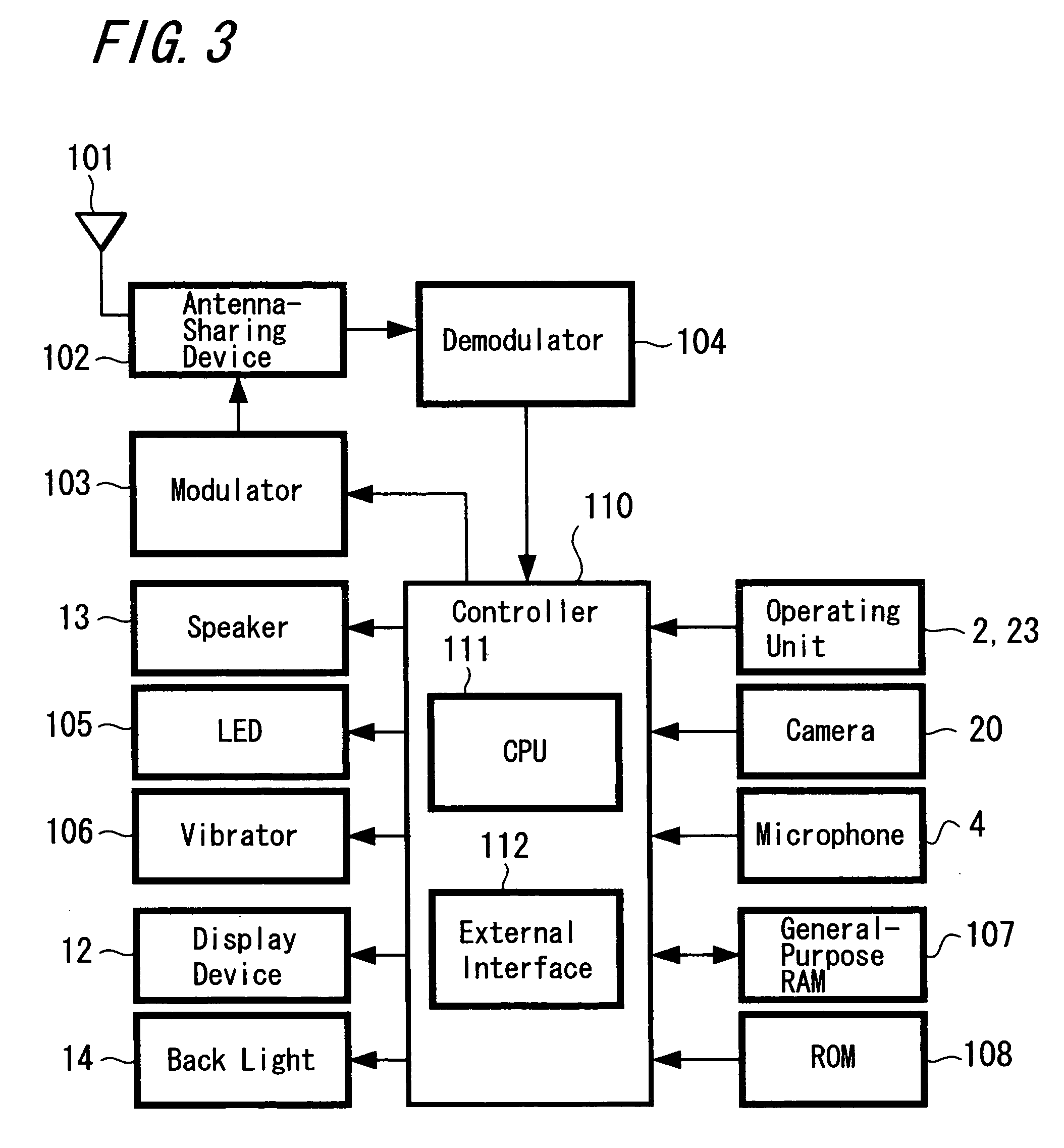

Electronic device

InactiveUS20050272462A1Reduce useless power consumptionWireless communication energy reductionPower managementElectric forceElectrical and Electronics engineering

Owner:SONY ERICSSON MOBILE COMM JAPAN INC

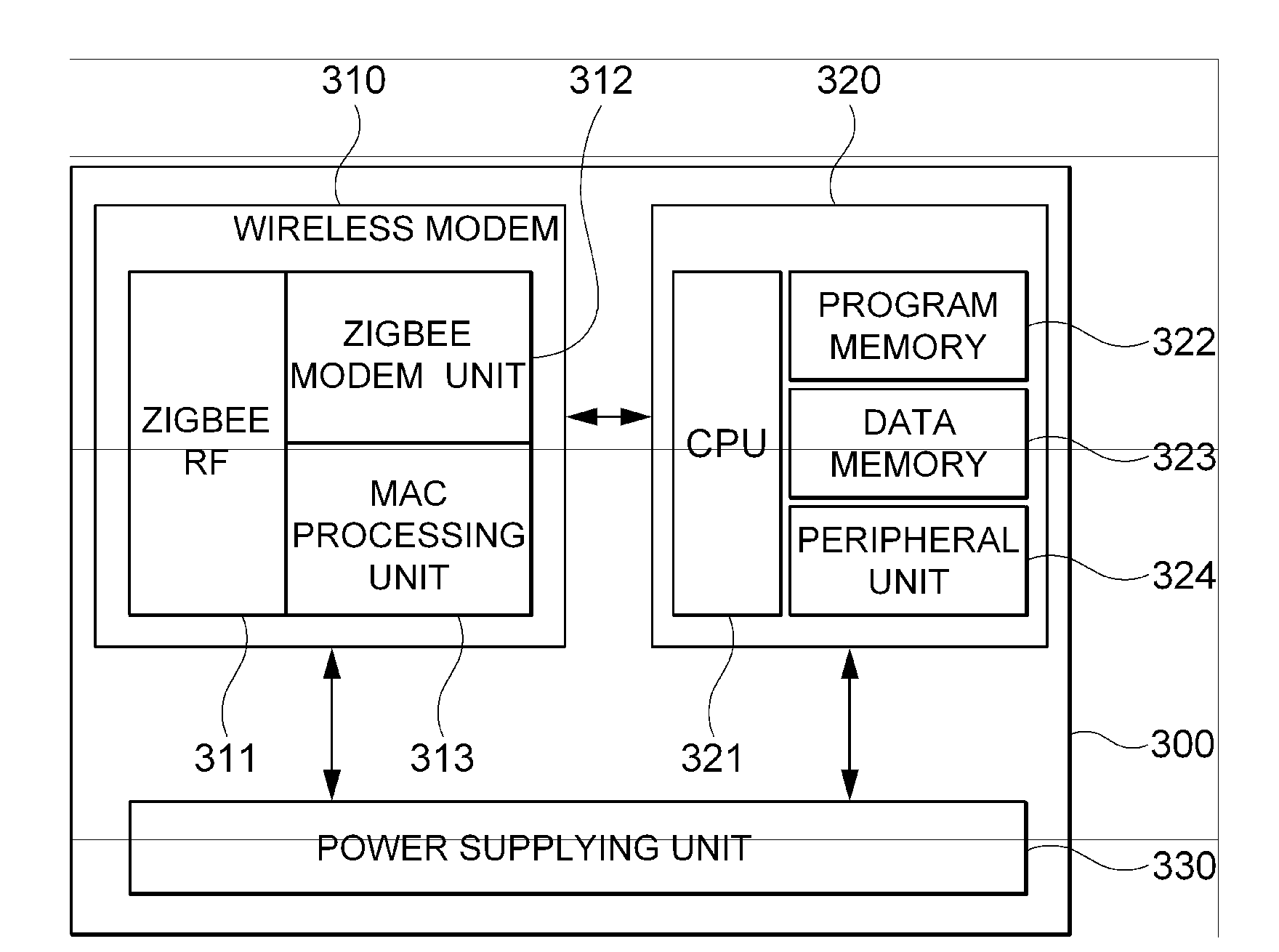

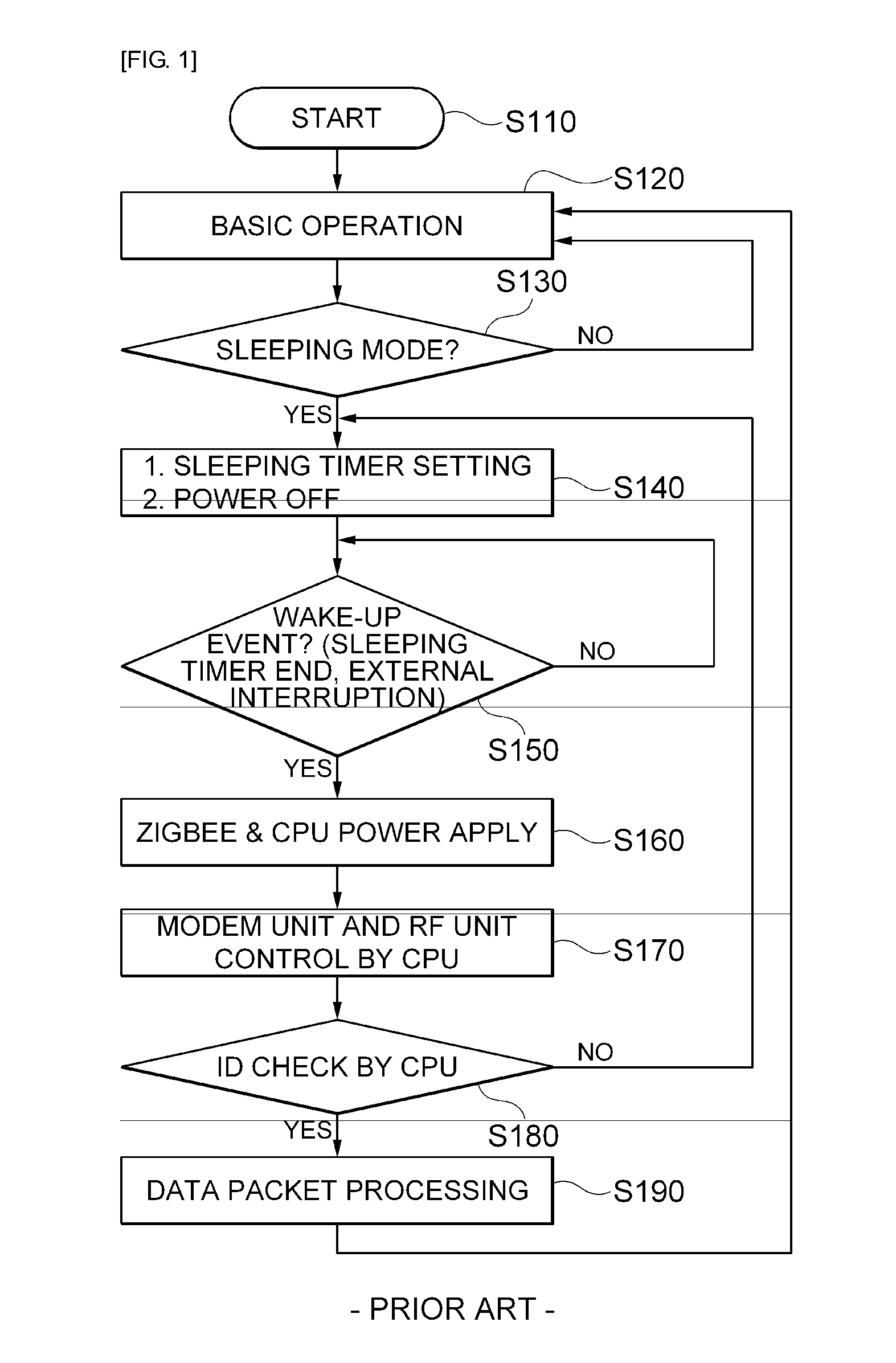

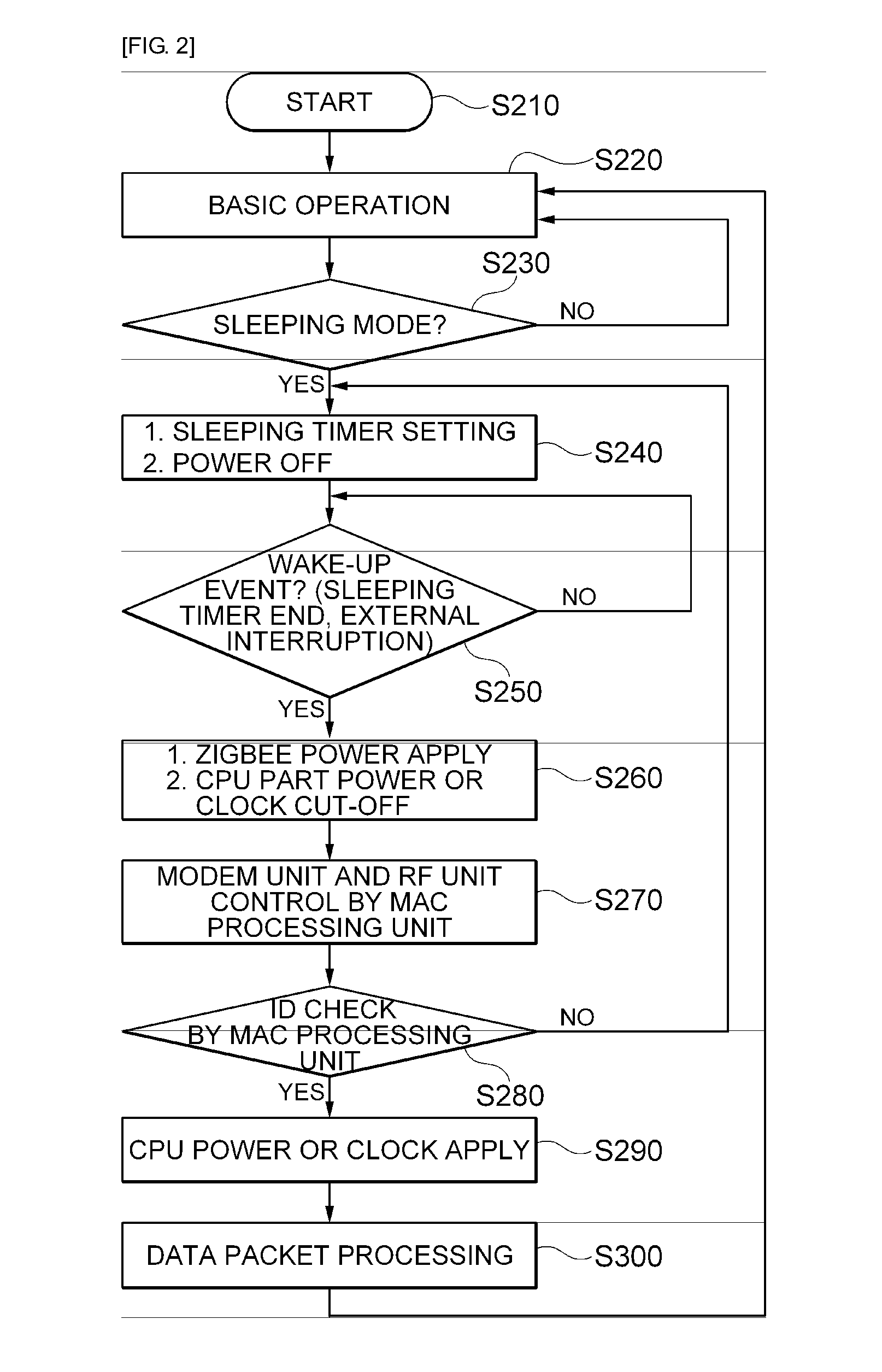

Low power zigbee device and low power wake-up method

InactiveUS20100115302A1Reduce unnecessary power consumptionPower managementVolume/mass flow measurementModem deviceMedia access control

Provided is a low-power ZigBee device provided with a sleeping mode and an active mode including a power supplying unit for supplying a power; a Medium Access Control (MAC) processing unit for receiving a wake-up packet and for controlling a modem unit and an Radio Frequency (RF) unit; and a Central Processing Unit (CPU) for receiving and processing a data packet, wherein the MAC processing unit makes the power supplying unit apply a power to the CPU based on a result of checking an identification (ID) of the wake-up packet.

Owner:SOLUM CO LTD

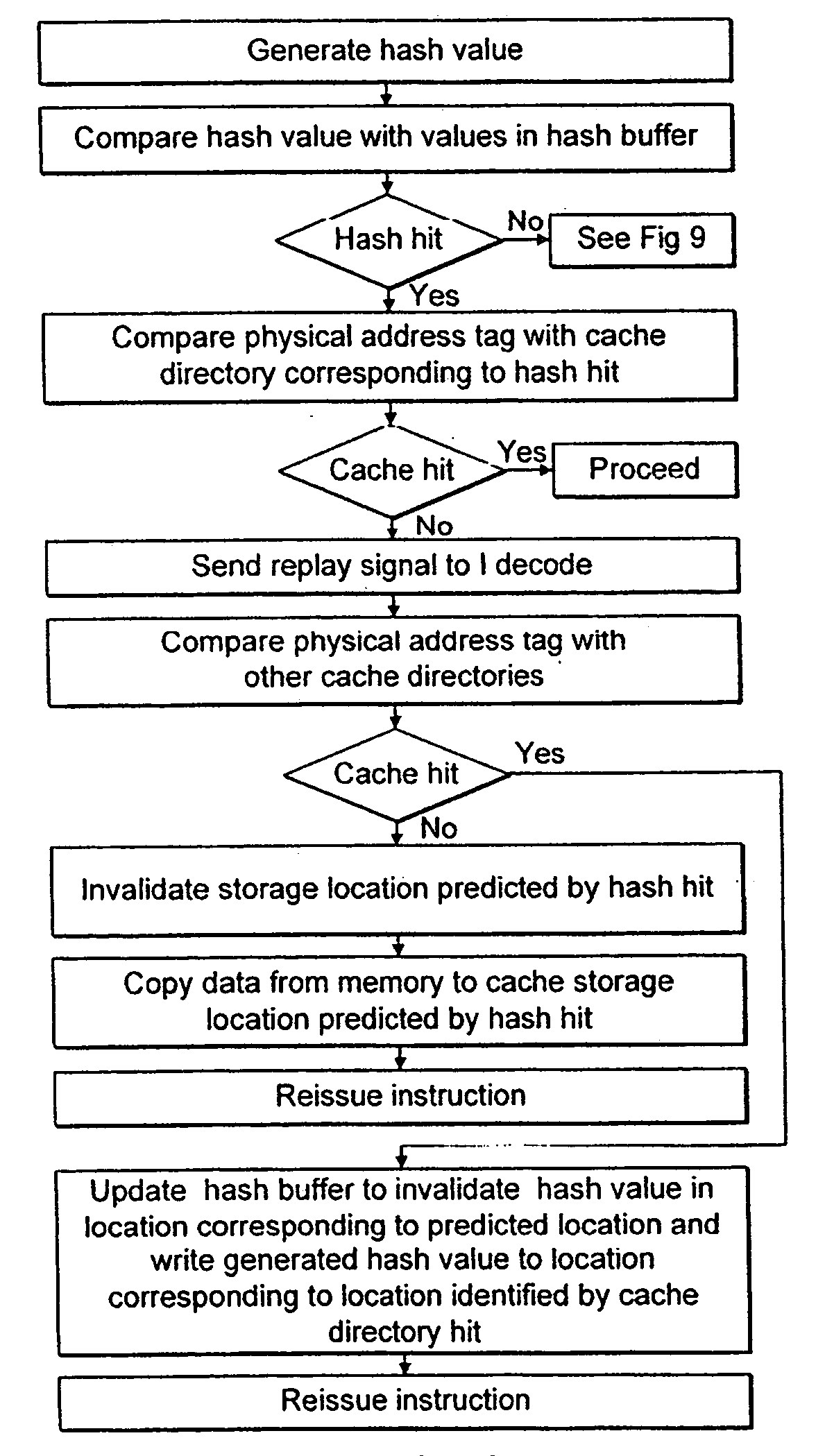

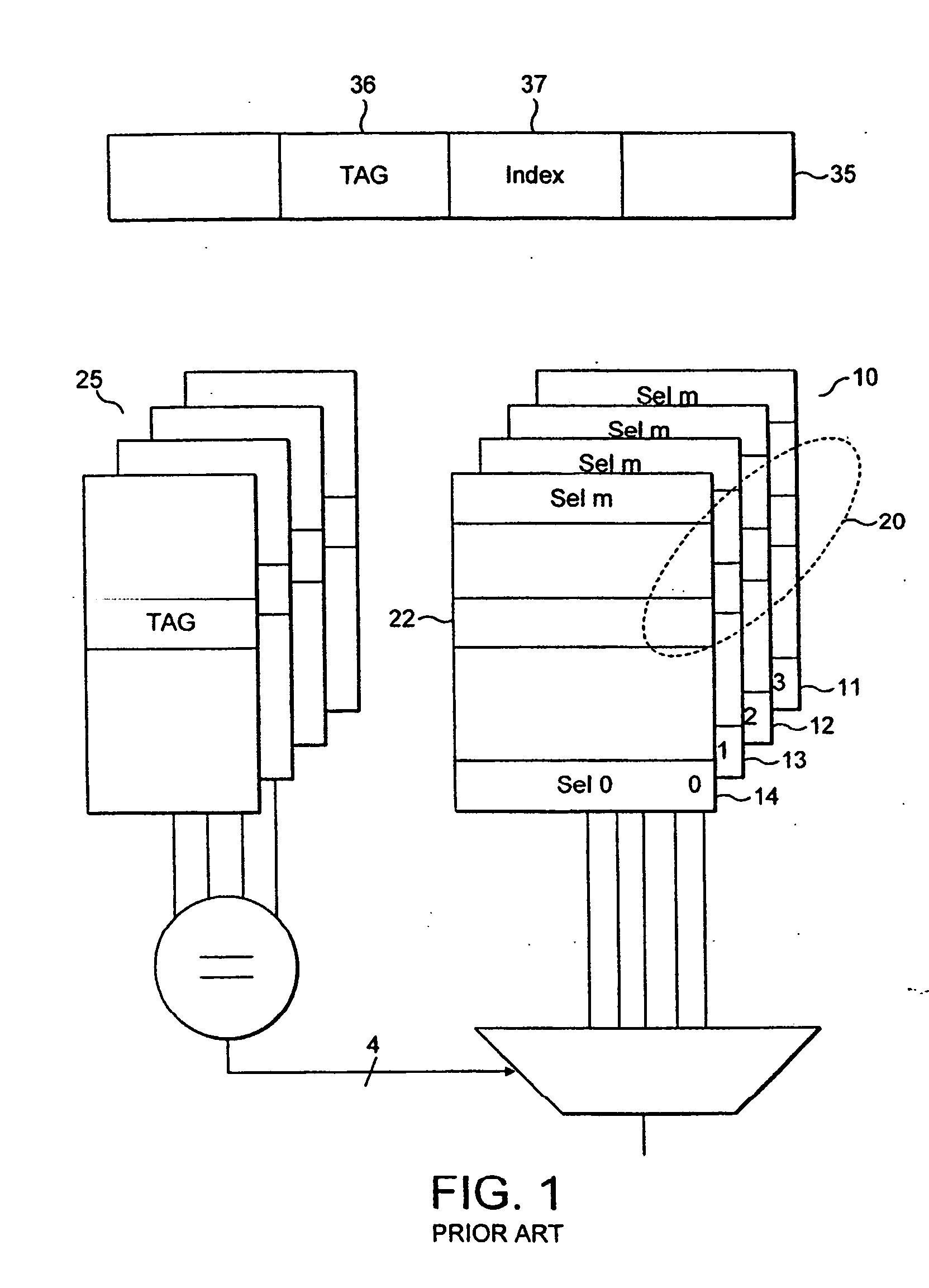

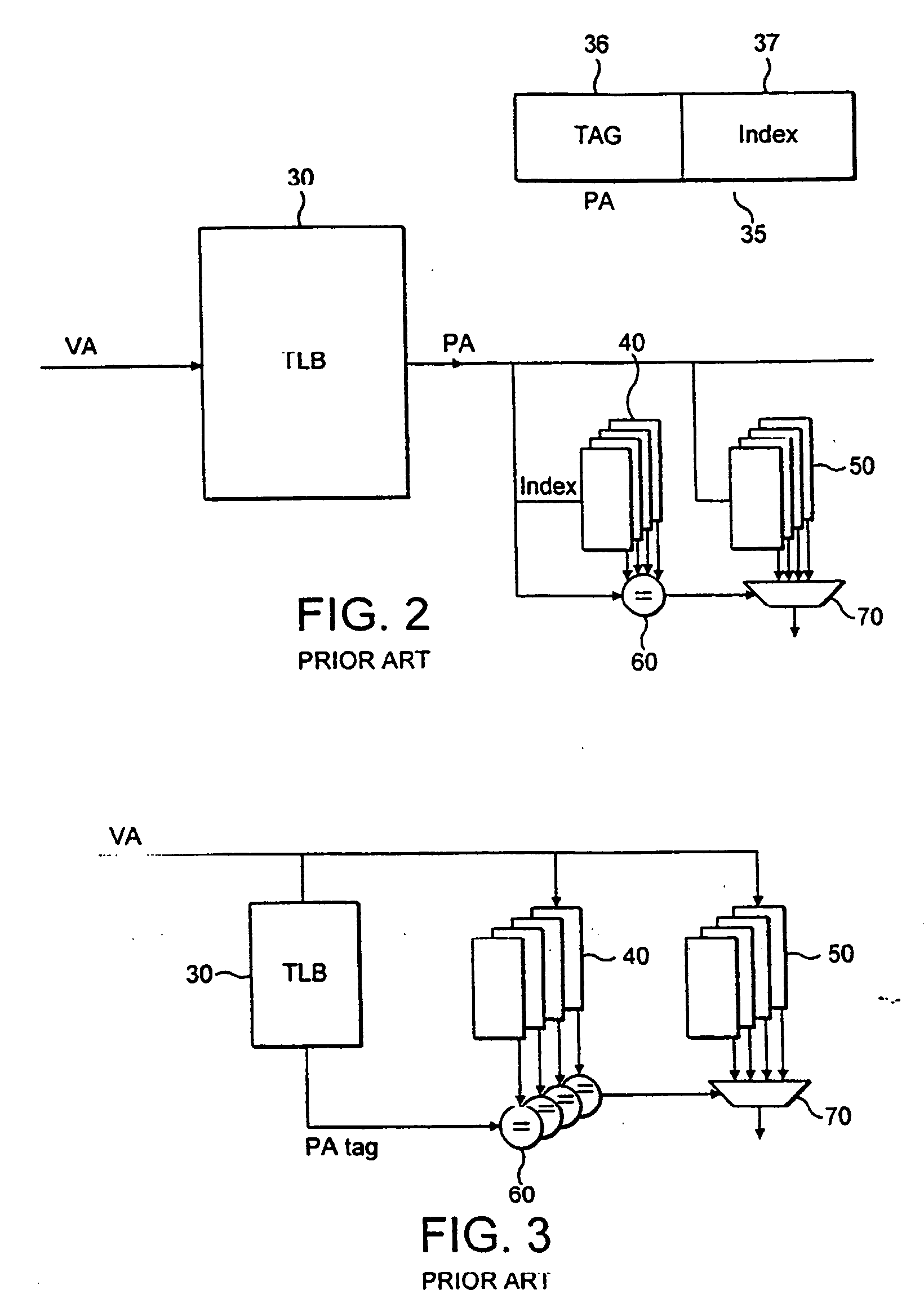

Time and power reduction in cache accesses

InactiveUS20070028051A1Reduce the number of stepsReduce widthMemory architecture accessing/allocationEnergy efficient ICTCache accessData buffer

Owner:ARM LTD +1

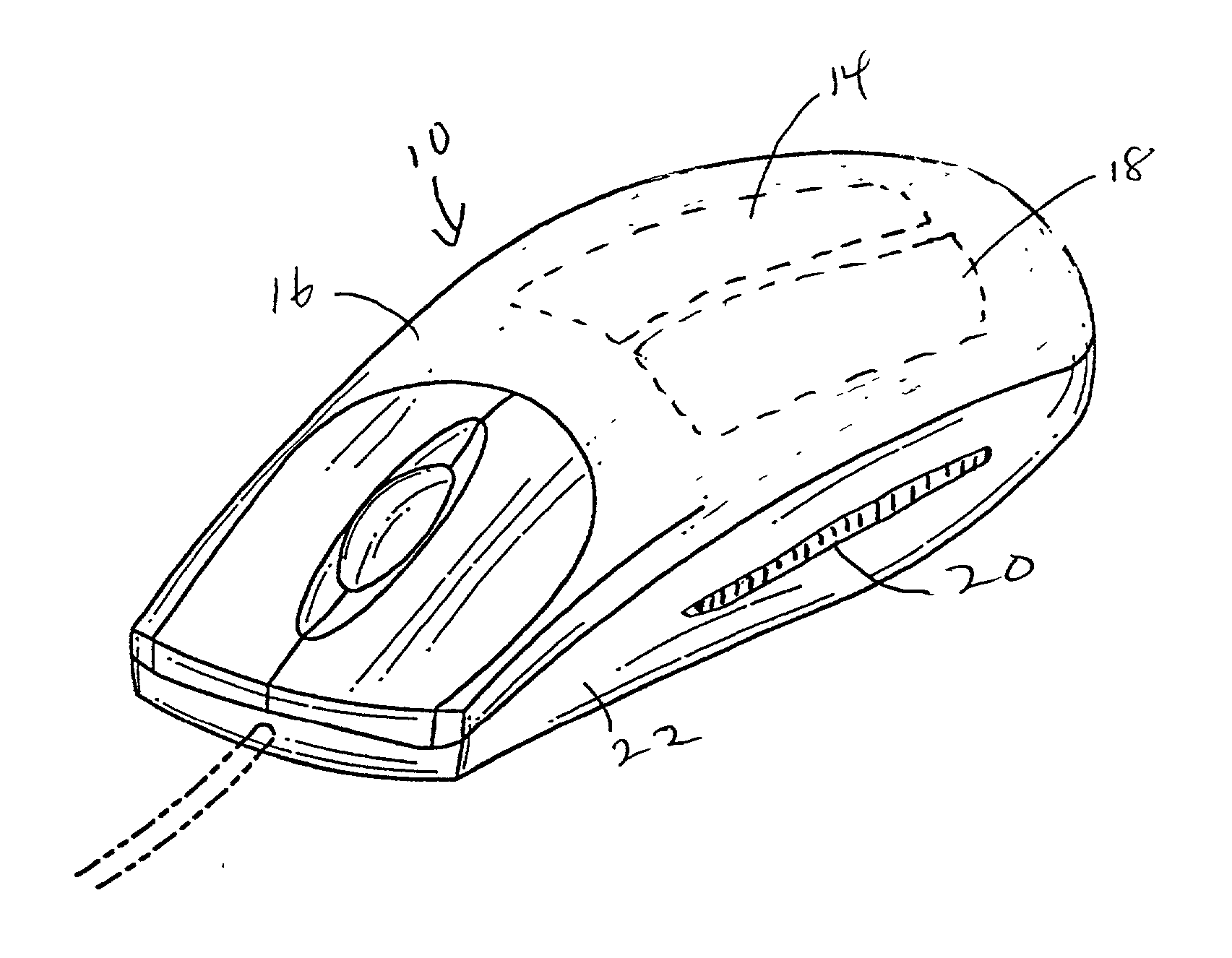

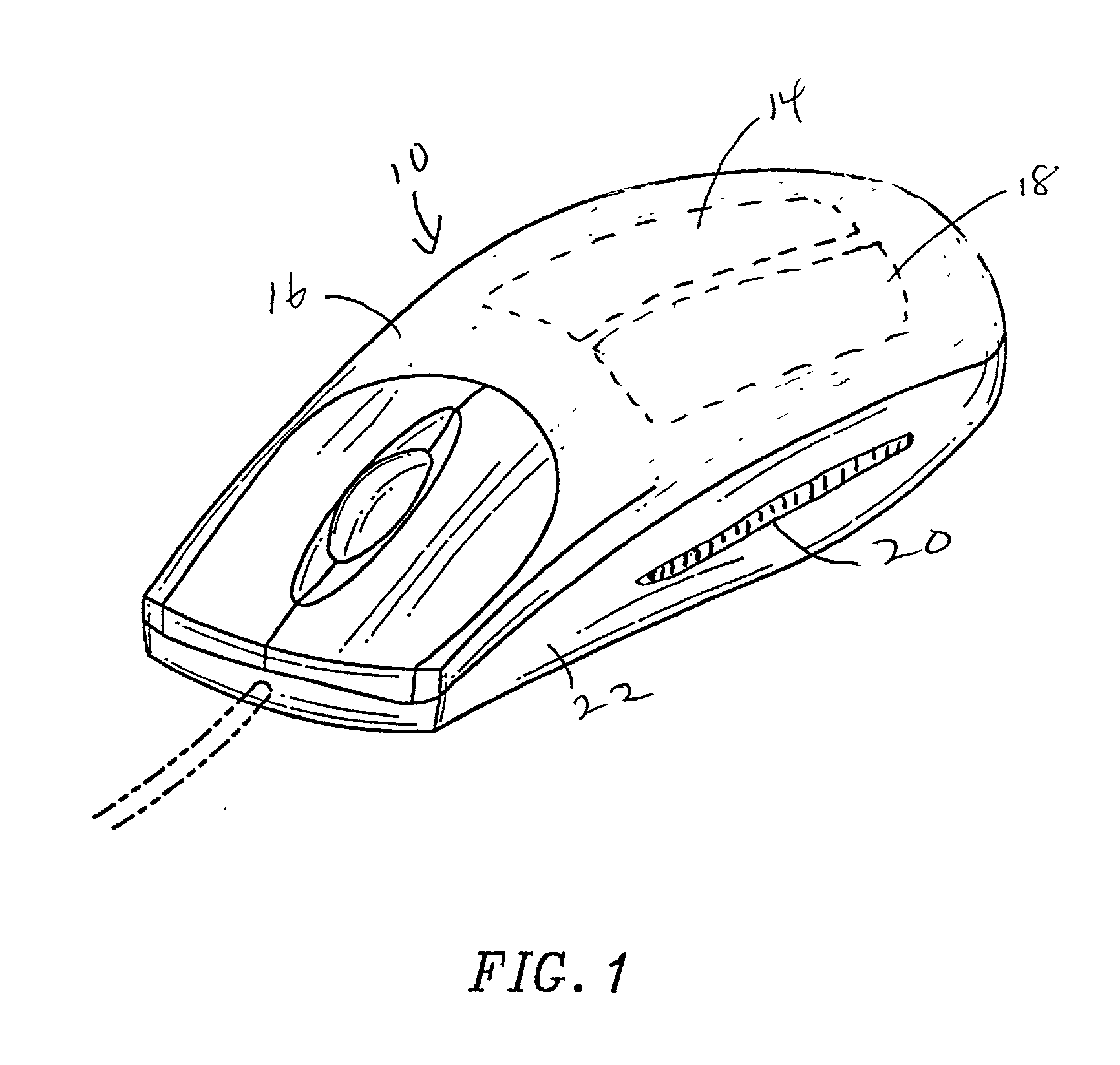

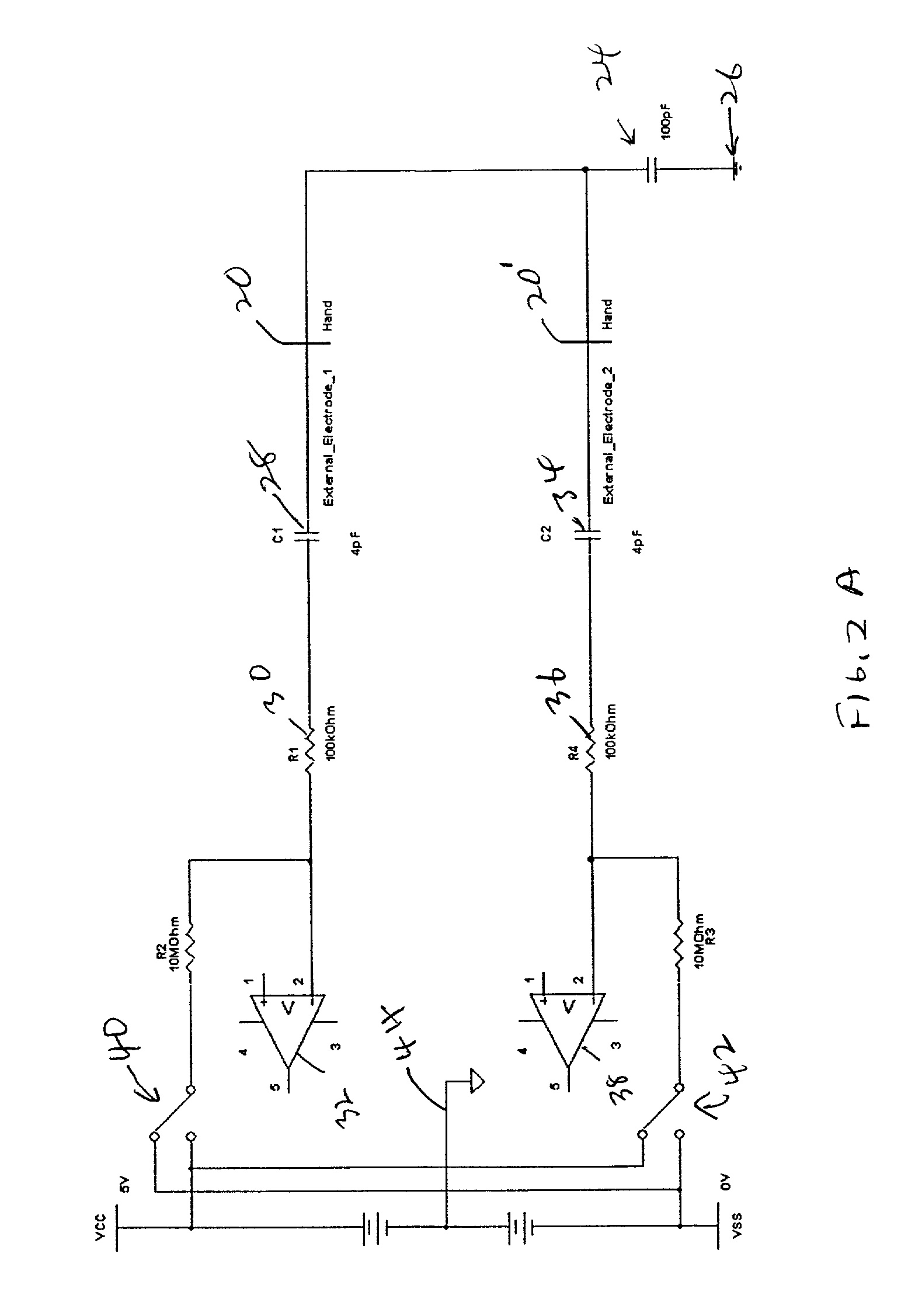

Input device with capacitive antenna

InactiveUS20020126094A1Minimize impactSave powerCathode-ray tube indicatorsPower supply for data processingCapacitanceUser input

An input device having a housing and electronic circuitry for detecting user inputs, and transmitting signals corresponding to those inputs to an electronic device, such as a computer. An antenna is provided for transmitting or receiving signals. A hand detection circuit is provided, which uses said antenna for detecting the proximity of a user's hand to the housing and producing a hand detect signal in response. In one embodiment, the antenna is a capacitive antenna. A capacitor is switched in parallel with the antenna when it is used in antenna mode, so that the impact on the antenna signaling of the capacitance of a user's hand is minimized. In one embodiment, a sleep mode is provided for the electronic circuitry to conserve power. The hand detect signal will awaken the input device from its sleep mode.

Owner:LOGITECH EURO SA

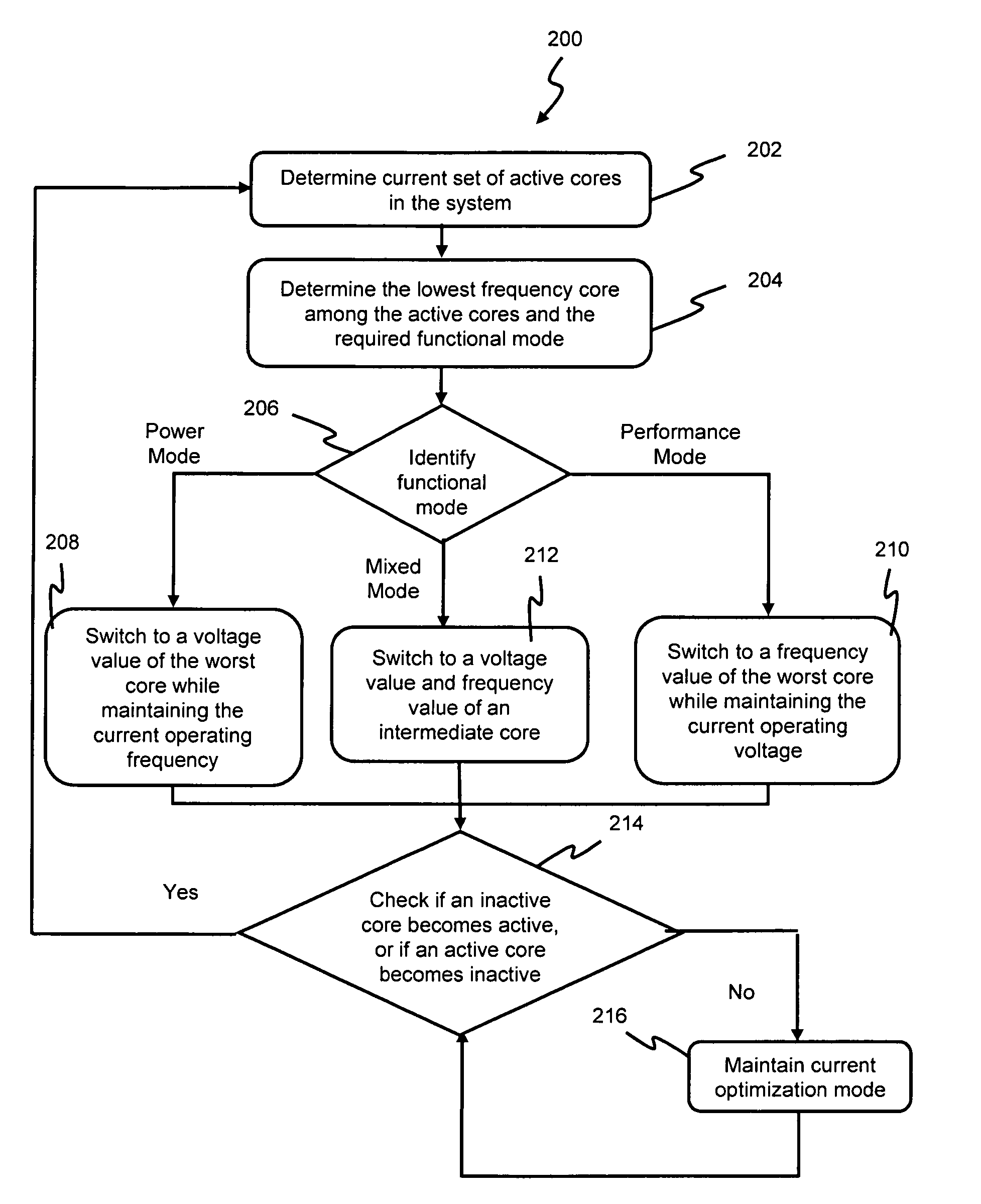

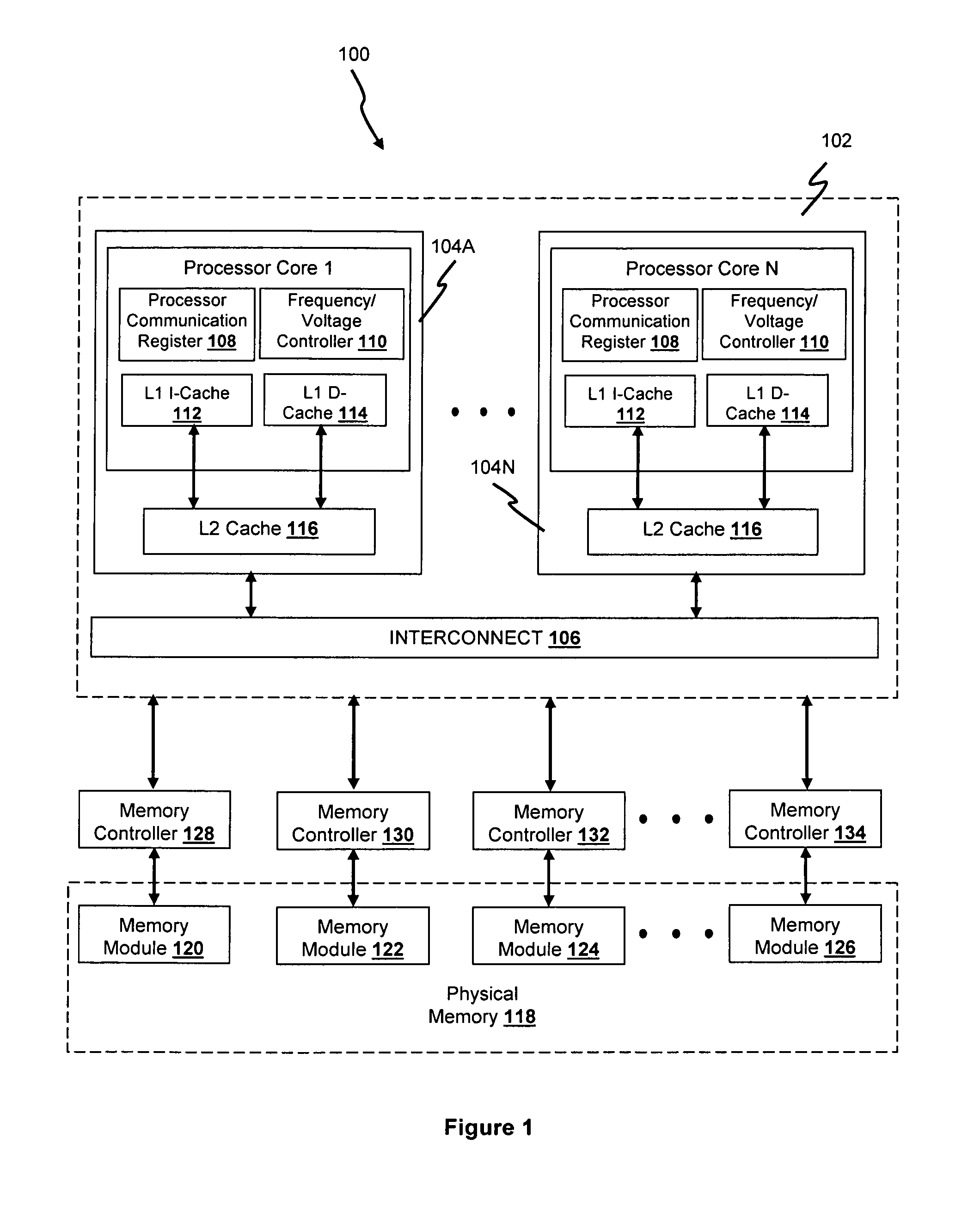

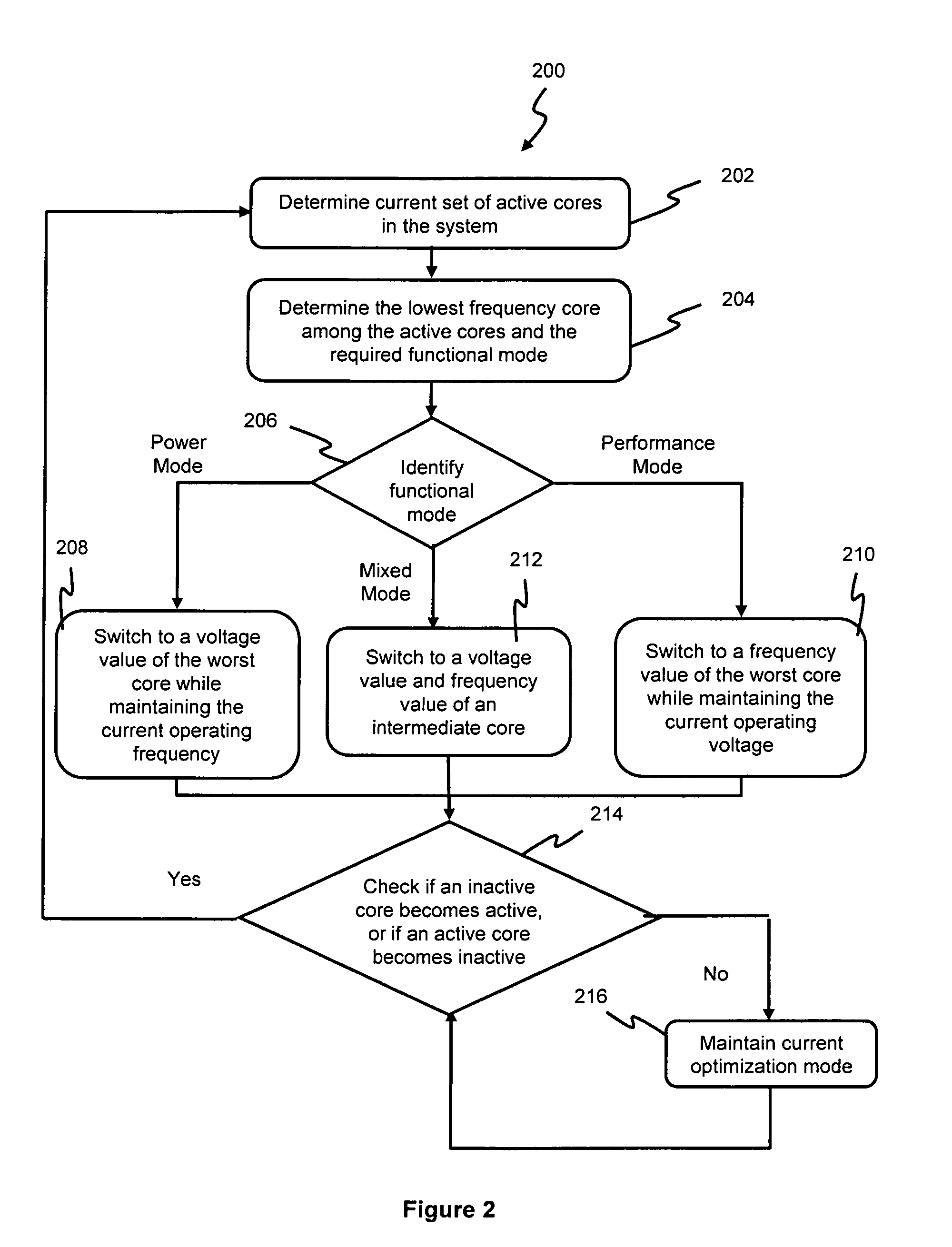

Method for optimizing voltage-frequency setup in multi-core processor systems

InactiveUS20100169609A1Program control using wired connectionsVolume/mass flow measurementFrequency characteristicMixed mode

A method for dynamically operating a multi-core processor system is provided. The method involves ascertaining currently active processor cores, identifying a currently active processor core having a lowest operating frequency, and adjusting at least one operational parameter according to voltage-frequency characteristics corresponding to the identified processor core to fulfill a predefined functional mode, e.g. power optimization mode, performance optimization mode and mixed mode.

Owner:INTEL CORP

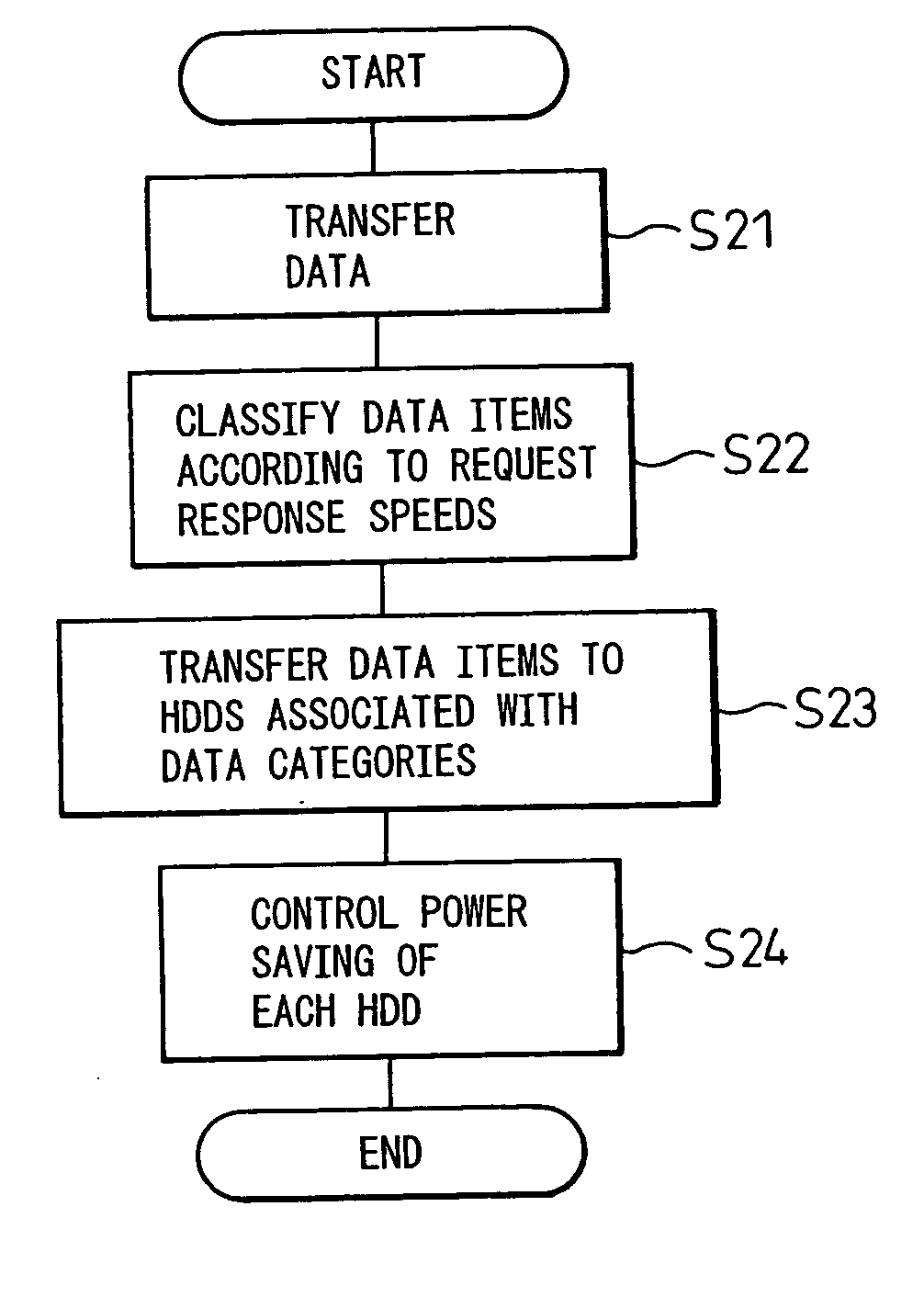

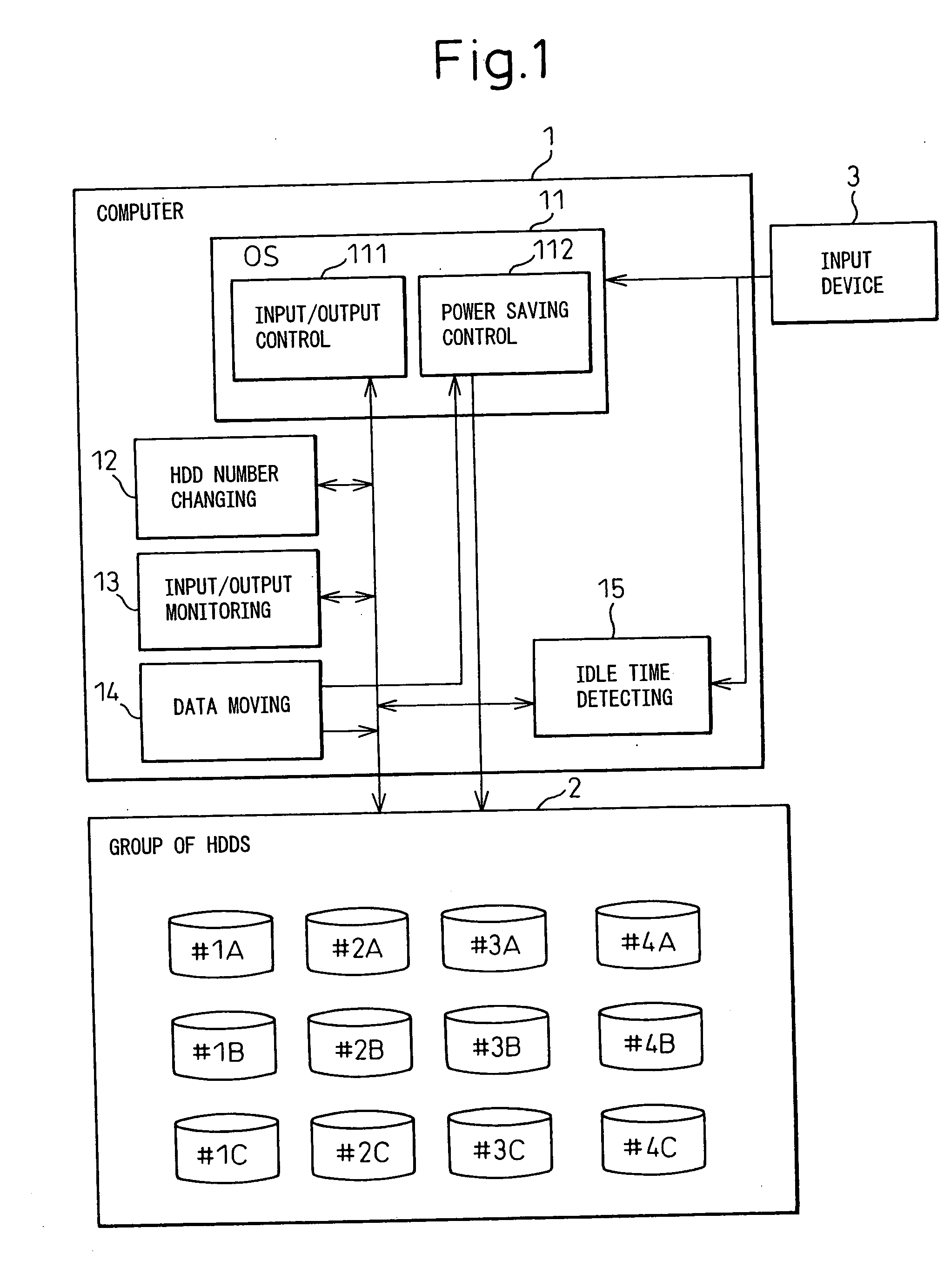

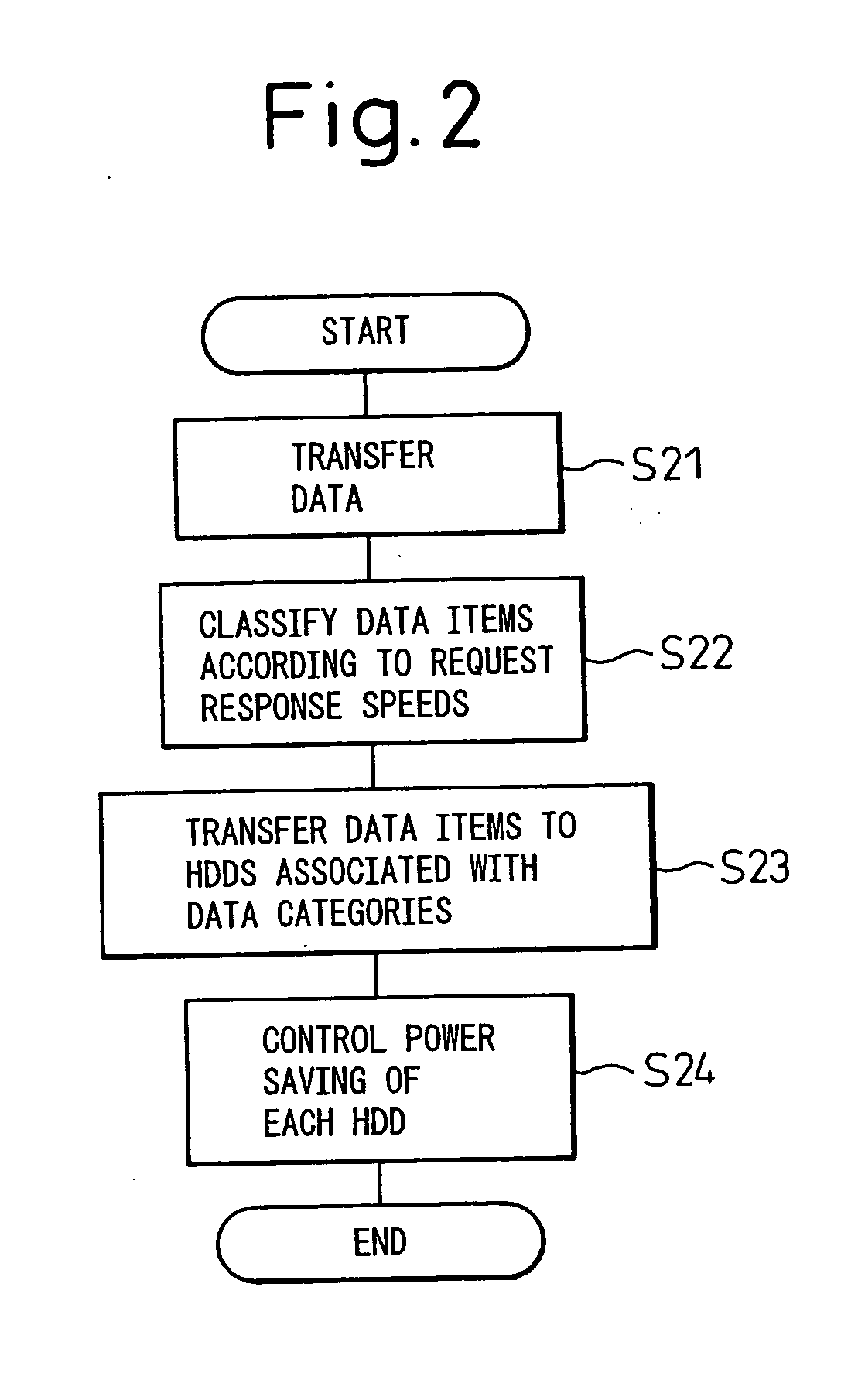

Power saving control system and power saving control method

InactiveUS20050273638A1Save energyInput/output to record carriersDriving/moving recording headsControl systemAccess frequency

Provided is a power saving control method and system for data storage devices or electrical equipment. Herein, data items are divided into groups according to required response times or access frequencies. The groups of data items are allocated to data storage devices or pieces of electrical equipment. A data storage device or electrical equipment to which data that may be accessed using a long response time at a low access frequency is set to a power-saving mode of a higher level. Consequently, the data storage devices or pieces of electrical equipment are provided with power-saving features of different levels. Eventually, energy saving can be achieved more efficiently.

Owner:FUJITSU LTD

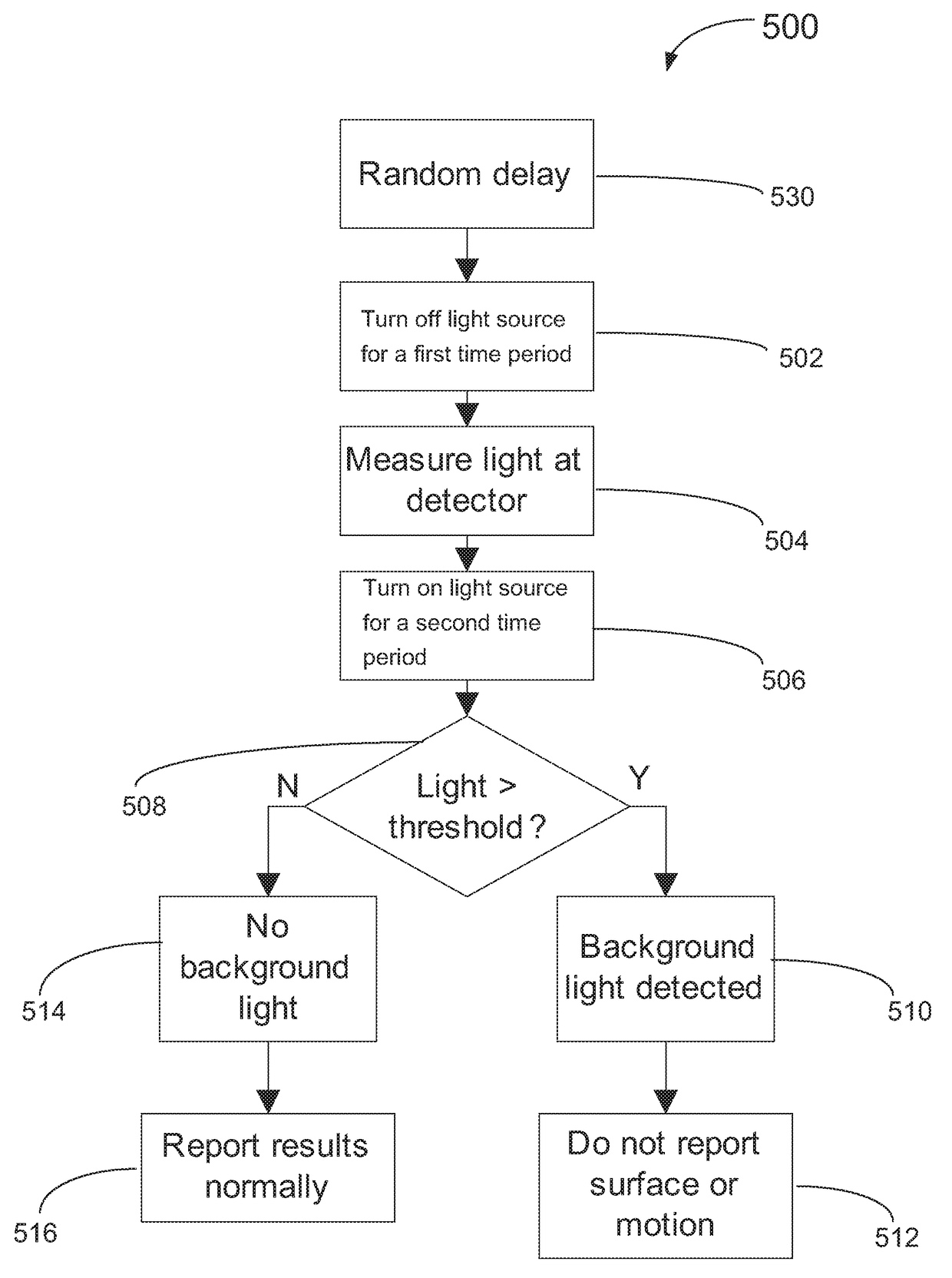

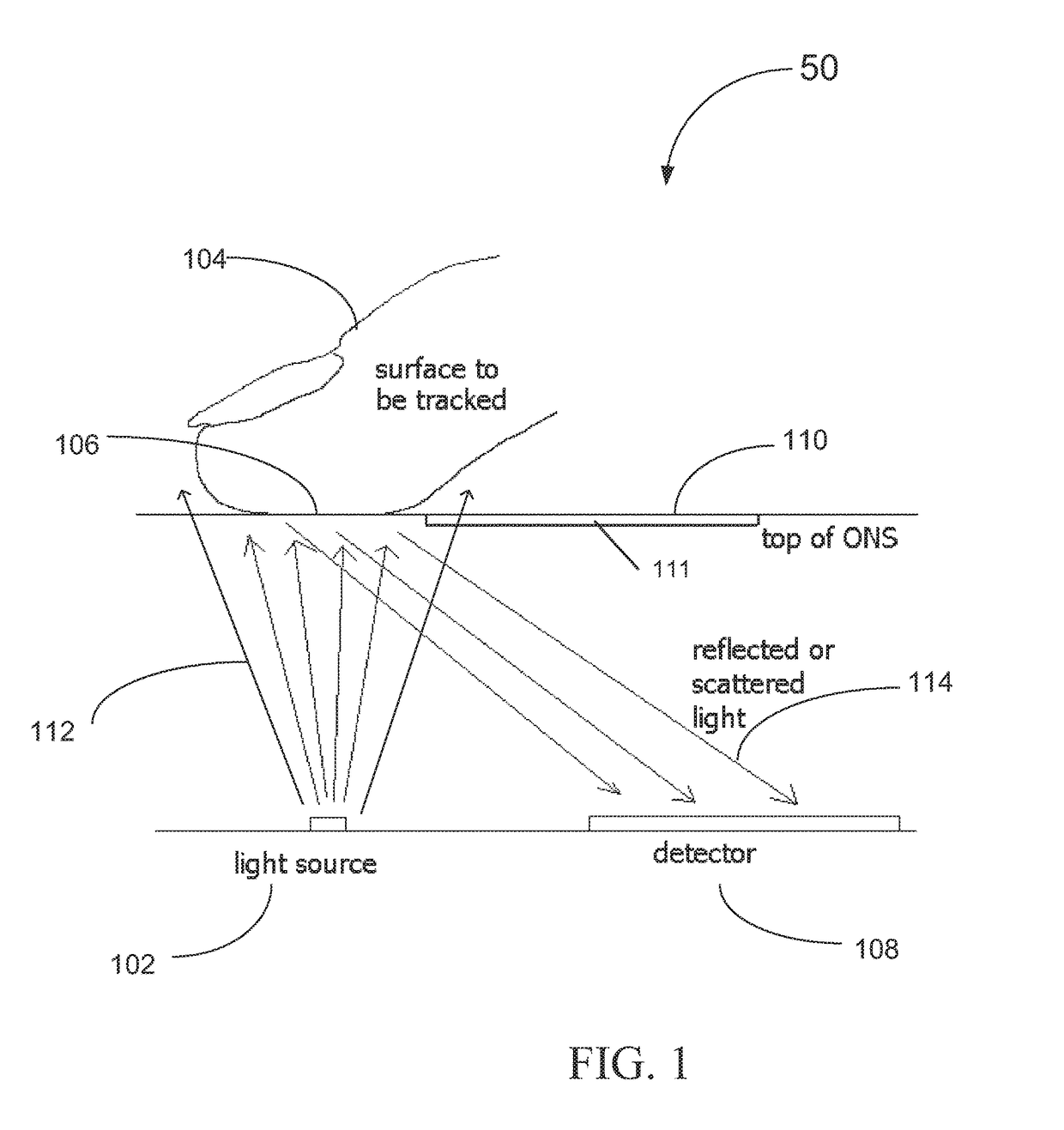

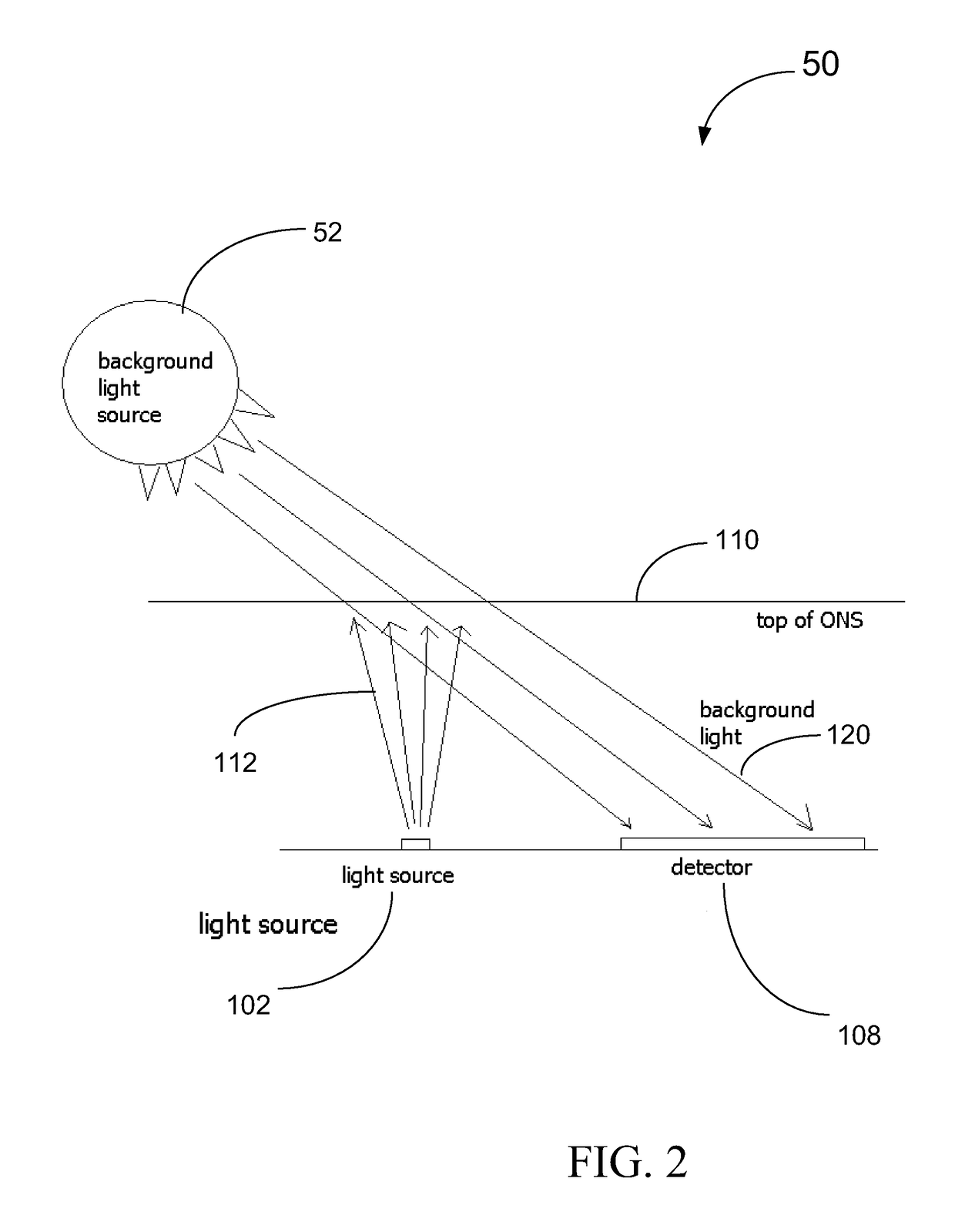

Optical navigation systems and methods for background light detection and avoiding false detection and auto-movement

ActiveUS9927915B2Complicates industrial designImprove performancePower supply for data processingSingle machine energy consumption reductionNavigation systemFalse detection

A method of operating an optical navigation system which includes disabling a light source to measure the ambient or external light level, comparing the measurement to a threshold level to determine whether the ambient light would cause false detection and light induced motion, and adjusting sensing parameter(s) to mitigate the effect of the ambient light.

Owner:CYPRESS SEMICON CORP

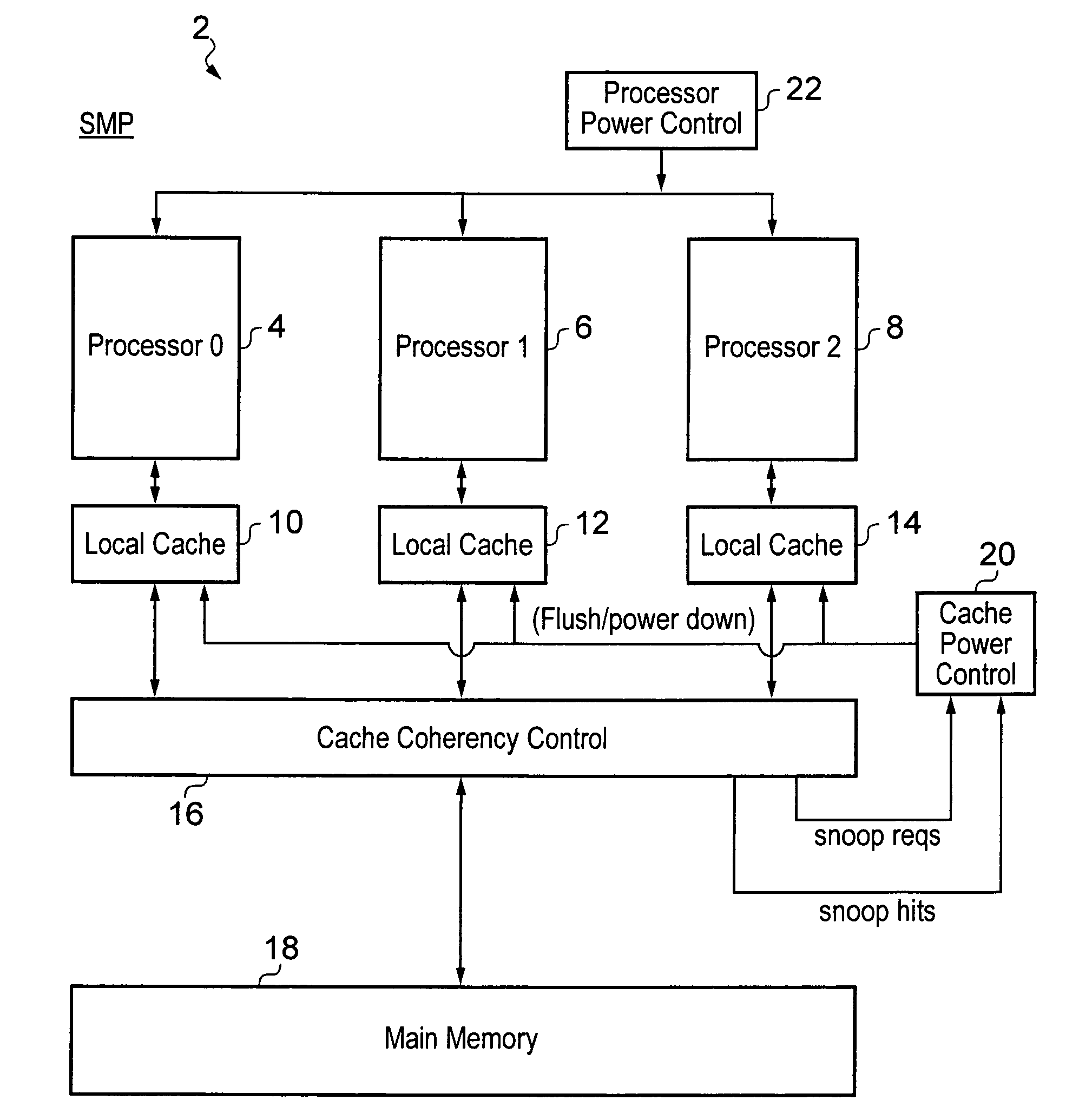

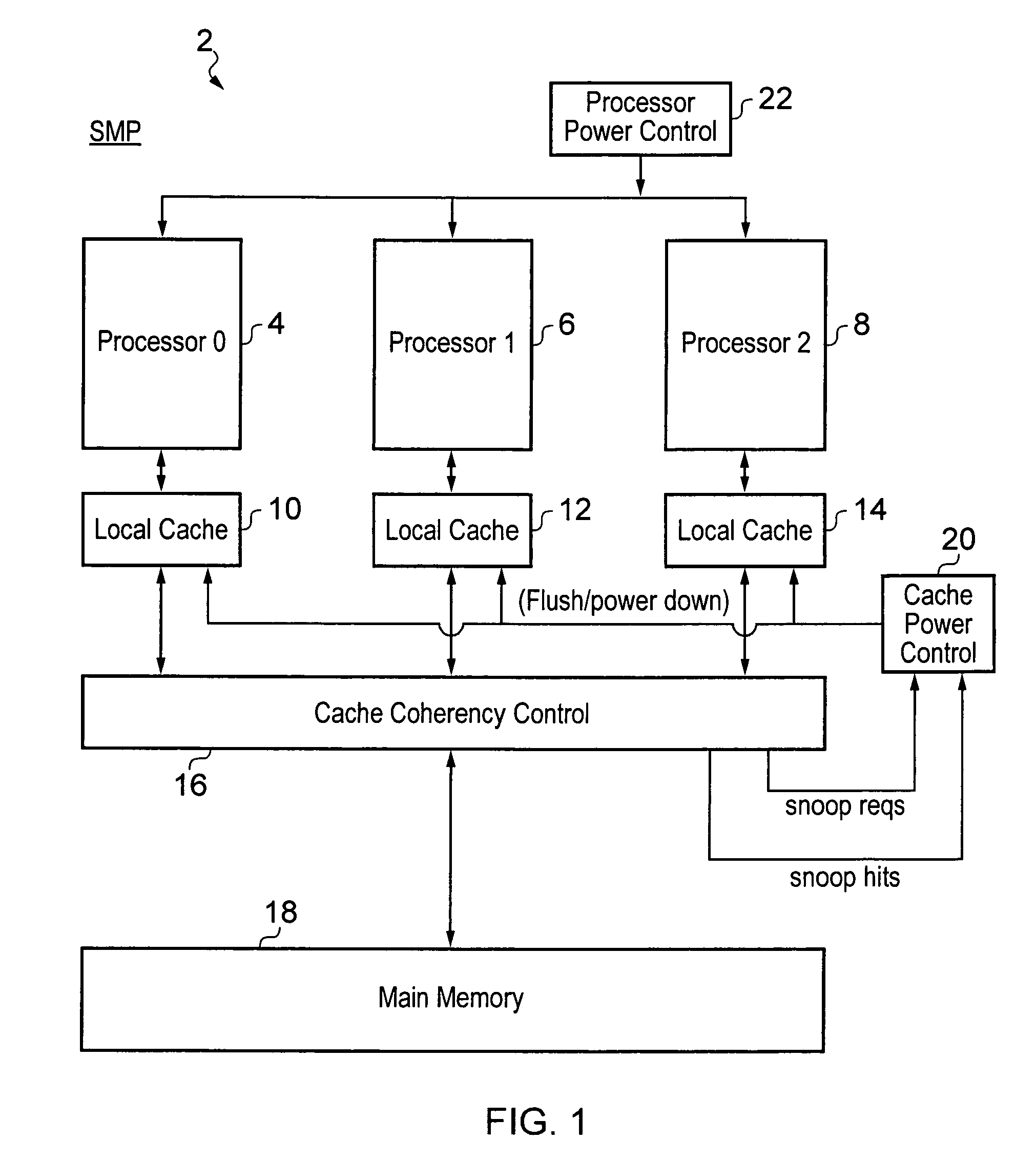

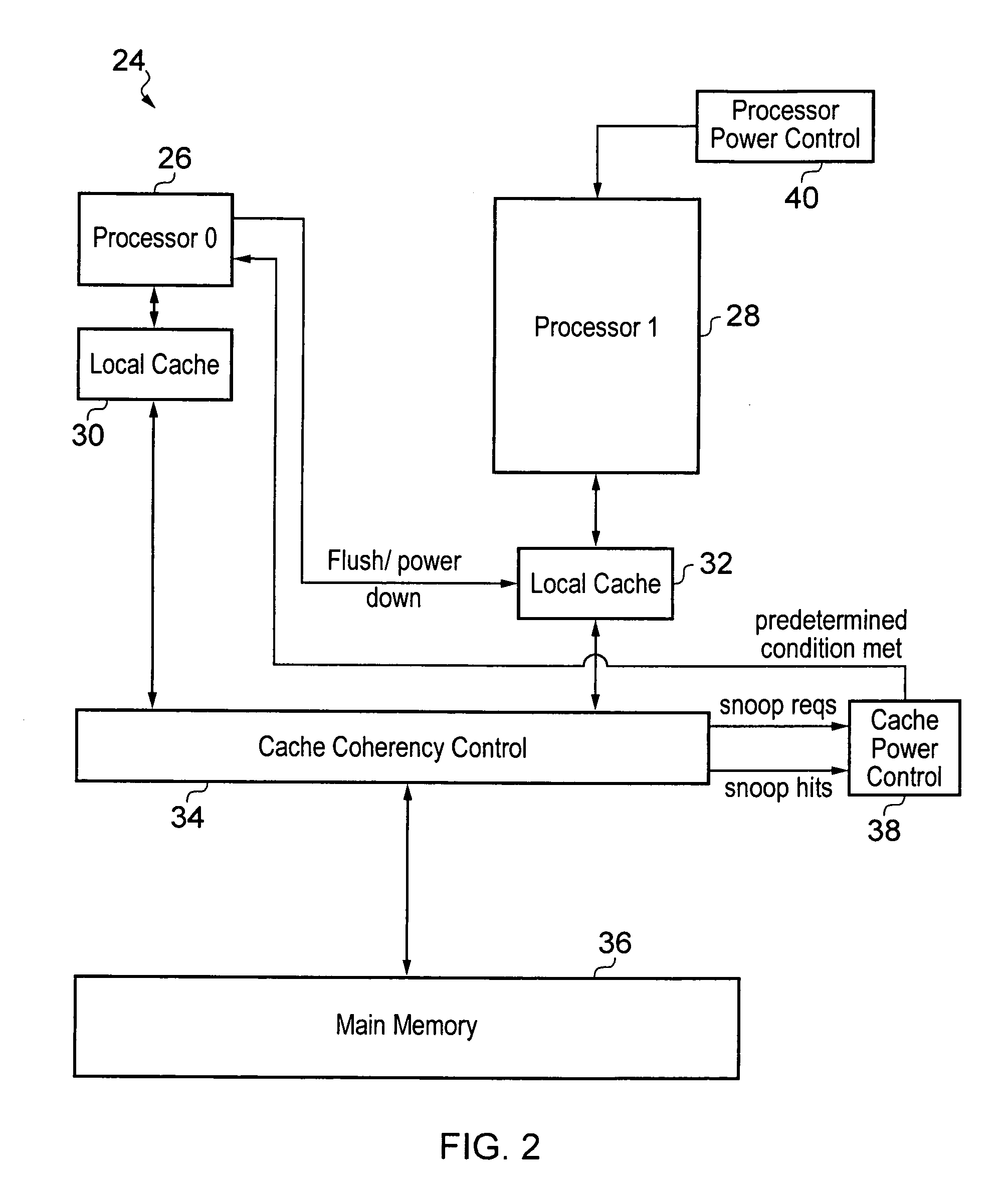

Local cache power control within a multiprocessor system

ActiveUS20100185821A1Great degreeMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemMulti processor

A data processing system including a plurality of processors 4, 6, 8 each having a local cache memory 10, 12, 14 is provided. A cache coherency controller 16 serves to maintain cache coherency between the local cache memories 10, 12, 14. When one of the processors 4, 6, 8 is placed into a low power state its associated local cache memory 10, 12, 14 is maintained in a state in which the data it is holding is accessible to the cache coherency controller 16 until a predetermined condition has been met whereupon the local cache memory 10, 12, 14 concerned is placed into a low power state. The predetermined condition can take a variety of different forms such as the rate of snoop hits falling below a threshold value, the ratio of snooping hits to snoop requests falling below a threshold value, a predetermined number of clock cycles passing since the associated processor for that local cache memory was powered down as well as other possibilities.

Owner:ARM LTD

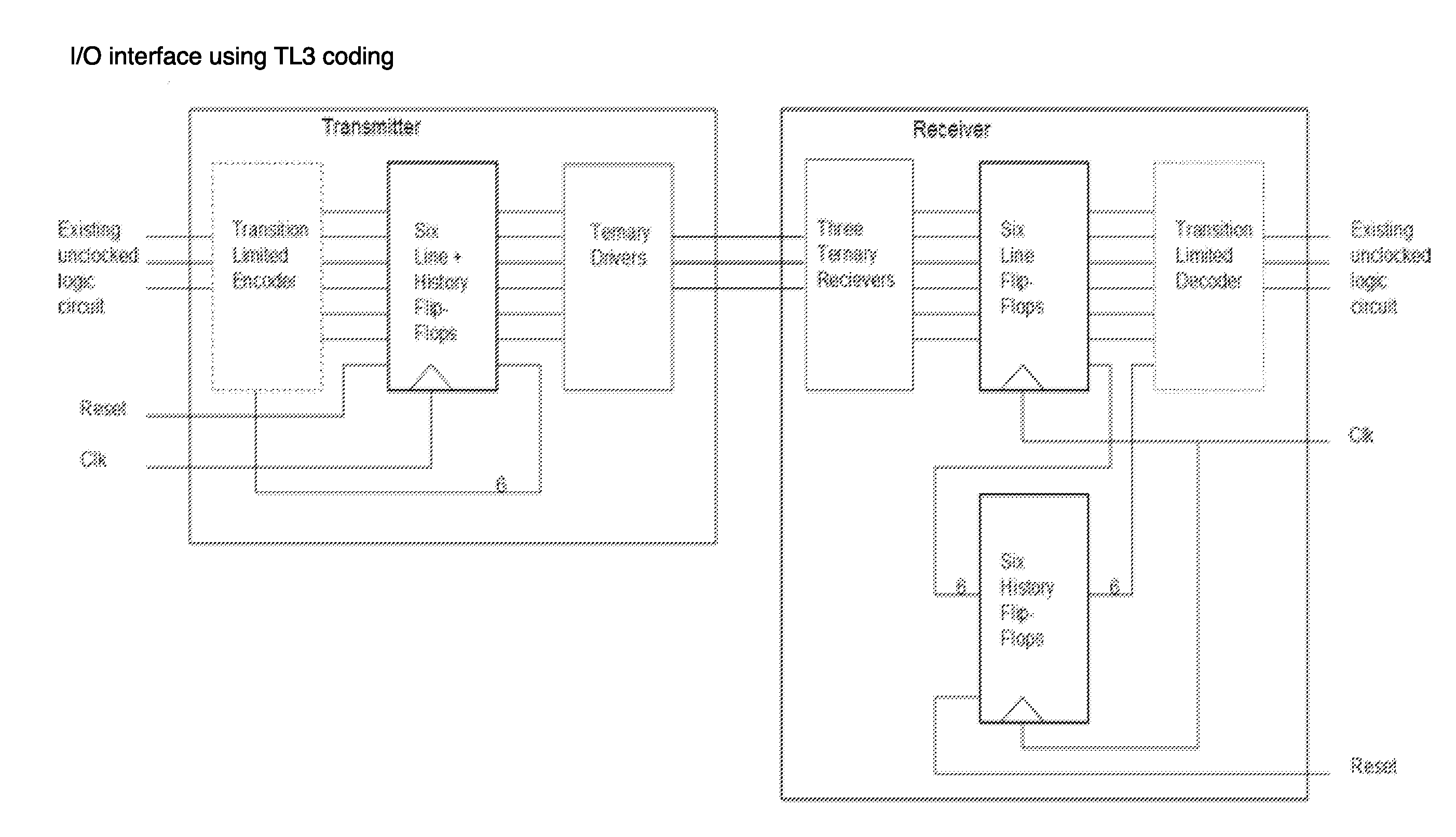

Methods and Systems for Chip-to-Chip Communication with Reduced Simultaneous Switching Noise

ActiveUS20150381768A1Increase speedReduce interfacePulse conversionSingle machine energy consumption reductionLatency (engineering)Memory controller

Owner:KANDOU LABS

Information processing apparatus and mode switching method

InactiveUS20100316099A1Save powerSusbset functionality useDigital data processing detailsInformation processingEngineering

Owner:SONY CORP

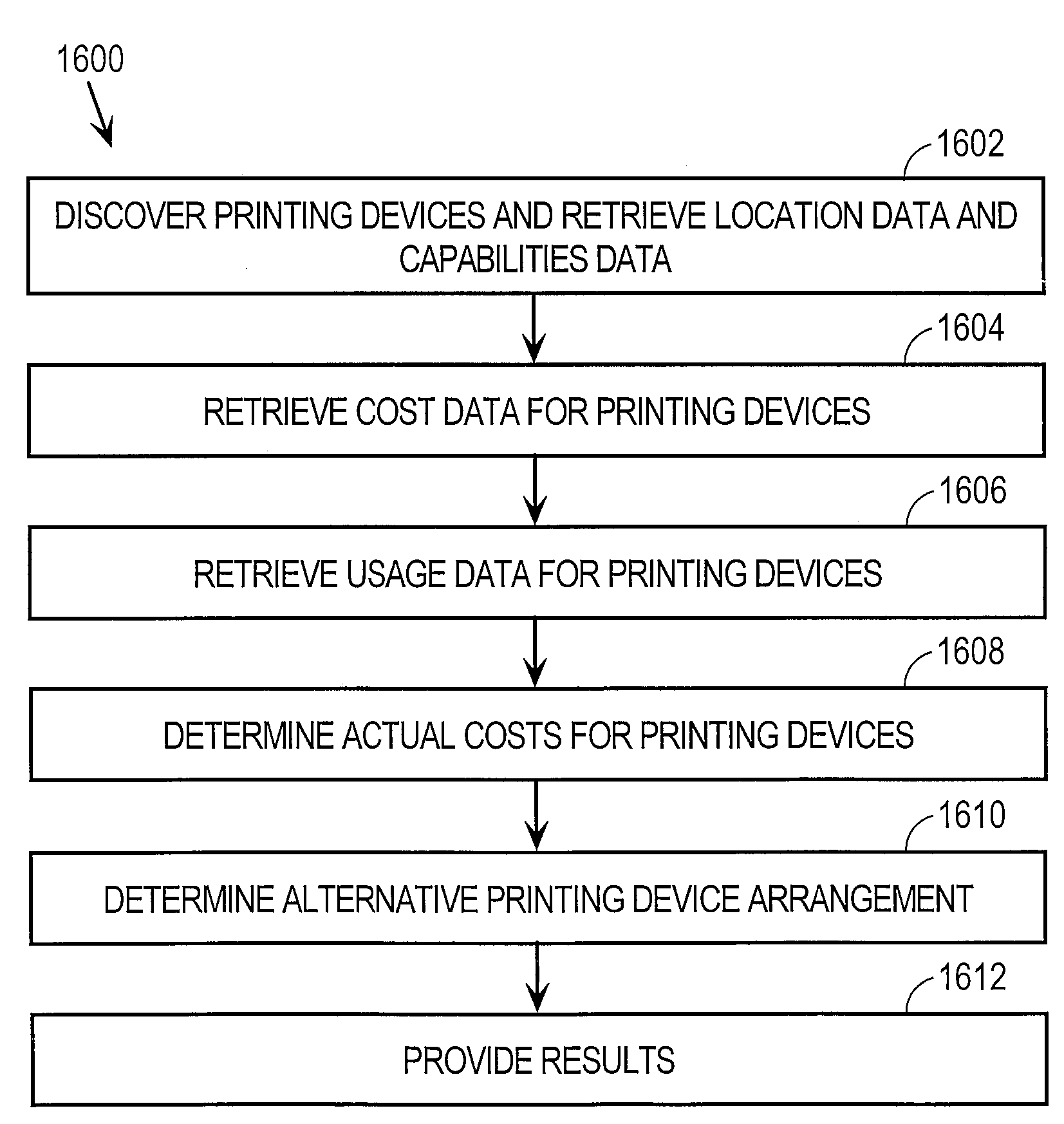

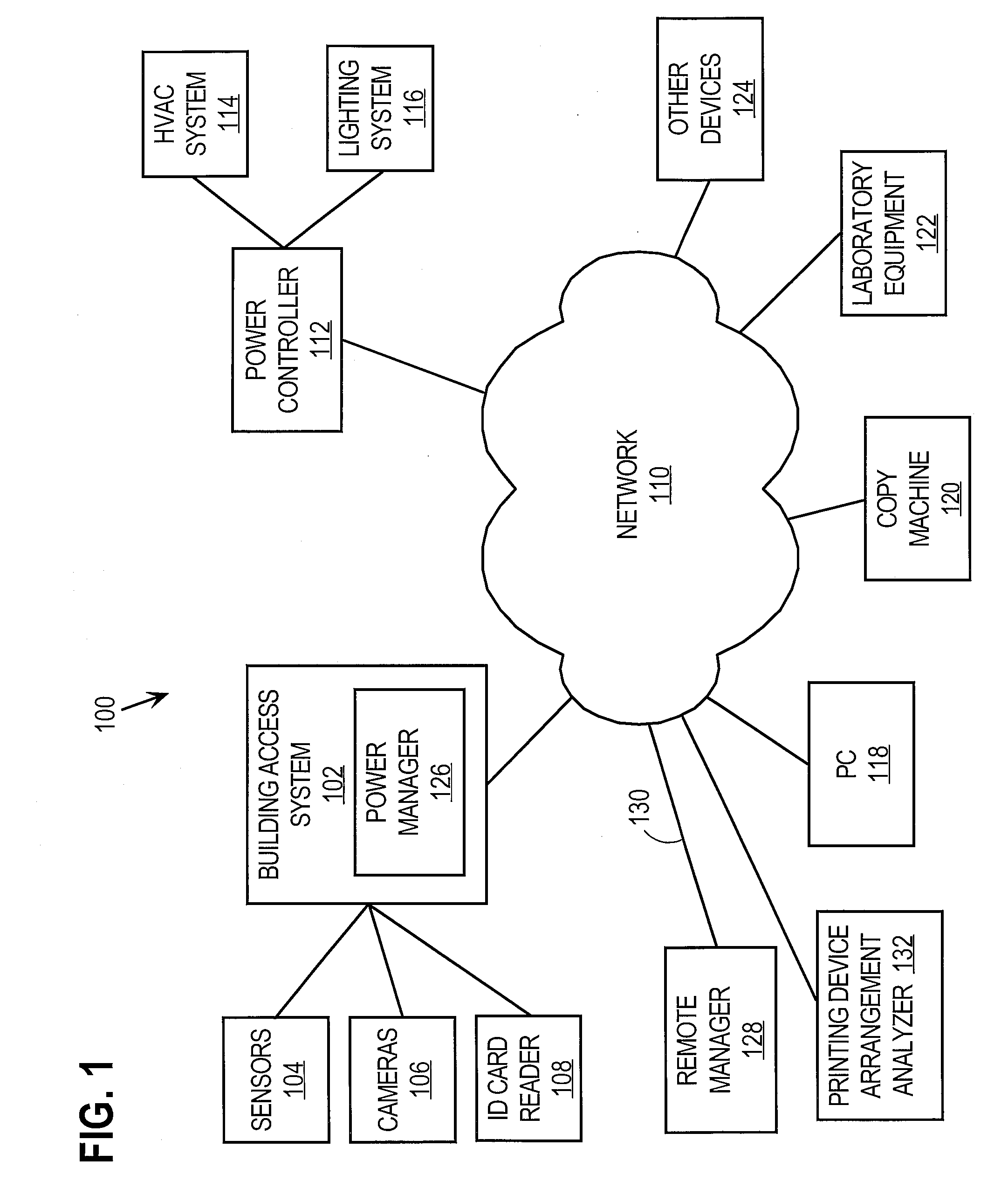

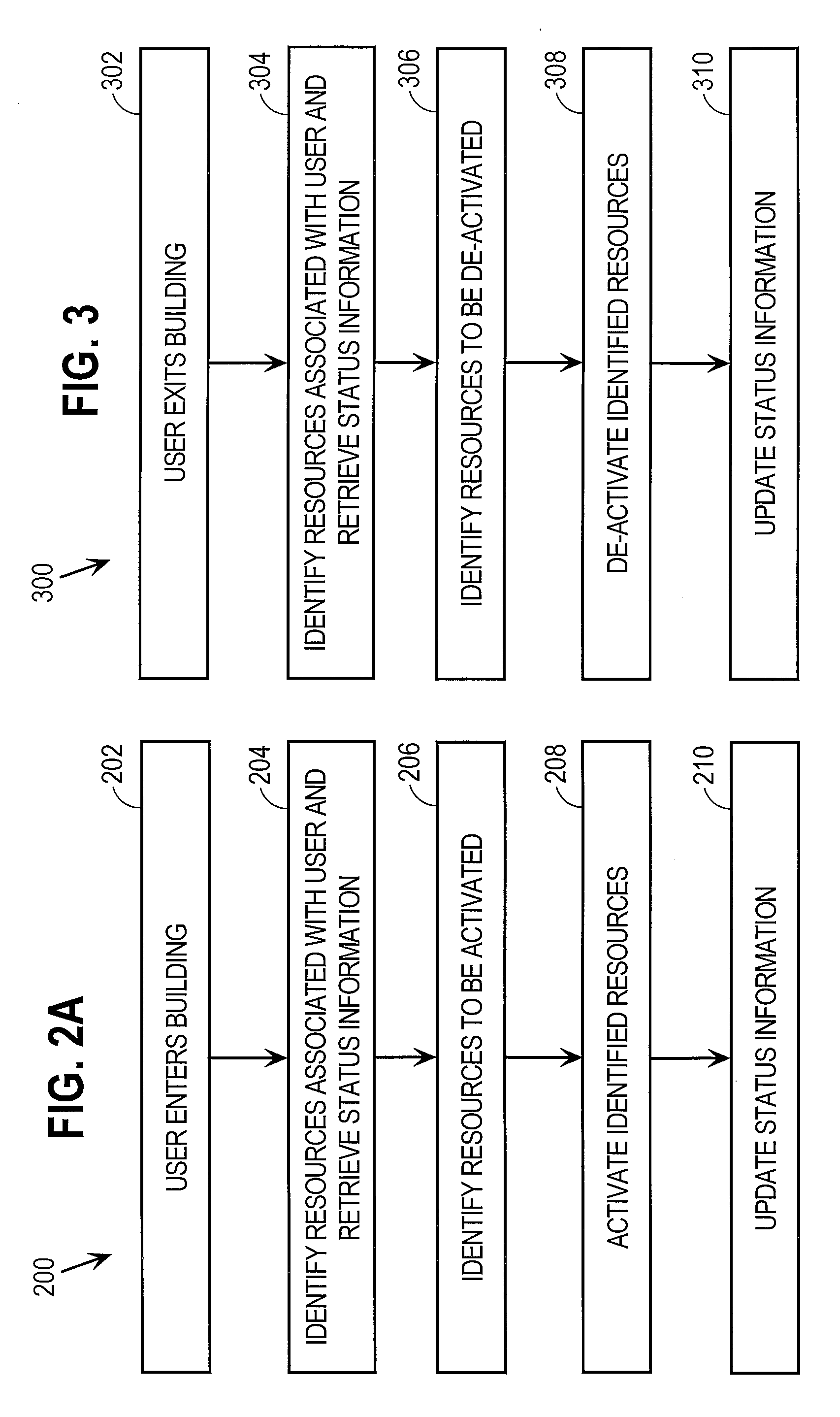

Approach For Determining Alternative Printing Device Arrangements

InactiveUS20100312600A1Low costReduce operating costsDigitally marking record carriersMarket predictionsOperational costsEngineering

According to one embodiment of the invention, an approach is provided for determining alternative printing device arrangements. In general, the geographic locations, usage and costs of an existing set of printing devices are analyzed. A determination is made, based upon this analysis, whether one or more of the existing printing devices can be replaced by one or more replacement printing devices to provide an alternative printing device arrangement that has lower costs. The lower costs may reflect lower operational costs, lower energy costs, lower acquisition costs, or any combination of lower operational costs, lower energy costs and lower acquisition costs.

Owner:RICOH KK

Interconnect that eliminates routing congestion and manages simultaneous transactions

InactiveUS20120036296A1Digital computer detailsDigital storageProtocol for Carrying Authentication for Network AccessRouting congestion

A method, apparatus, and system are described, which generally relate to an integrated circuit having an interconnect. The flow control logic for the interconnect applies a flow control splitting protocol to permit transactions from each initiator thread and / or each initiator tag stream to be outstanding to multiple channels in a single aggregate target at once, and therefore to multiple individual targets within an aggregate target at once. The combined flow control logic and flow control protocol allows the interconnect to manage simultaneous requests to multiple channels in an aggregate target from the same thread or tag at the same time.

Owner:META PLATFORMS TECH LLC

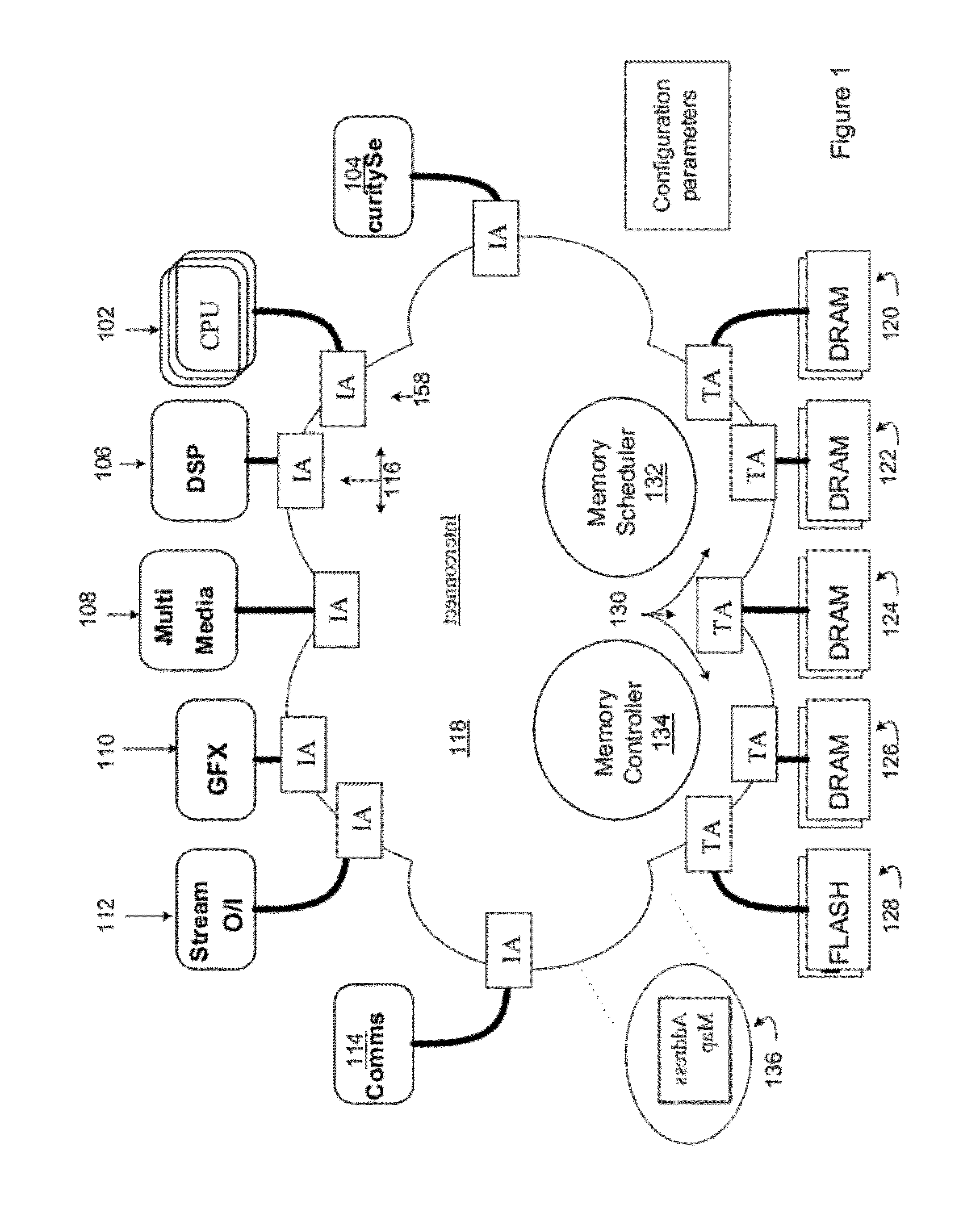

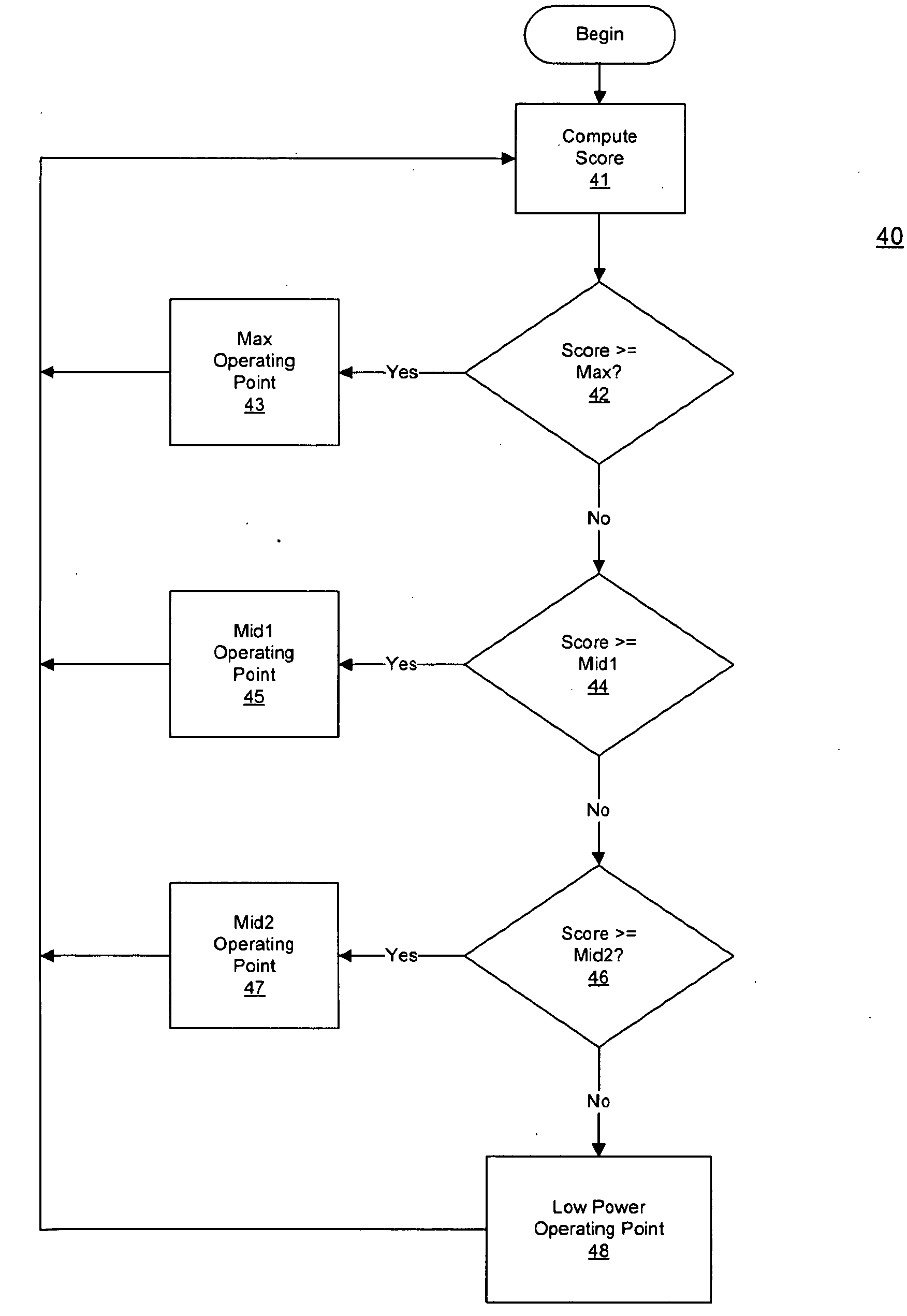

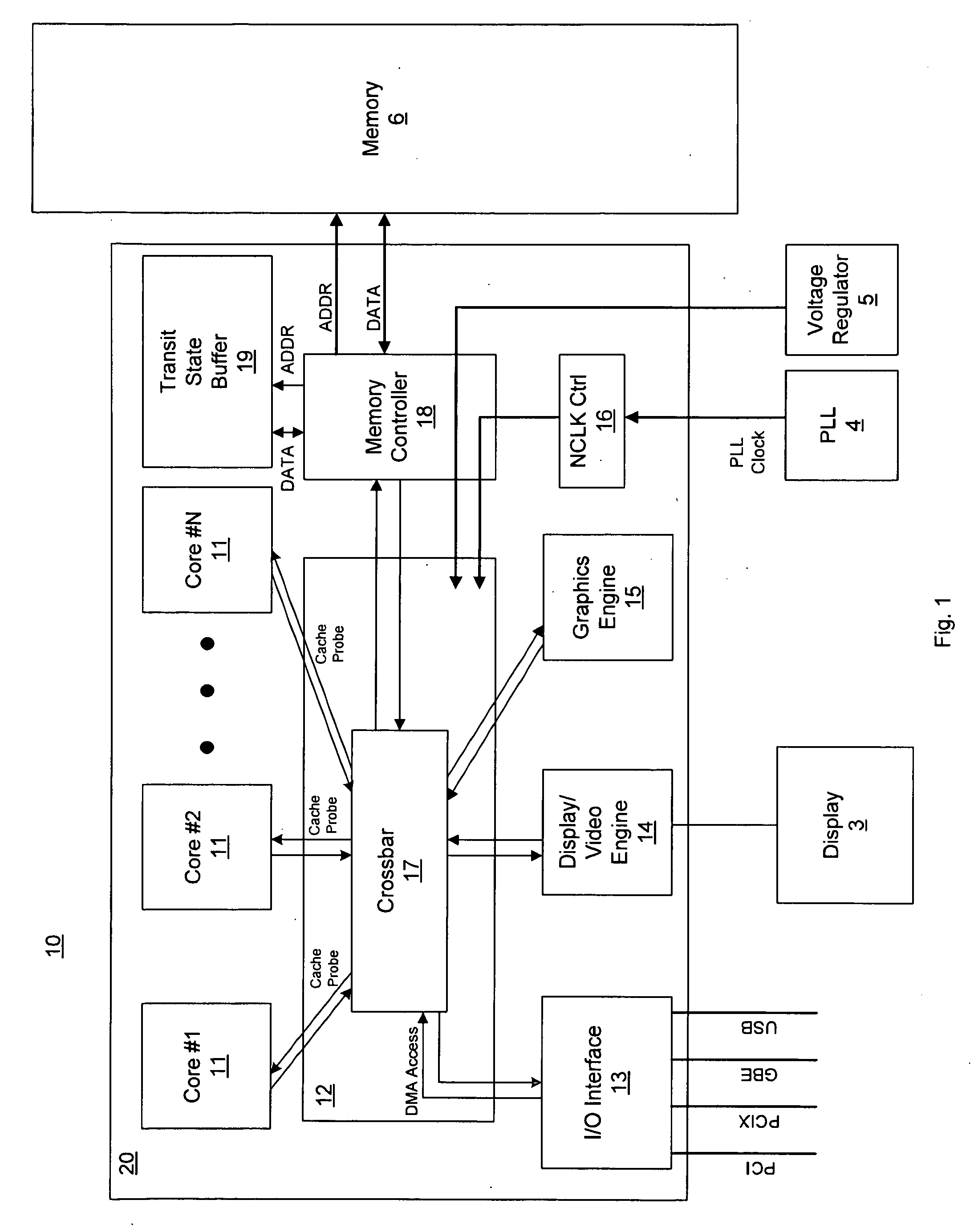

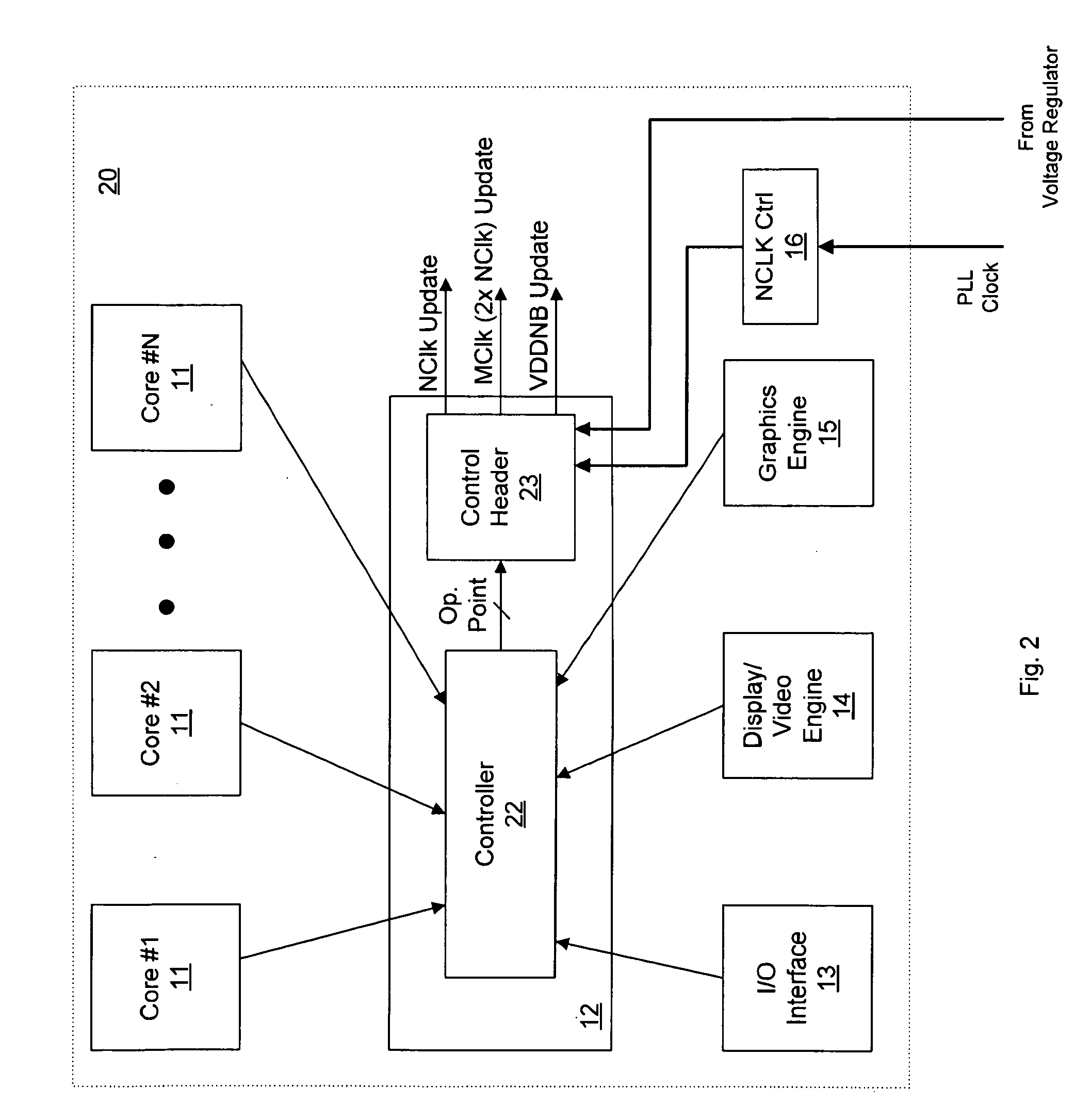

Optimization of application power consumption and performance in an integrated system on a chip

InactiveUS20100162256A1Digital data processing detailsMultiprogramming arrangementsComputer architectureOperating point

A method for determining an operating point of a shared resource. The method includes receiving indications of access demand to a shared resource from each of a plurality of functional units and determining a maximum access demand from among the plurality of functional units based on their respective indications. The method further includes determining a required operating point of the shared resource based on the maximum access demand, wherein the shared resource is shared by each of the plurality of functional units, comparing the required operating point to a present operating point of the shared resource, and changing to the required operating point from the present operating point if the required and present operating points are different.

Owner:GLOBALFOUNDRIES INC +1

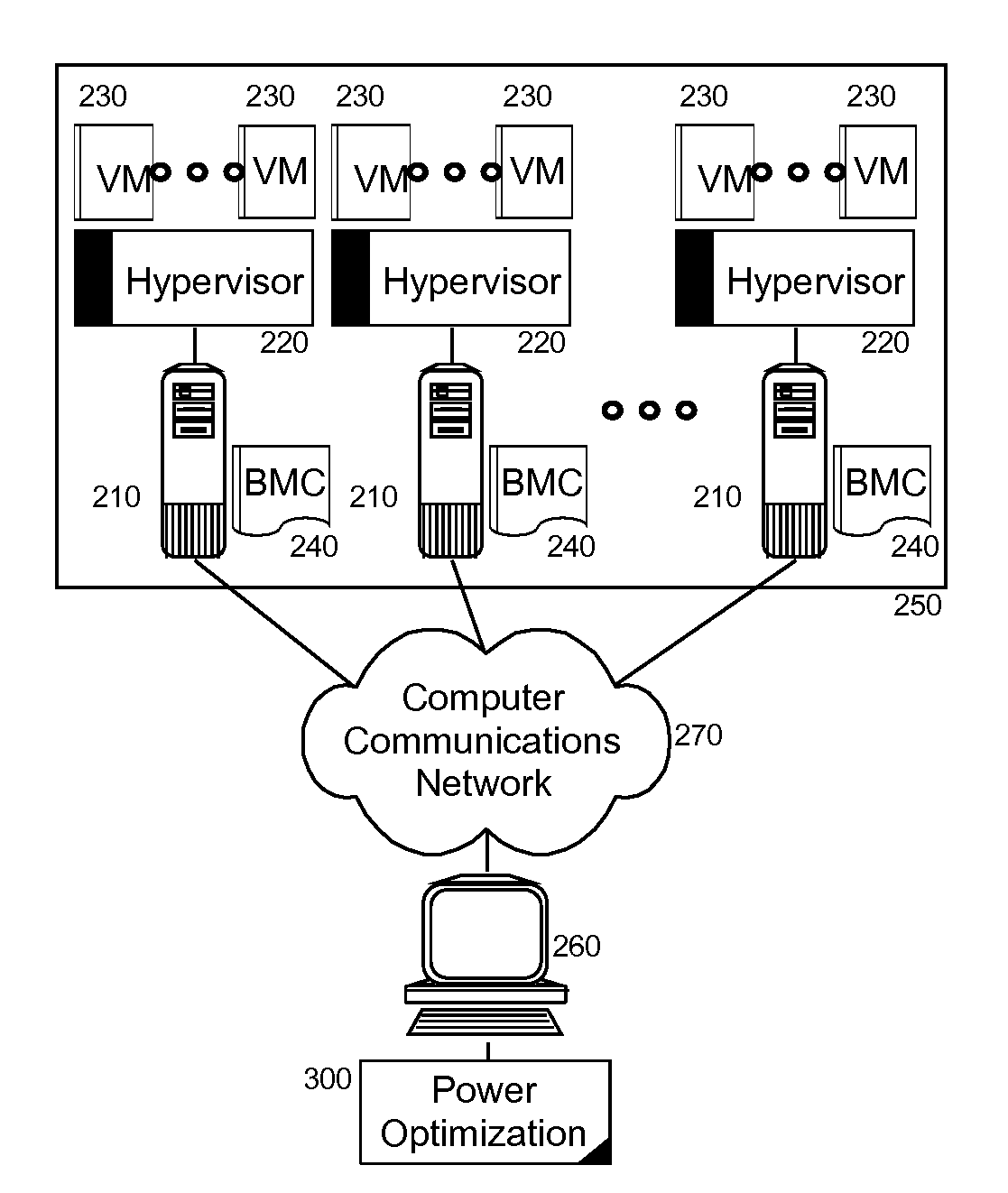

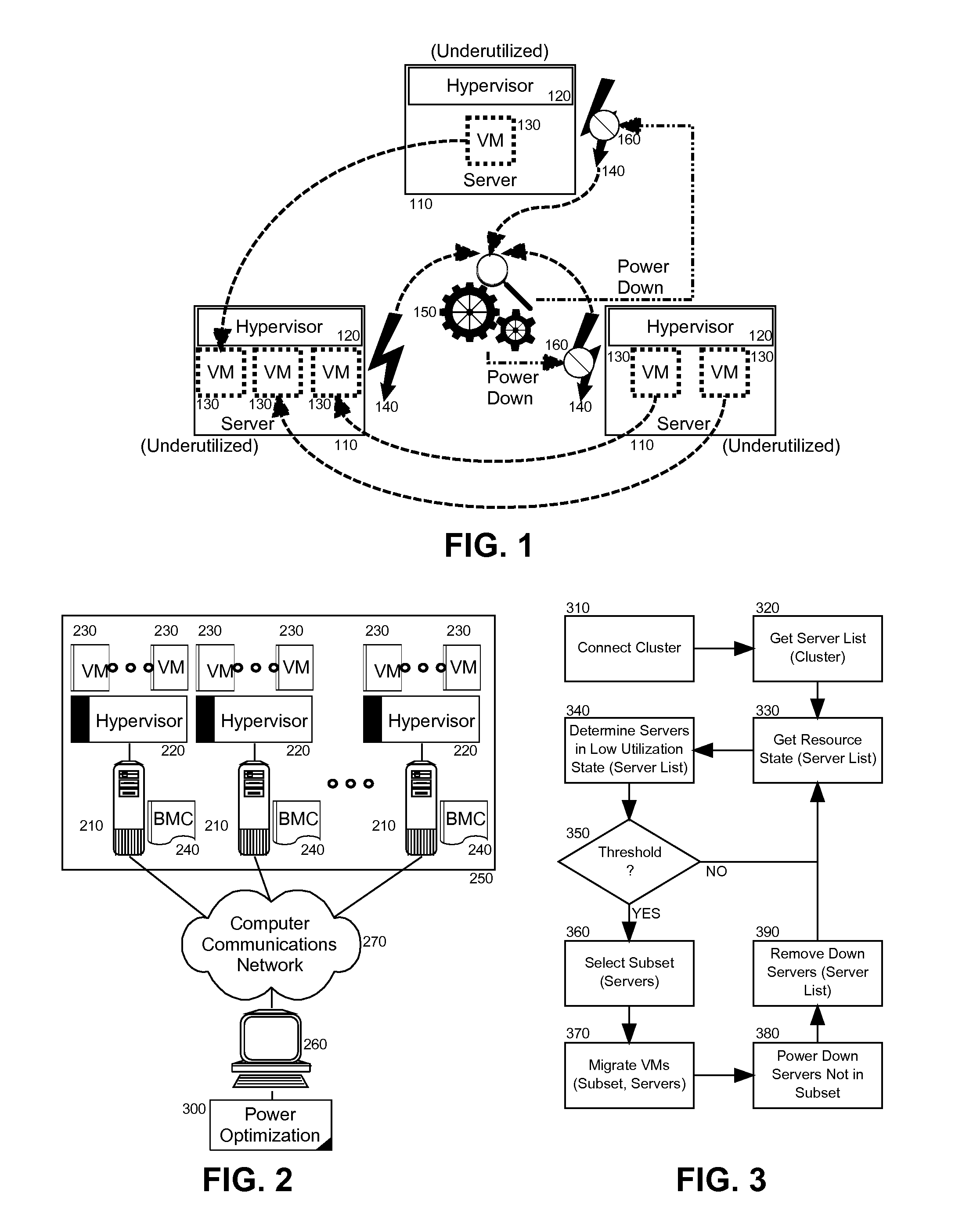

Power optimization via virtualization opportunity

InactiveUS20100115509A1Reduce power consumptionDistributed system energy consumption reductionVolume/mass flow measurementVirtualizationComputer program

Embodiments of the present invention provide a method, system and computer program product for power optimization via virtualization opportunity determination. In an embodiment of the invention, a method for power optimization via virtualization opportunity determination can be provided. The method can include monitoring power utilization in individual server hosts in a cluster and determining a set of the server hosts in the cluster demonstrating low power utilization. The method also can include selecting a subset of server hosts in the set and migrating each VM in non-selected server hosts in the set to the subset of server hosts. Finally, the method can include powering down the non-selected server hosts.

Owner:LENOVO ENTERPRISE SOLUTIONS SINGAPORE

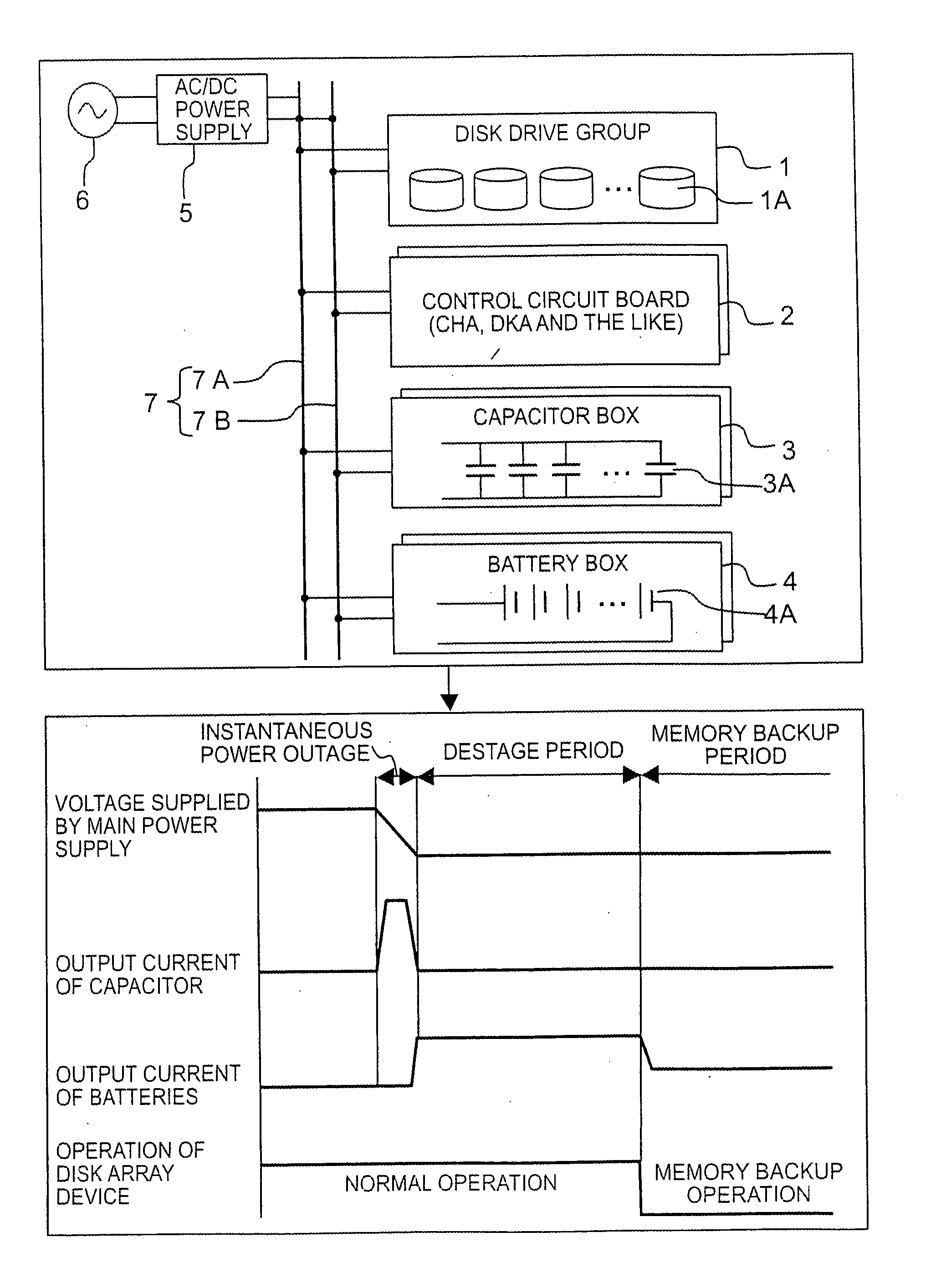

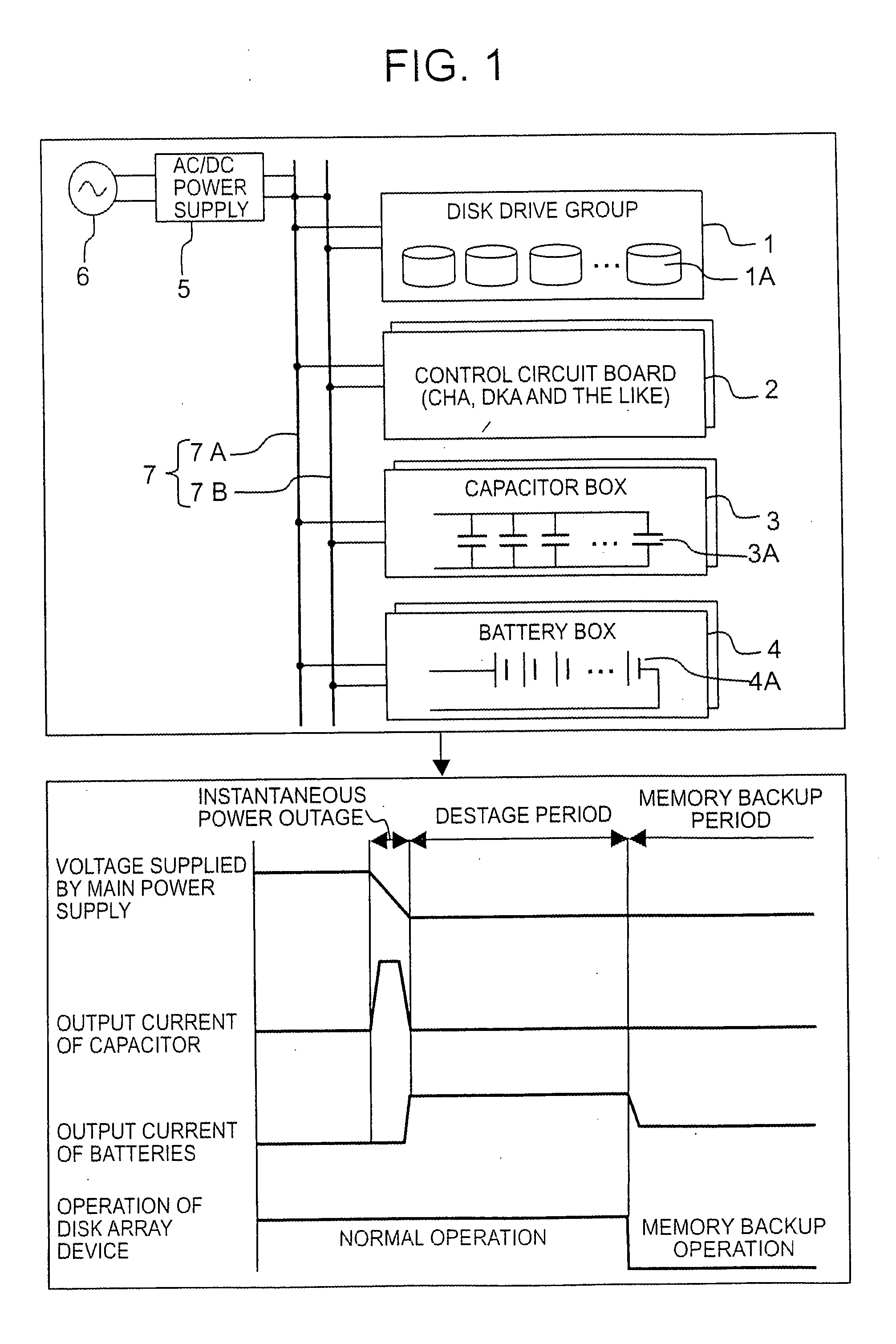

Disk array device and battery output control method for disk array device

InactiveUS20050270927A1Improve reliabilityStable outputCarrier constructional parts dispositionInput/output to record carriersElectricityEngineering

The disk array device supplies appropriate power to various parts in accordance with the operating mode in cases where the output of the main power supply drops. The disk array device adjusts the power from a commercial power source 6 with an AC / DC power supply 5, and supplies this power to a power supply common bus 7. A disk drive group 1 and a control circuit board group 2 constituting electrical loads are respectively connected to the power supply common bus 7. When the supply of power from the main power supply stops, the capacitor box 3 supplies a relatively large current for a short time only, in order to retain data during an instantaneous power outage. Then, the battery boxes 4 supply power to the power supply common bus 7 for a relatively long period of time, in order to perform destage control and memory backup. The battery boxes 4 perform balancing control of the output current in order to suppress variation in the output current value among the battery boxes 4.

Owner:GOOGLE LLC

Popular searches

Heat exchange apparatus Cooling fluid circulation Cooling/ventilation/heating modifications Ventilation systems Acceleration measurement Current supply arrangements Internal/peripheral component protection Speed/acceleration/shock instrument details Substation equipment In satellite navigation networks