Clock control circuit and clock control method

a clock control and clock technology, applied in the direction of pulse technique, oscillation generator, generating/distributing signals, etc., to achieve the effect of reducing phase error to a major degr

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

second embodiment

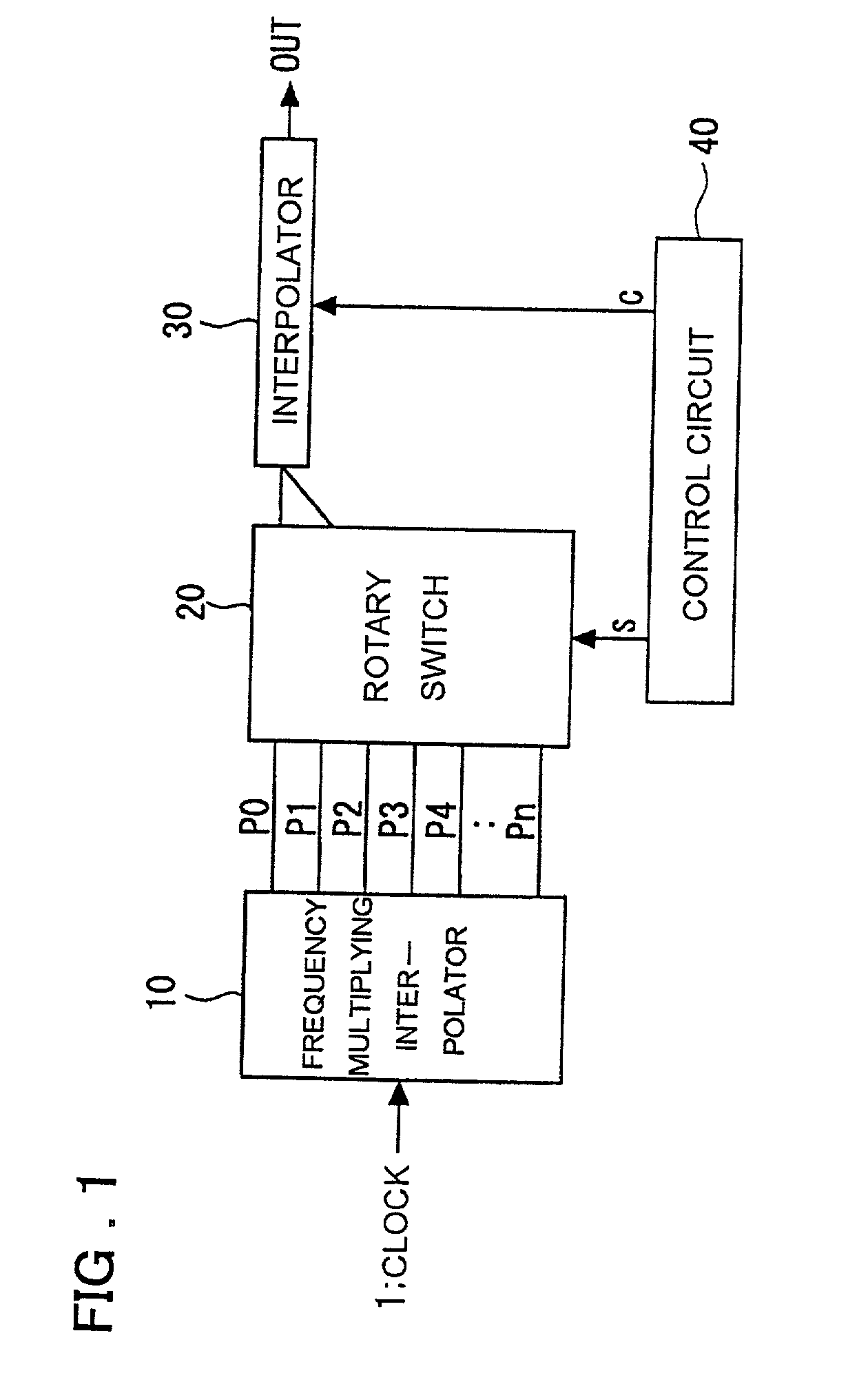

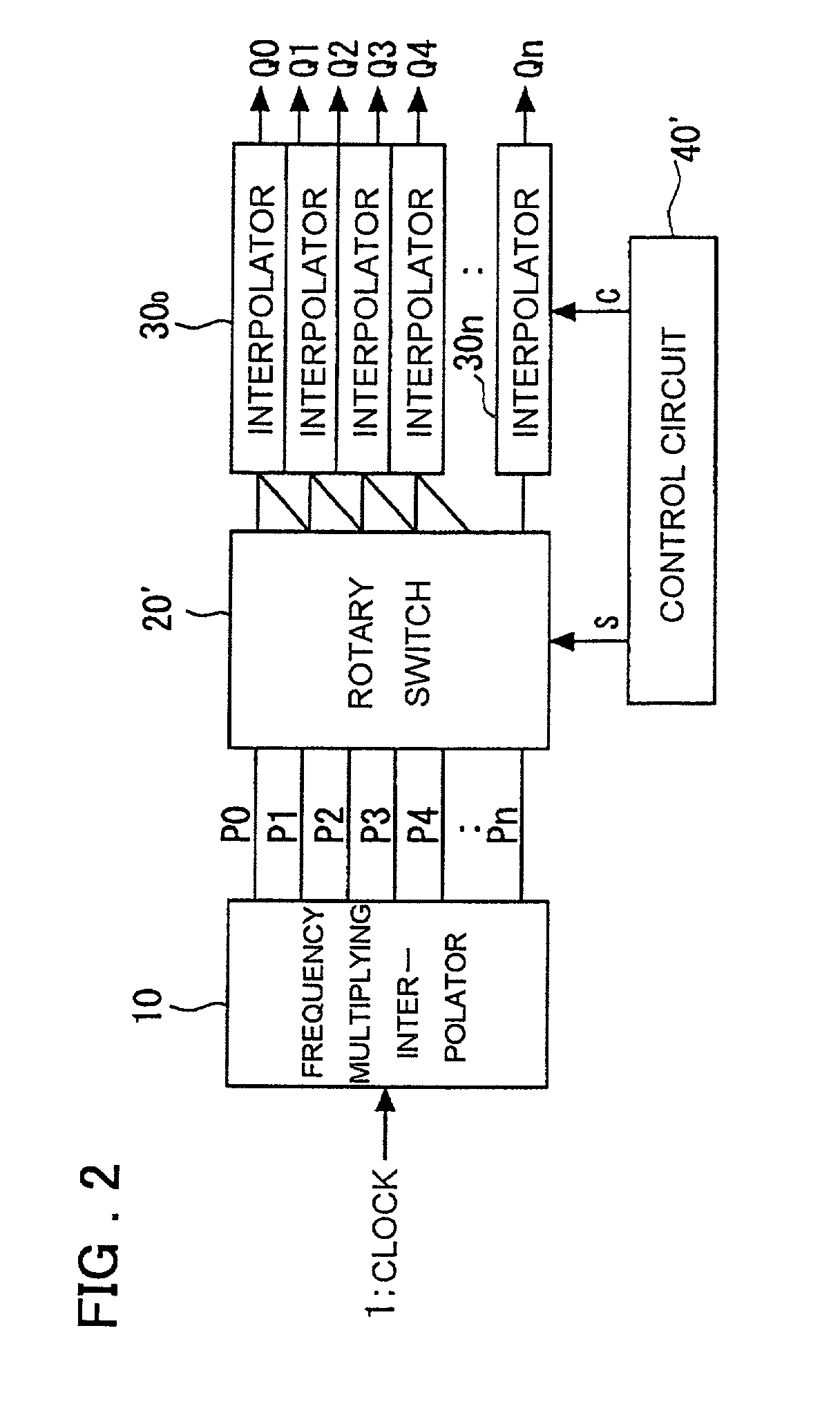

[0134] FIG. 2 is a block diagram illustrating the structure of the present invention;

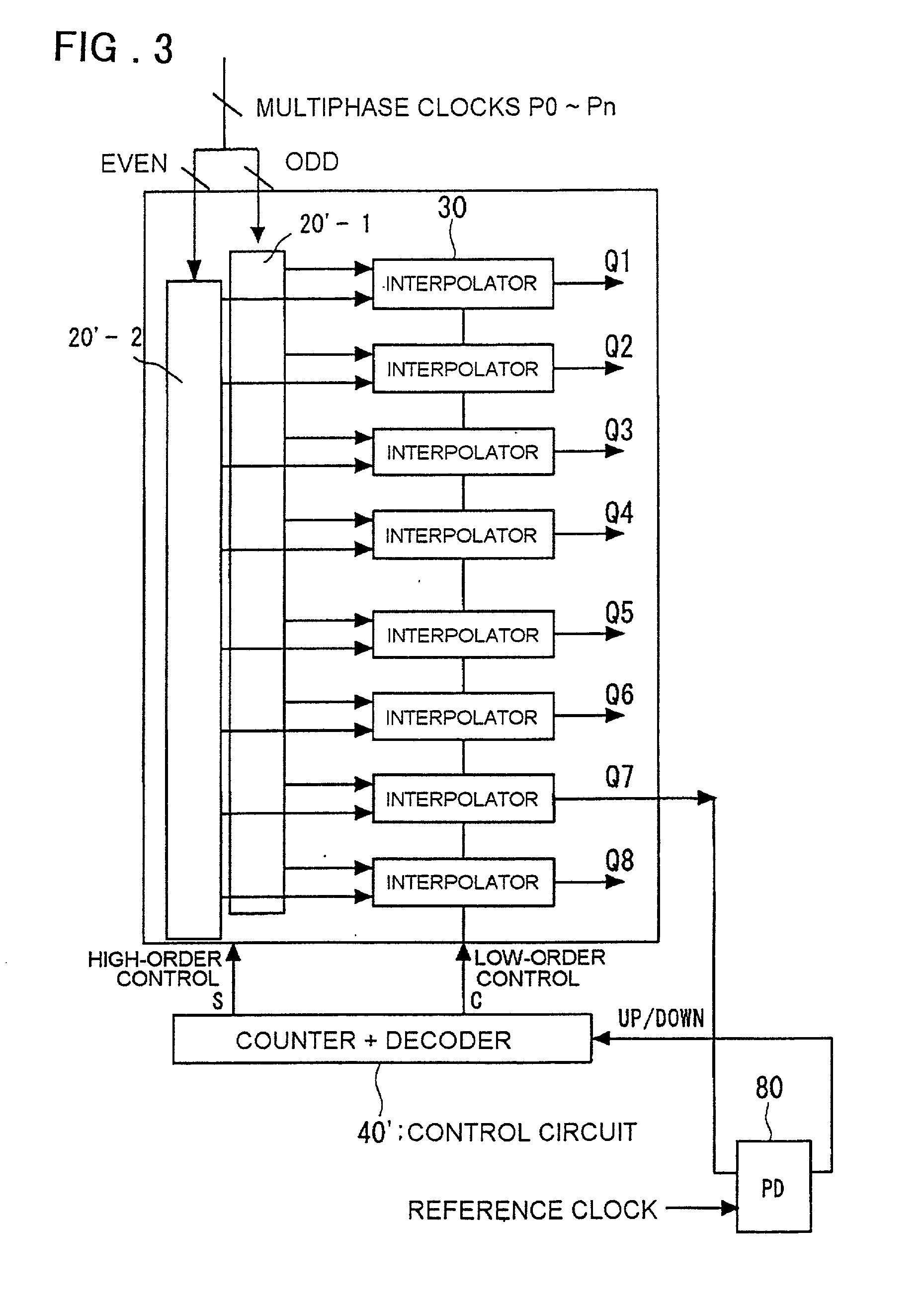

[0135] FIG. 3 is a block diagram illustrating the structure of the second embodiment of the present invention;

[0136] FIG. 4 is a block diagram illustrating the structure of a frequency multiplying interpolator according to an embodiment of the present invention;

[0137] FIG. 5 is a block diagram illustrating the structure of a frequency multiplying interpolator according to an embodiment of the present invention;

[0138] FIGS. 6(a), (b) and (c) are diagrams illustrating the structure of a 4-phase-clock frequency multiplying circuit according to an embodiment of the present invention;

[0139] FIG. 7 is a diagram showing the timing waveforms of the 4-phase-clock frequency multiplying circuit according to the embodiment of the present invention shown in FIG. 6;

[0140] FIGS. 8(a) and (b) diagrams showing the structures of timing-difference dividing circuits of the 4-phase-clock frequency multiplying circuit ac...

third embodiment

[0147] FIG. 15 is a block diagram illustrating the structure of the present invention;

[0148] FIG. 16 is a block diagram illustrating the structures of a switch and interpolator according to the third embodiment of the present invention;

[0149] FIG. 17 is a diagram showing an example of the layout of a 16-step interpolator according to an embodiment of the present invention;

fourth embodiment

[0150] FIG. 18 is a block diagram illustrating the present invention;

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More