Logic gate cell

a logic gate and cell technology, applied in the field of logic gate cells, can solve the problems of poor area utilization, cell height layout, and cell area, and achieve the effect of low power consumption and high area utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiments

[0175] Other embodiments of the present invention will be now explained. The following embodiments correspond to any of Claims 1 to 24.

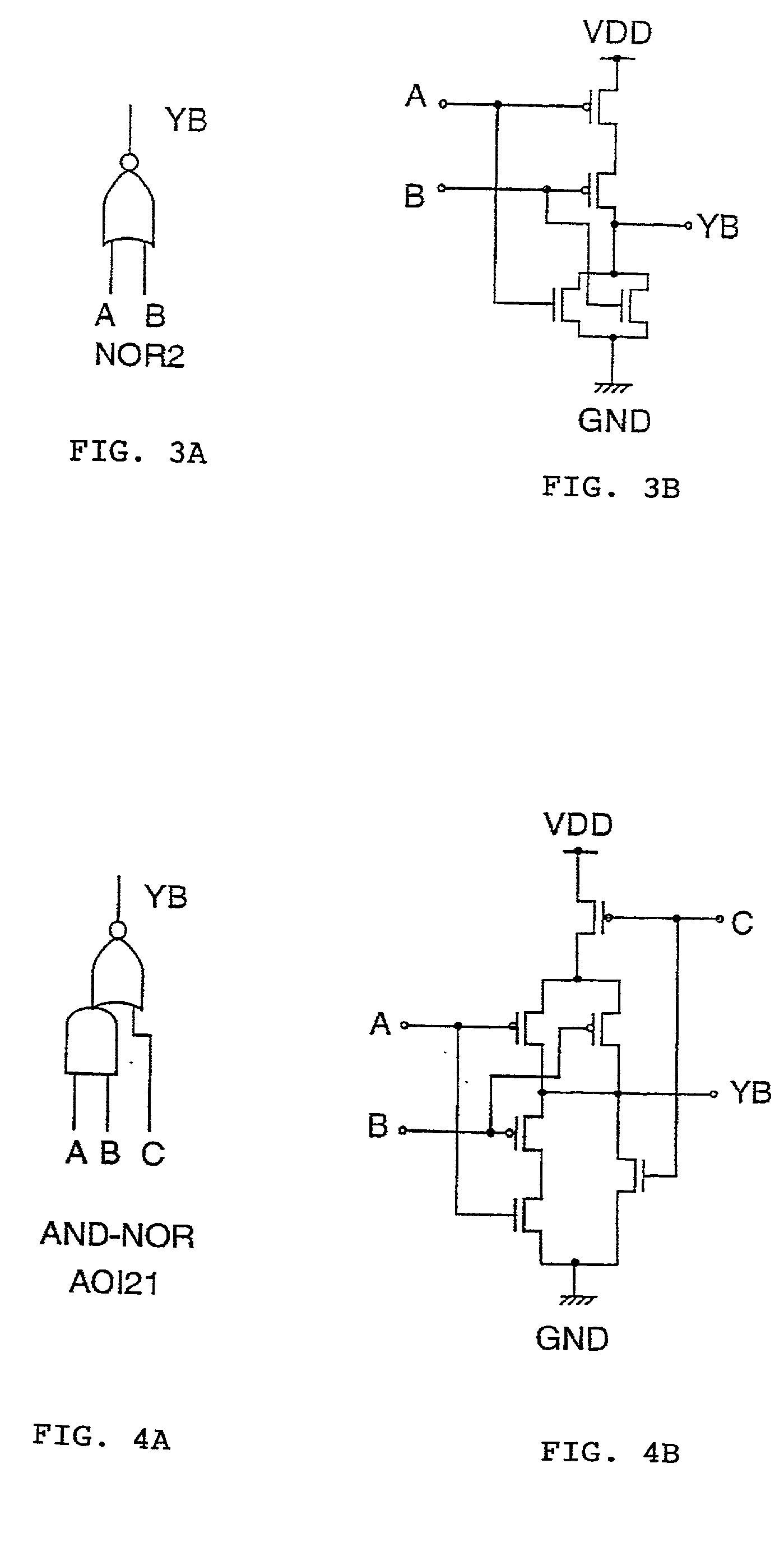

[0176] FIGS. 28A shows a layout of a two-input AND gate AND2, and its circuit is shown in FIG. 9. The layout in FIG. 28A is different from that in FIG. 14 in that the output portions of transistors 33 and 36 are not connected in parallel, and both layouts are identical in the remaining construction. FIG. 28B shows diffusion regions and gate polysilicon wirings extracted from the layout shown in FIG. 28A. FIG. 29A shows first metal layer wirings extracted from the layout in FIG. 28A, and FIG. 29B shows second metal layer wirings extracted from the layout in FIG. 28A. The same drawing method applies in the subsequent embodiments.

[0177] FIGS. 30A and 30B and FIGS. 31A and 31B show the layout of a two-input OR gate OR2. Referring to FIG. 32B, the gate OR2 is formed by connecting a gate NOR2 and a NOT gate. FIG. 33 is a circuit diagram of the gate OR2. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More