Configurable embedded processor

a technology of embedded processors and memory systems, applied in the direction of memory address formation, micro-instruction address formation, instruments, etc., can solve the problems of dual port memory operating frequency, dual port memory operation at lower frequencies, and additional complexity of dual port memory, so as to increase the utilization of cpu and dma controller

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

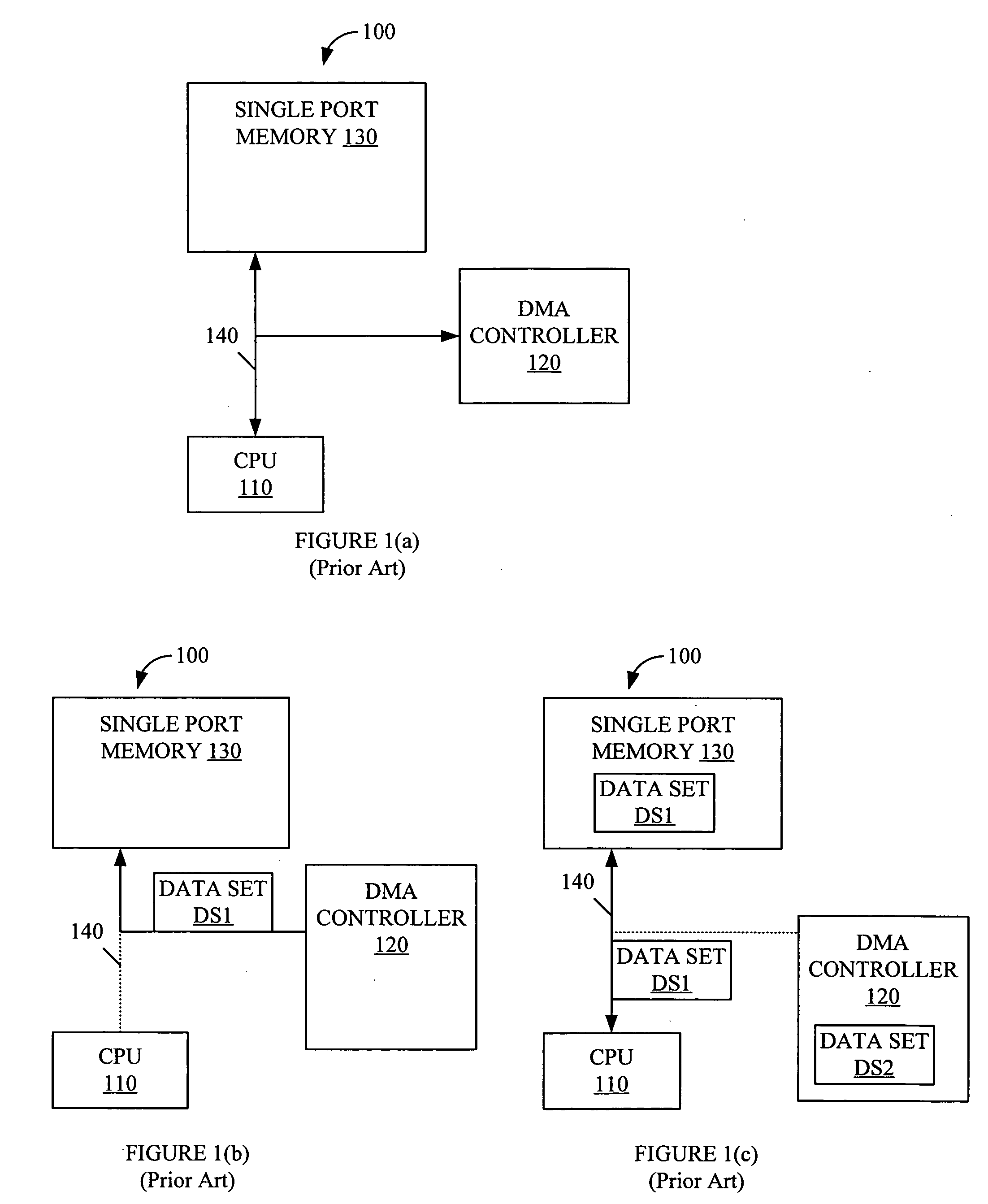

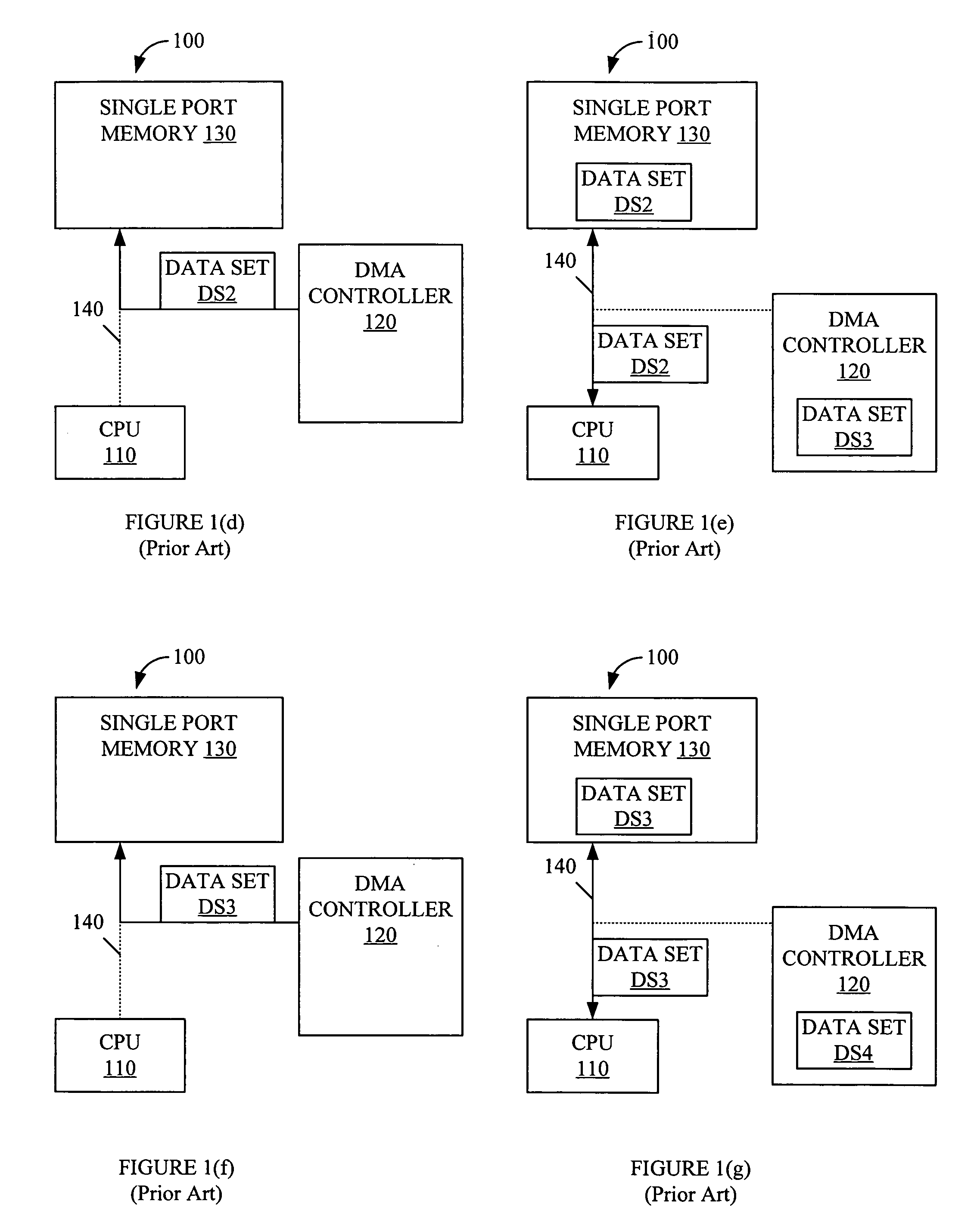

[0016] As explained above, conventional microprocessor systems have low utilization of the CPU due to memory bottlenecks caused by sharing a single port memory with a DMA controller. While using a dual port memory provides higher utilization, the cost in silicon area and power for the dual port memory prevents wide spread use of dual port memories. The present invention provides a novel microprocessor system that provides the benefits of a dual port memory system without the detriments.

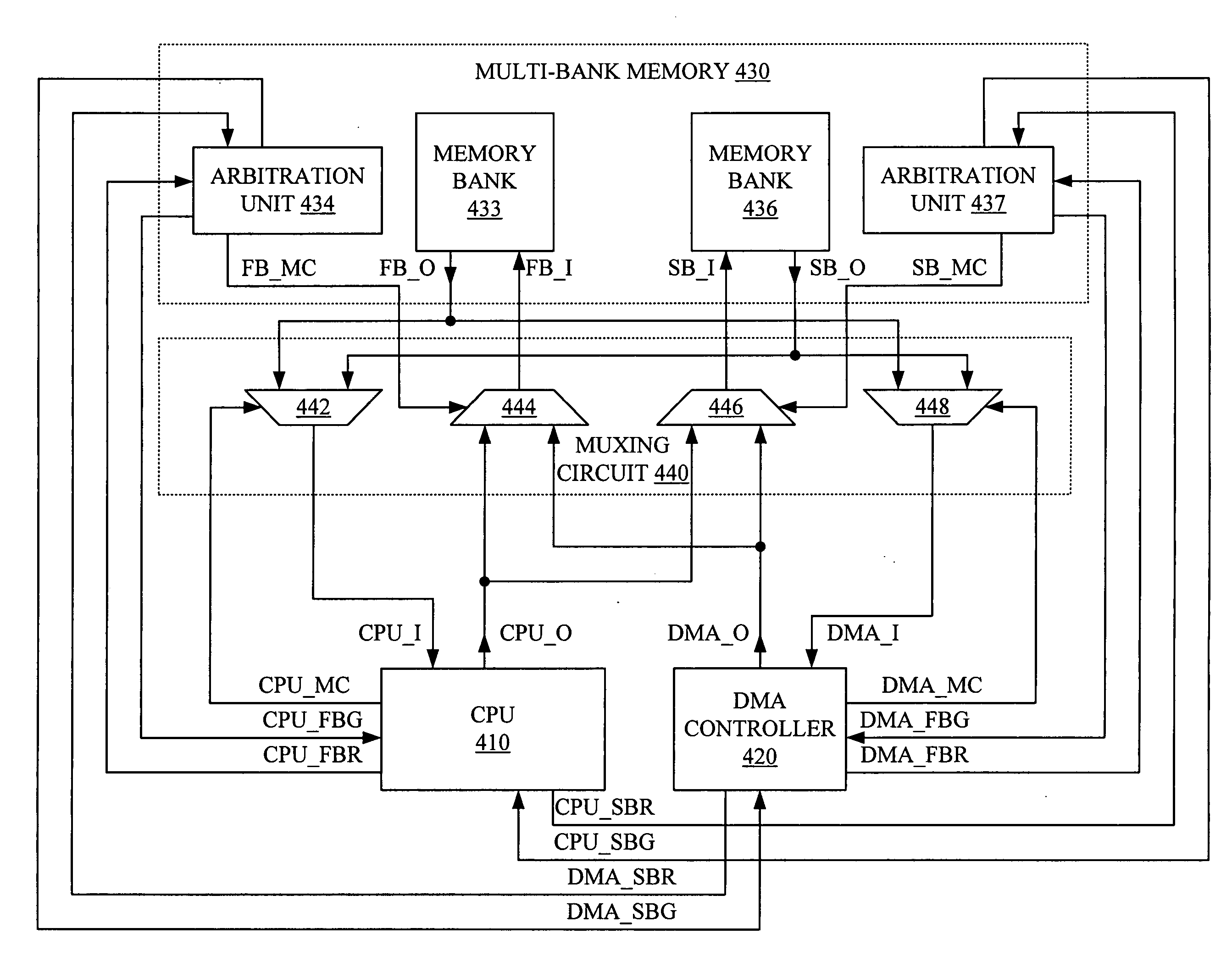

[0017]FIG. 3 is a simplified block diagram of a microprocessor system 300 in accordance with one embodiment of the present invention. Microprocessor system 300 includes a CPU 310, a DMA controller 320, a multi-bank memory 330 having a first memory bank 333 and a second memory bank 336, and a muxing circuit 340. Muxing circuit 340 couples CPU 310 and DMA controller 320 to memory banks 333 and 336. Muxing circuit 340 could be for example, a multiplexer or a crossbar switch. For clarity, the sample embo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More