High frequency differential power amplifier

a power amplifier and high frequency technology, applied in the field of high frequency communications, can solve the problems of excessive voltage drop, unsatisfactory output signal degradation, and increase the power consumption of differential amplifiers b>100, and achieve the effect of not consuming excessive power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

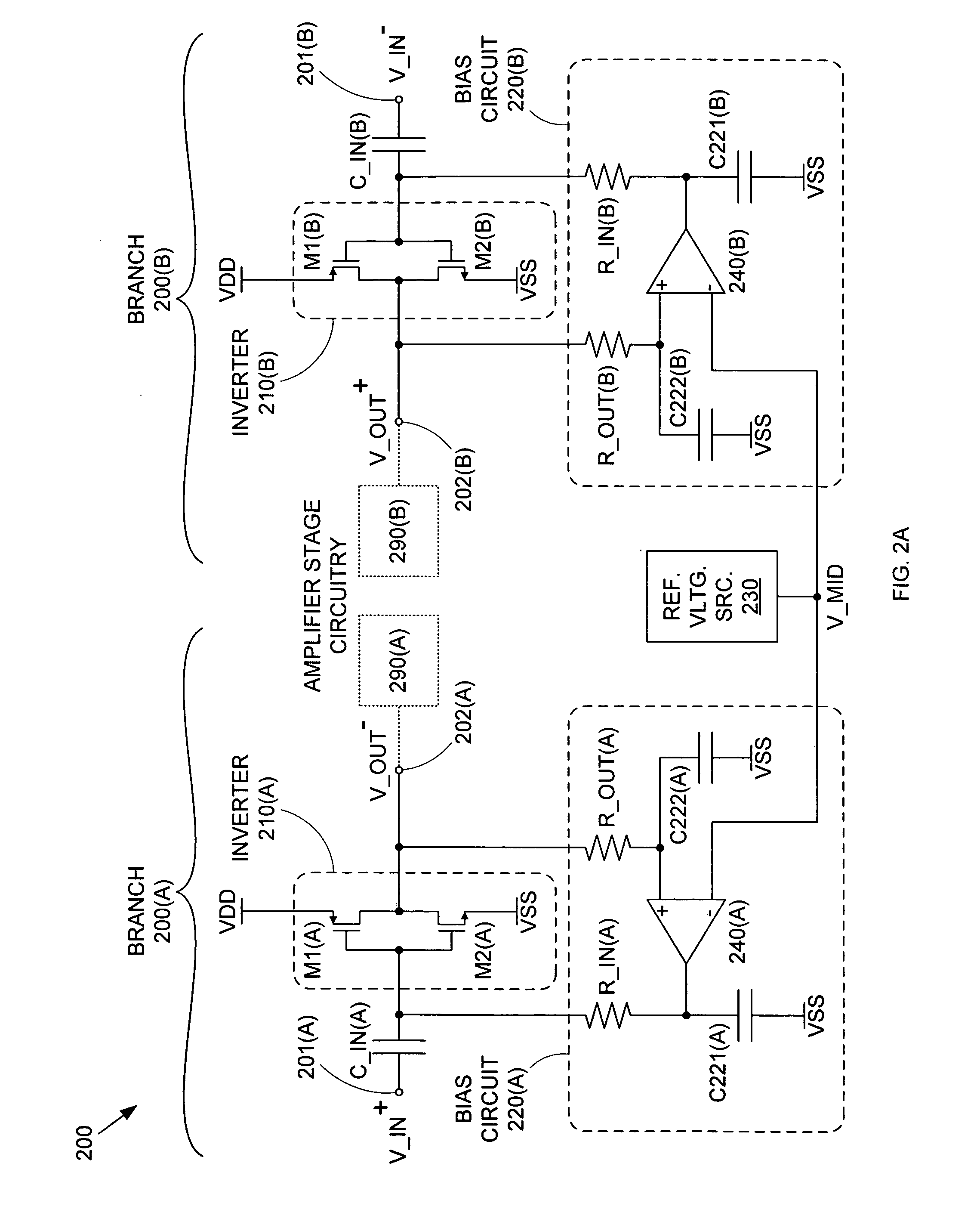

[0024]FIG. 2A shows a high-frequency amplifier circuit 200 in accordance with an embodiment of the invention. Amplifier circuit 200 is formed from two branches 200(A) and 200(B). Branch 200(A) includes an input terminal 201(A), an output terminal 202(A), a CMOS inverter 210(A), a capacitor C_IN(A), and a bias circuit 220(A). Capacitor C_IN(A) is coupled between input terminal 201(A) and the input of inverter 210(A) and provides DC filtering at the input of inverter 210(A). Bias circuit 220(A) is connected between the output and input of inverter 210(A).

[0025] Inverter 210(A) includes a PMOS transistor M1(A) and an NMOS transistor M2(A) that are serially coupled between an upper supply voltage VDD and a lower supply voltage (e.g., ground). The gate terminals of transistors M1(A) and M2(A) are connected to form the input of inverter 210(A), while the drain terminals of transistors M1(A) and M2(A) are connected to form the output of inverter 210(A).

[0026] Branch 200(B) is substantial...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More