Pipelined clock stretching circuitry and method for I2C logic system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

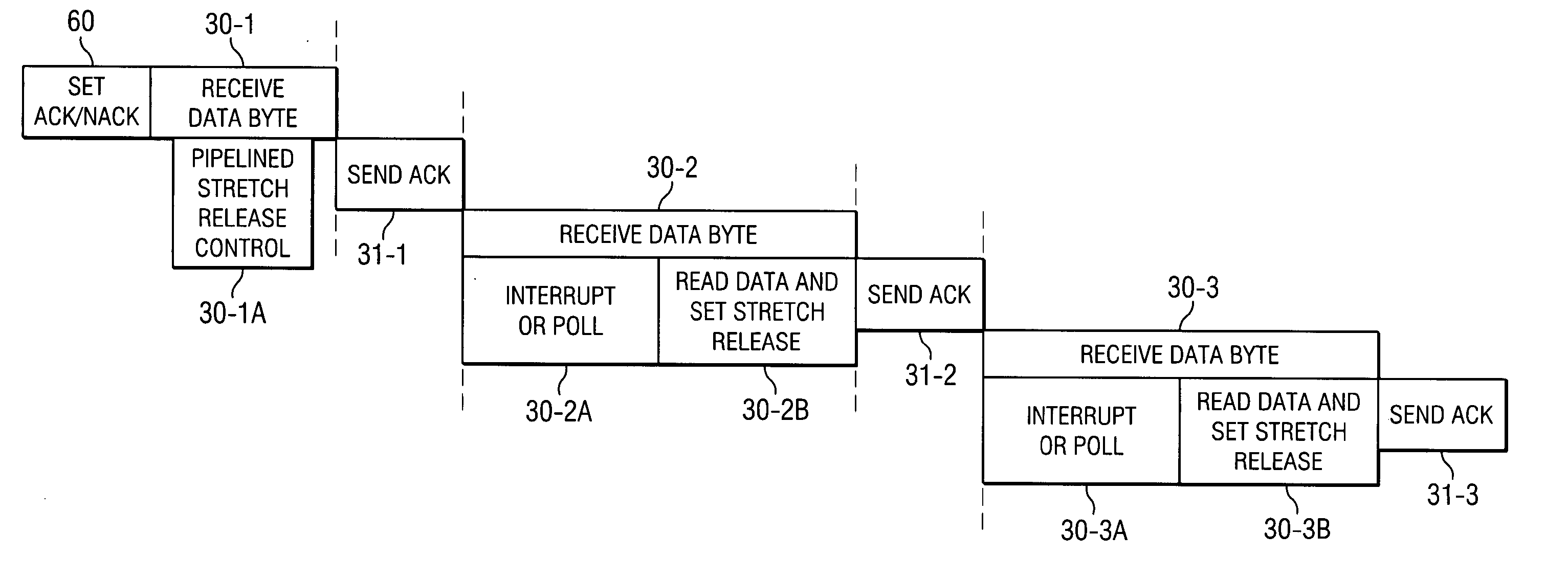

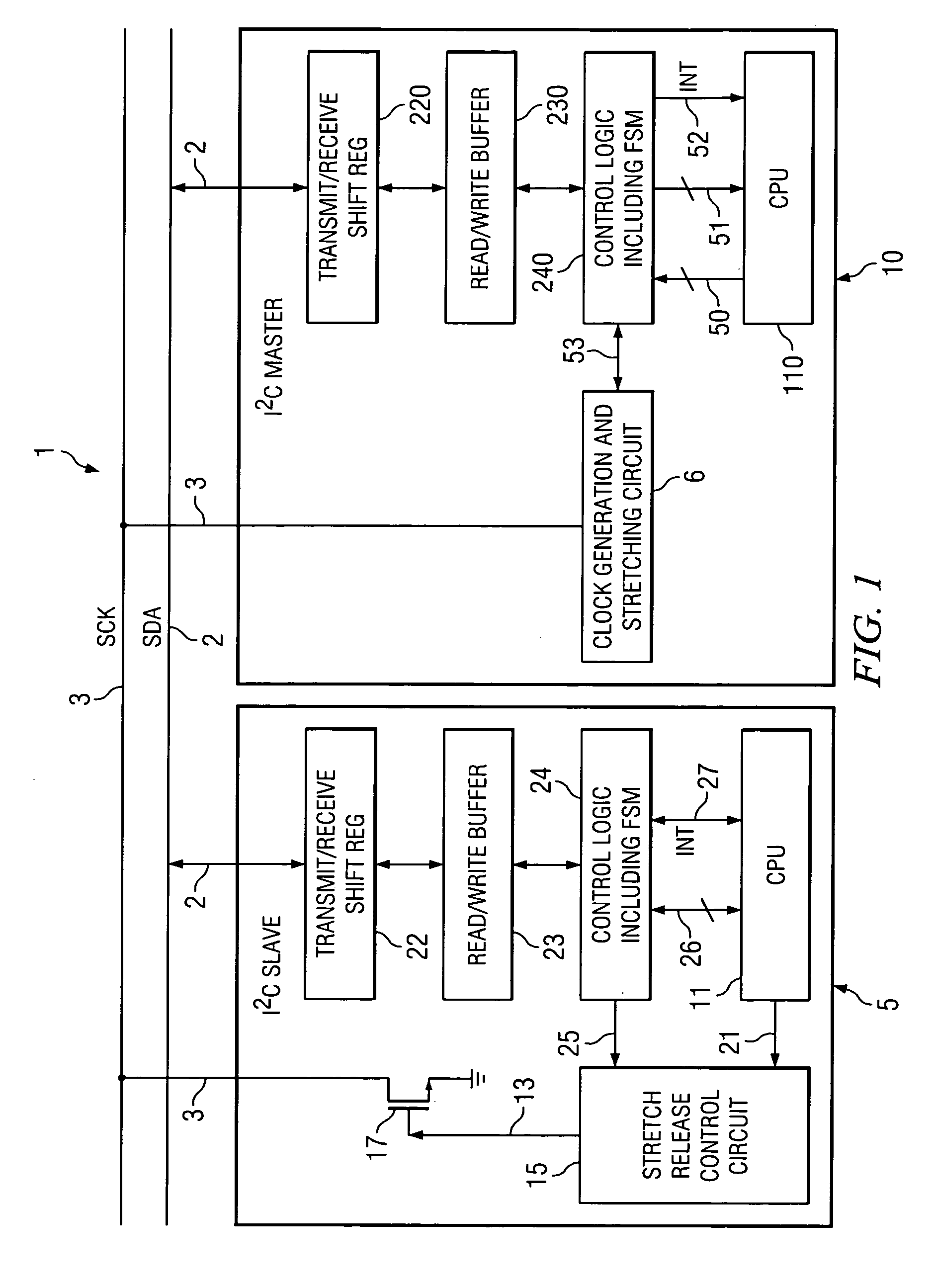

[0024] Referring to FIG. 1, I2C system 1 includes a serial data bus conductor 2 which conducts the serial clock data signal SDA and a serial clock conductor 3 that conducts the serial clock signal SCK. I2C system 1 includes an I2C slave device 5 and an I2C master device 10, both of which are connected to SCK conductor 3 and SDA conductor 2.

[0025] Slave device 5 includes an N-channel transistor 17 having its drain connected to SCK conductor 3 and its source connected to a ground conductor. The gate of transistor 17 is connected to a stretch release control circuit 15 (shown in detail in FIG. 5), which operates to “stretch” SCK by temporarily pulling SCK conductor 3 to ground, in response to control signals received on conductor 25 from control logic circuit 24 and on conductor 21 from a CPU (central processing unit) 11. Slave device 5 also includes a transmit / receive shift register 22 connected to SDA conductor 2. Transmit / receive shift register 22 is bidirectionally coupled by mult...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com