Solid state image pickup device and its manufacture method

a solid-state image and pickup device technology, applied in the direction of semiconductor devices, basic electric elements, electrical appliances, etc., can solve the problems of likely blooming between pixels, suppress blooming between pixels, and suppress the effect of lowering the long wavelength sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0046]FIG. 2 is a schematic cross sectional view of a pixel area of a solid state image pickup device according to the

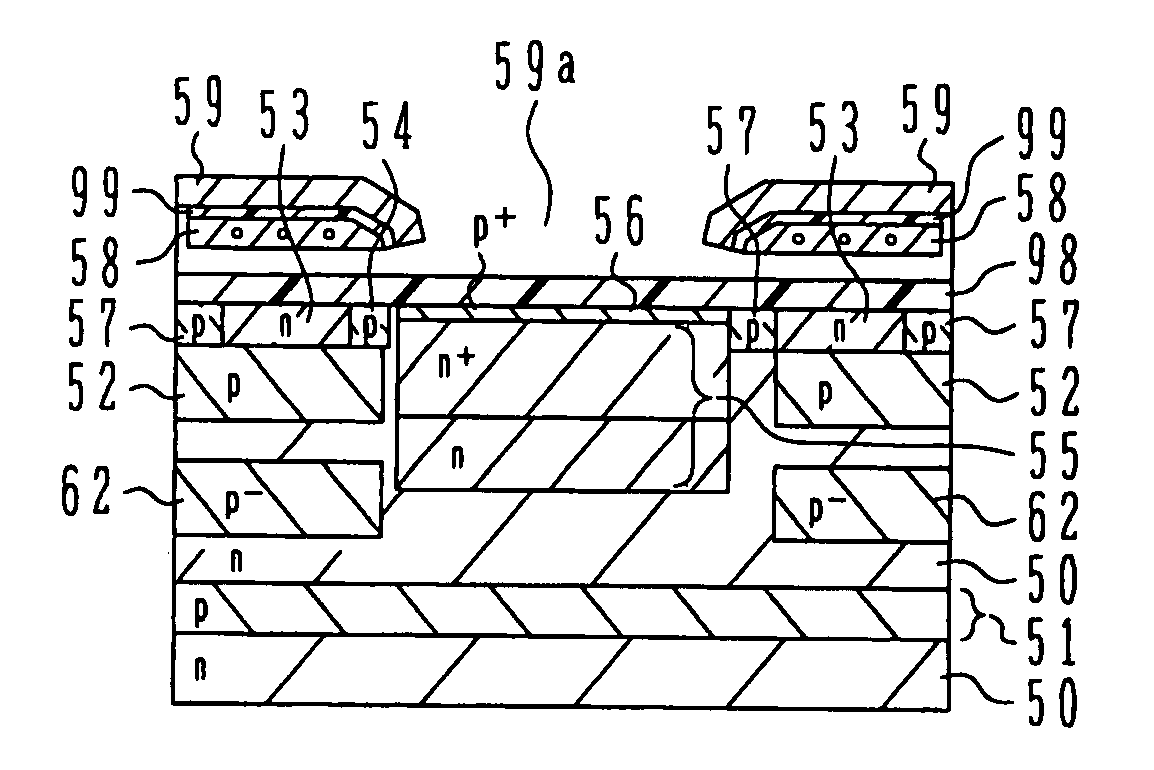

[0047] Although the structure of the solid state image pickup device is similar to that shown in FIG. 9B, it is different in that an overflow barrier region 51 is formed deeper in an n-type semiconductor substrate 50 and that a low concentration p-type (p−-type) impurity layer (pixel separation impurity layer) 62 is formed between a p-type impurity layer (channel protection impurity layer) 52 under the vertical transfer channel 53 and the overflow barrier region 51, e.g., at a middle depth between the layer 52 and region 51. The low concentration p-type (p−-type) impurity layer 62 is formed under the p-type impurity layer 52 and faces the p-type impurity layer 52.

[0048] The peak position of the p-type impurity concentration of the overflow barrier region 51 is at a depth of 3.5 μm from the substrate surface. The overflow barrier region 51 can be formed at this depth...

second embodiment

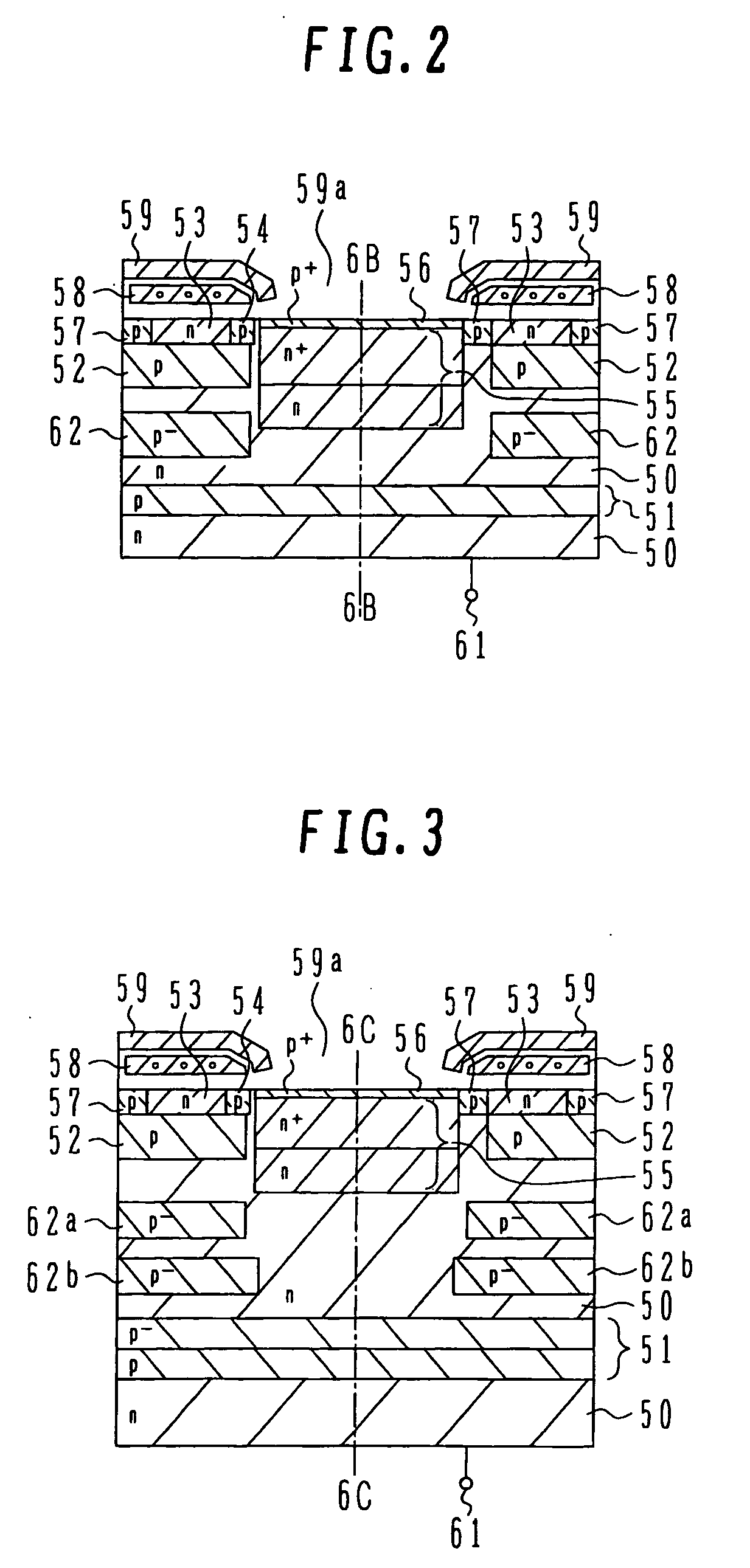

[0063]FIG. 3 is a schematic cross sectional view of a solid state image pickup device according to the

[0064] A first different point from the first embodiment shown in FIG. 2 is that an overflow barrier region has a multi-layer structure (in this example, two layers) along a substrate depth direction. In the first embodiment, the overflow barrier area 51 is made of only a single p-type impurity layer, whereas in the second embodiment, the overflow barrier region 51 is made of a p-type impurity layer and an upper p−-type impurity layer. A peak position of the p-type impurity concentration of the overflow barrier region 51 is at a depth of, e.g., 4.4 μm from the semiconductor substrate surface.

[0065] A preferable depth and effects of the peak position of the p-type impurity concentration of the overflow barrier region 51 are similar to the first embodiment. By making the overflow barrier region 51 have a multi-layer structure, an impurity concentration of the p-side region of a pn ju...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More