Digital Loop Filter for All-Digital Phase-Locked Loop Design

a phase-locked loop and filter technology, applied in the field can solve the problems of the design of digital loop filters, the inability to reduce the jitter effect of output signals, and so as to reduce the period jitter of output signals of pll, reduce the output jitter of all-digital pll designs, and reduce the jitter effect of input signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

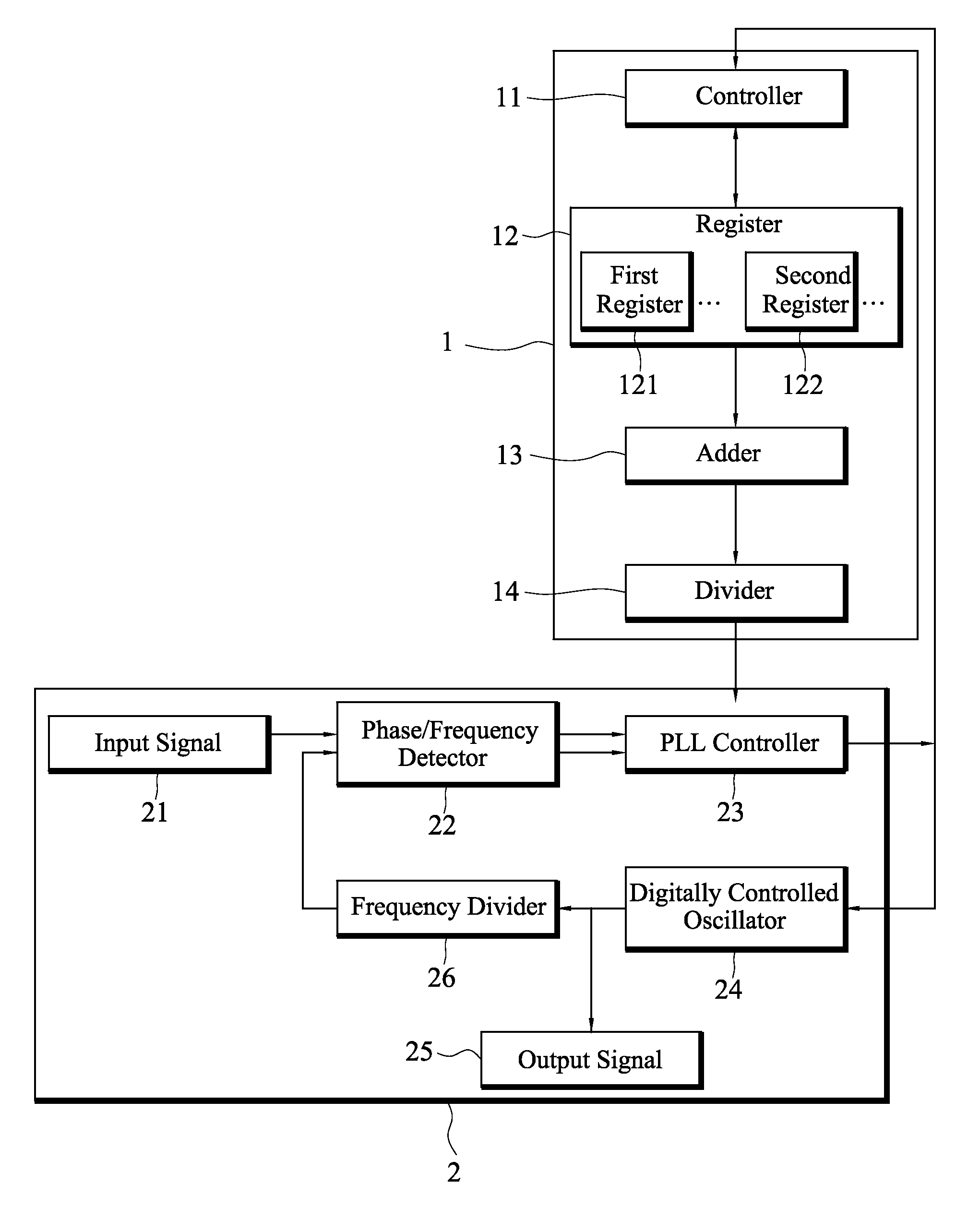

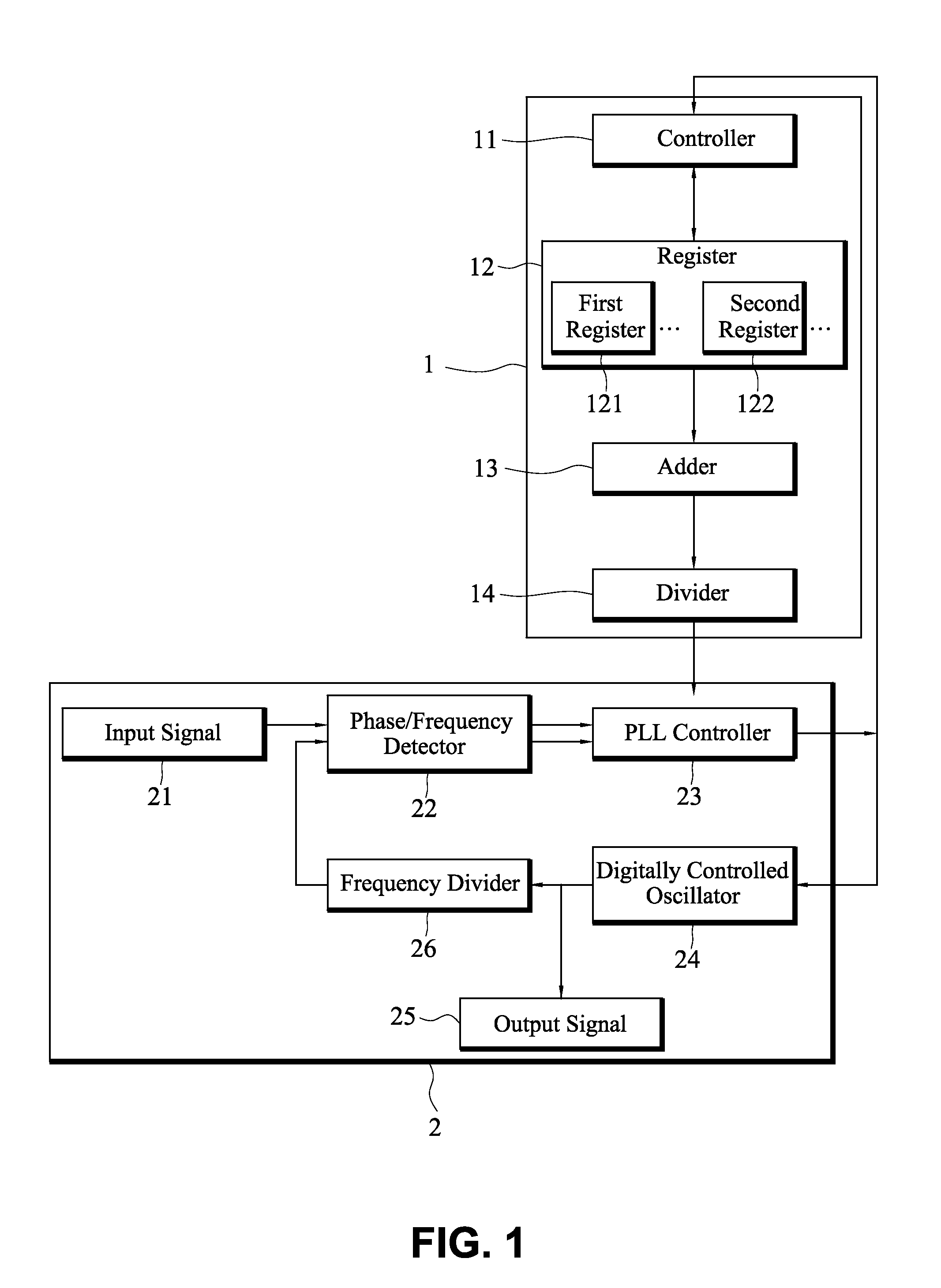

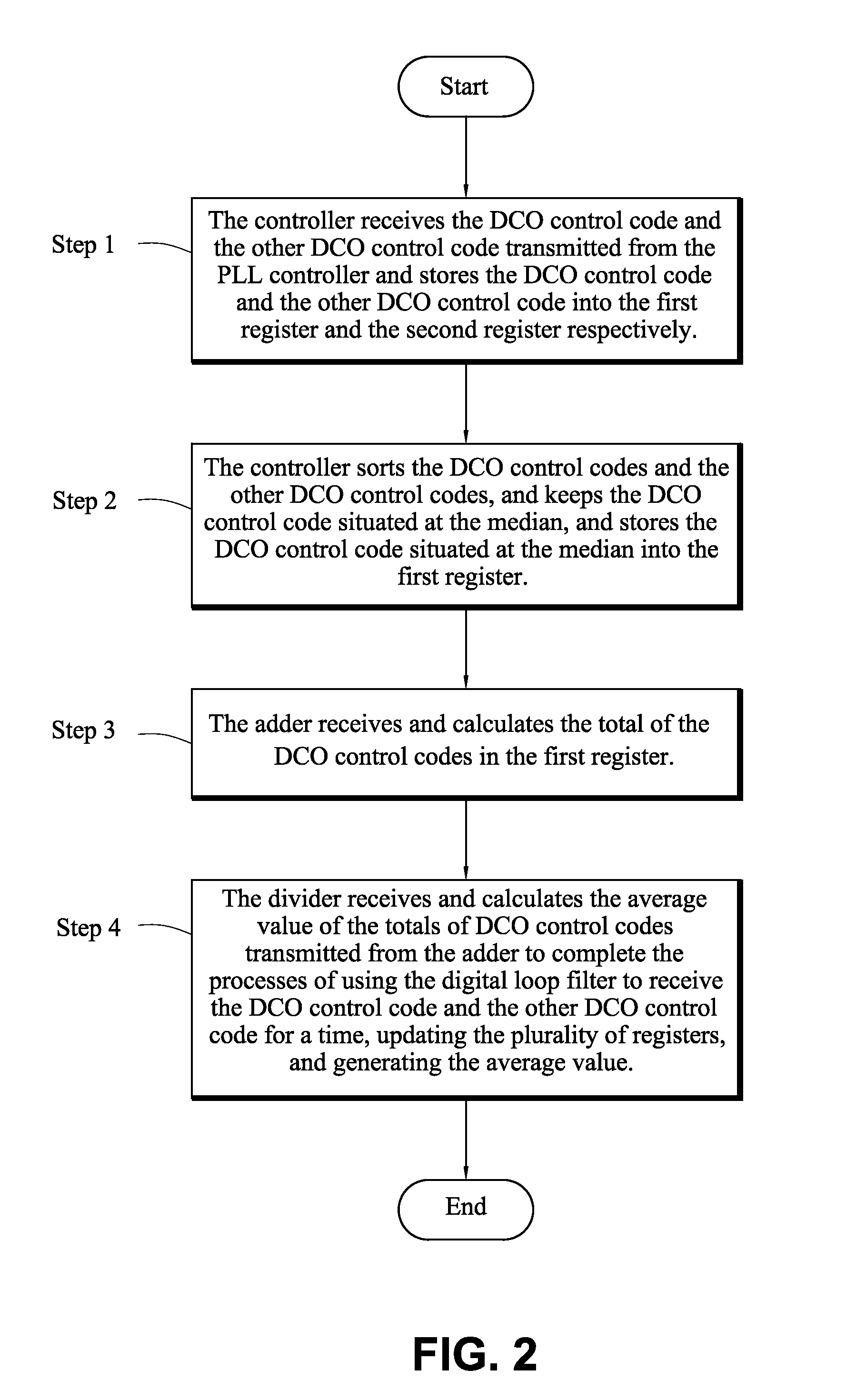

[0015]The present invention relates to a digital loop filter for an all-digital PLL design. With reference to FIG. 1 for a schematic view of a structure of a digital loop filter 1 installed in an all-digital PLL 2, the digital loop filter 1 includes a controller 11 for receiving a DCO control code and another DCO control code transmitted from a phase-locked loop (PLL) controller in the all-digital PLL 2, and updating the DCO control code and the other DCO control code into a plurality of registers 12.

[0016]The plurality of registers 12 are provided for storing the DCO control code and the other DCO control code updated and transmitted by the controller 11, wherein the plurality of registers 12 include a plurality of first registers 121 (such as M=T0˜T(M−1)) and a plurality of second registers 122 (such as K=TM˜T(M+K−1)), and the plurality of first registers 121 are provided for storing the DCO control code transmitted from the controller 11, and the plurality of second registers 122...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More