Phase lock loop

A phase-locked loop and circuit technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems affecting the performance of traditional phase-locked loop 1, output jitter, etc., to achieve the effect of reducing output jitter and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

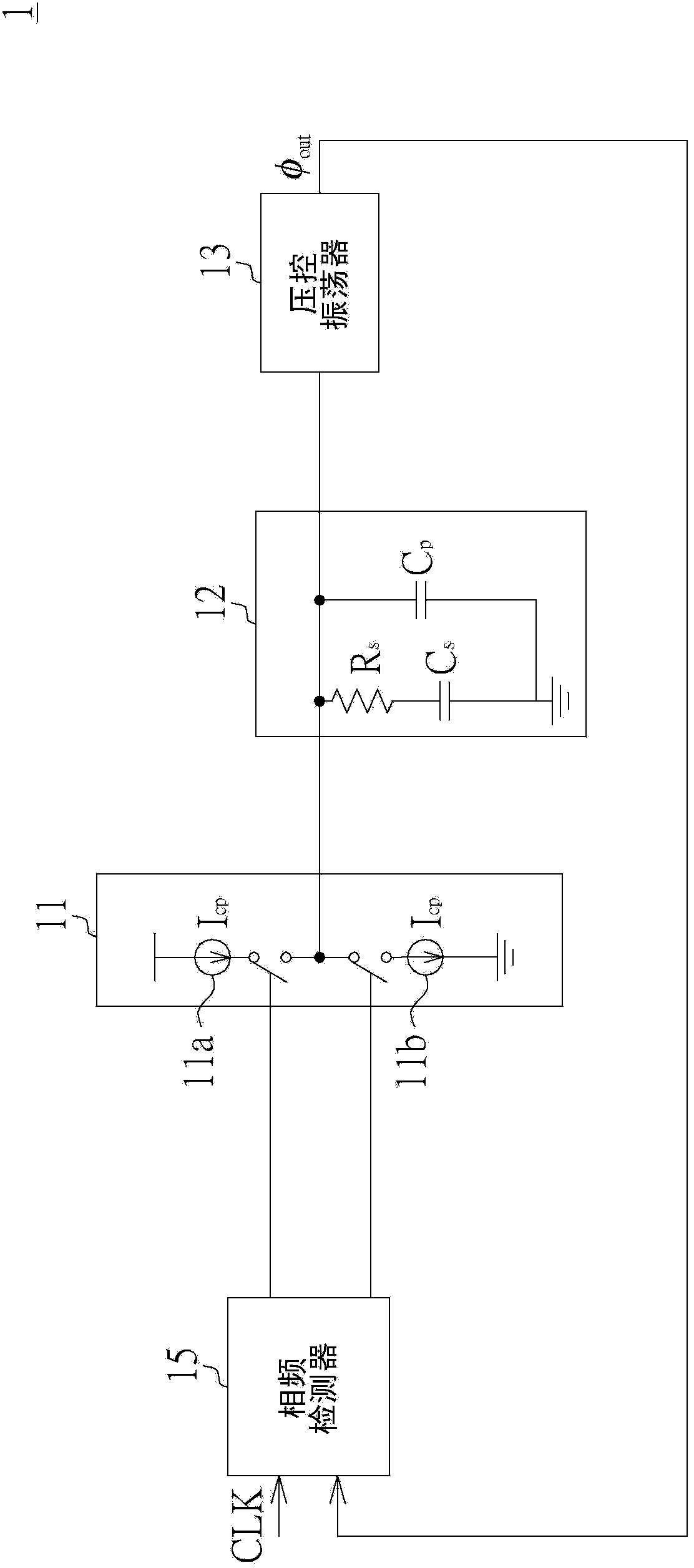

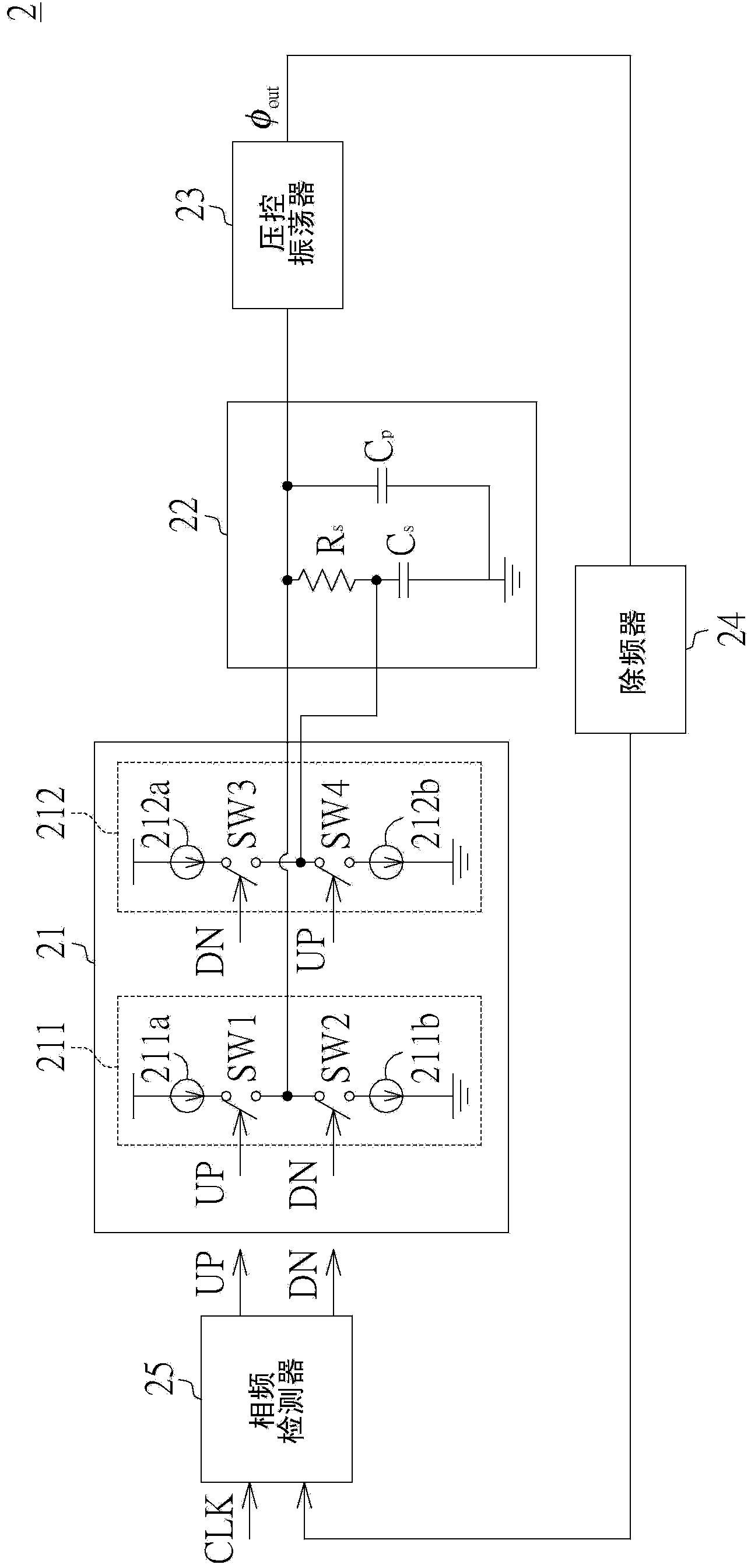

[0036] Please also refer to figure 1 and figure 2 , figure 2 is a schematic diagram of a phase lock loop (PLL) according to the first embodiment. The phase locked loop 2 includes a charge pump circuit 21 , a loop filter 22 , a voltage controlled oscillator 23 , a frequency divider 24 and a phase frequency detector (Phase Frequency Detector) 25 . The voltage controlled oscillator 23 generates an oscillation signal Φ according to the output of the loop filter 22 out ’, the phase frequency detector 25 according to the oscillation signal Φ out ’ and the clock signal CLK provide the switch signal UP and the switch signal DN.

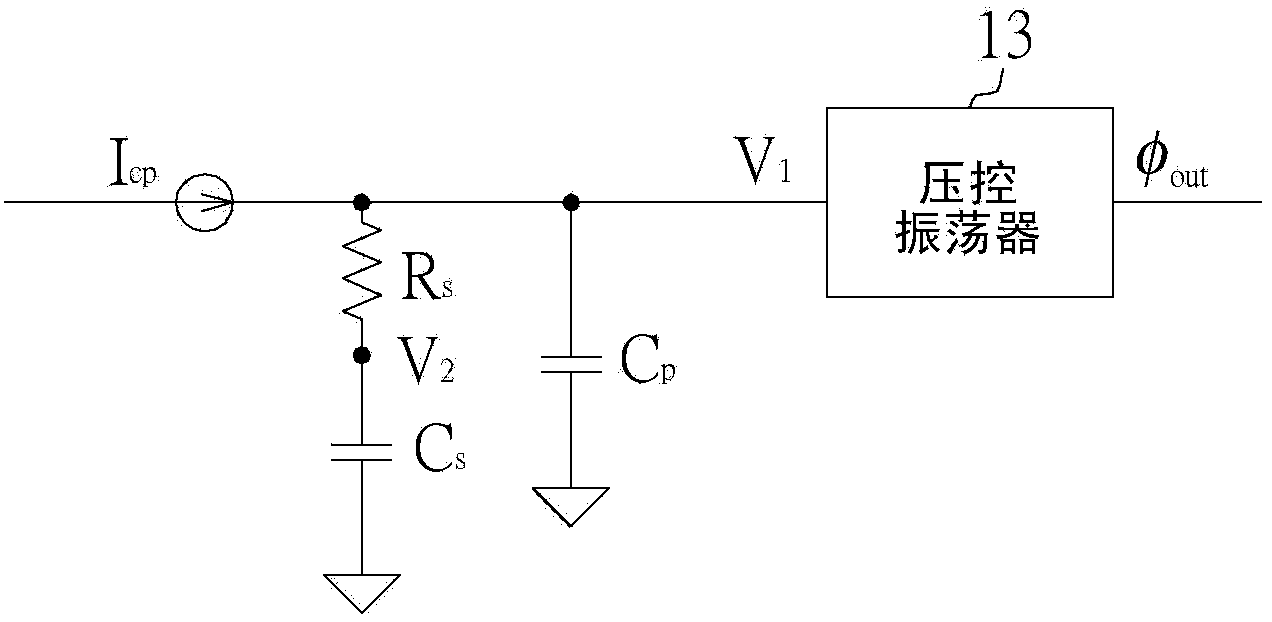

[0037] The loop filter 22 includes a shunt capacitor C p ’, series resistance R s ’ and the series capacitor C s '. Series resistance R s ’ is electrically connected to the parallel capacitor C p ’ at one end. Series capacitance C s ’ is electrically connected to the series resistor R s ’, while the series capacitor C s ’ The other end is elec...

no. 2 example

[0058] Please refer to Figure 5 , Figure 5 is a schematic diagram of a phase-locked loop according to the second embodiment. The second embodiment differs from the first embodiment in that the PLL 3 uses a third-order loop filter 32 . The loop filter 32 divides the shunt capacitor C p ’, series resistance R s ’ and the series capacitor C s ’, also includes the resistor R 1 and capacitance C 1 . Resistance R 1 One end is coupled to the series resistor R s ’ at one end. Capacitance C 1 One end of the resistor R1 is coupled to the other end, and the other end of the capacitor C1 is coupled to the series capacitor C s ’ the other end. In addition, in other embodiments, the phase-locked loop may also use loop filters of other orders.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More