Output buffer

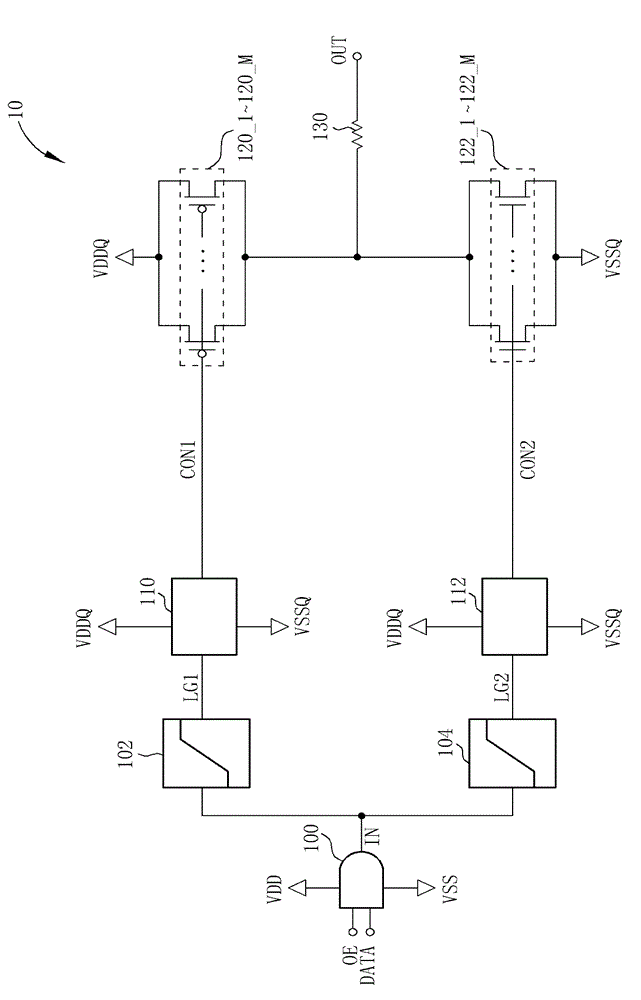

A technology of output buffer and output terminal, applied in the direction of logic circuit connection/interface layout, etc., can solve the problems of large output jitter of output signal OUT, unfavorable noise, large signal delay time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

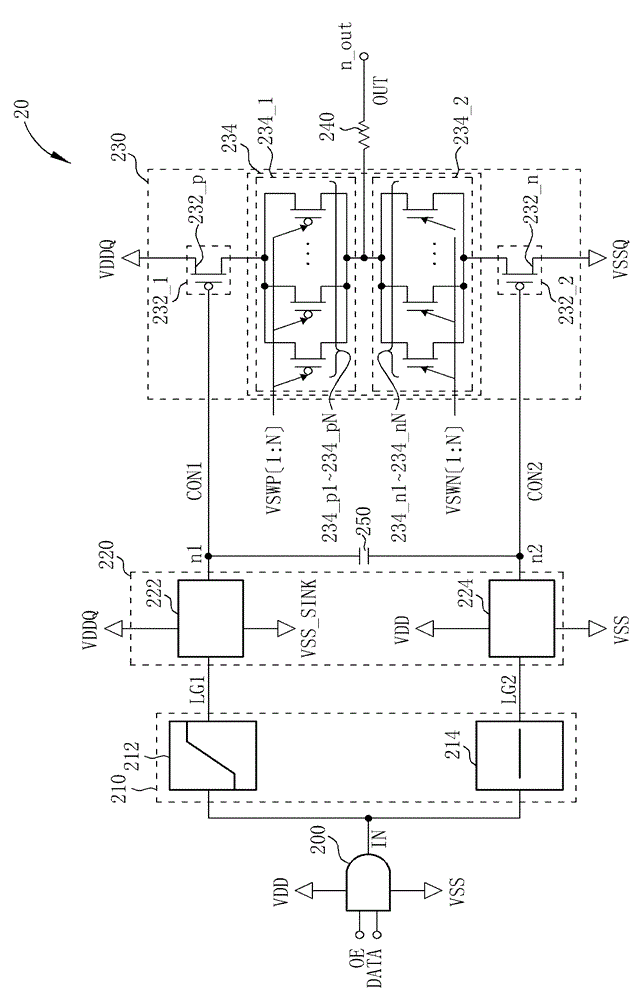

[0052]The output buffer provided in the following embodiments can maintain the stability of the output signal when the operating voltage keeps dropping. The following embodiments consider that in the Complementary Metal-Oxide-Semiconductor (CMOS) process, the driving current of the low-voltage transistor is weakened by the reduction of the supply voltage level is less obvious, so the output buffer Some components in the converter that are not directly facing the load are implemented with low-voltage components. As a result, the output buffer has better resistance to power supply noise, and can achieve a smaller delay time of the output signal, thereby making it easier to achieve a low-jitter output signal.

[0053] Please refer to figure 2 , figure 2 It is a schematic structural diagram of an output buffer 20 according to an embodiment. The output buffer 20 includes a logic unit 200 , a level conversion module 210 , a pre-driver module 220 , an output module 230 and a res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More