Method of fabricating solar cell chips

a technology of solar cells and solar energy, applied in the field of solar cells, can solve the problems of limiting the widespread use of solar cells, the relative high cost of fabricating solar cells,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

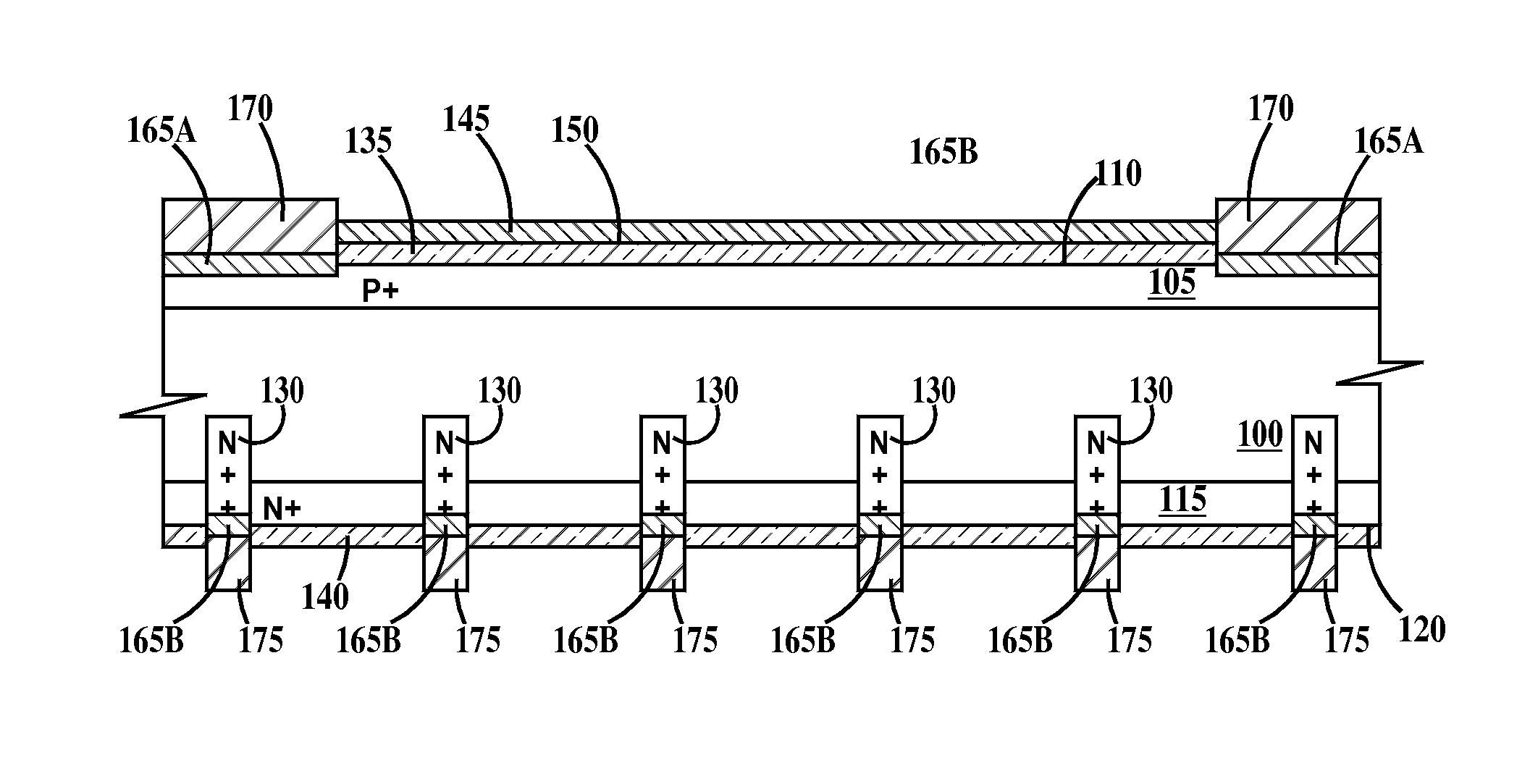

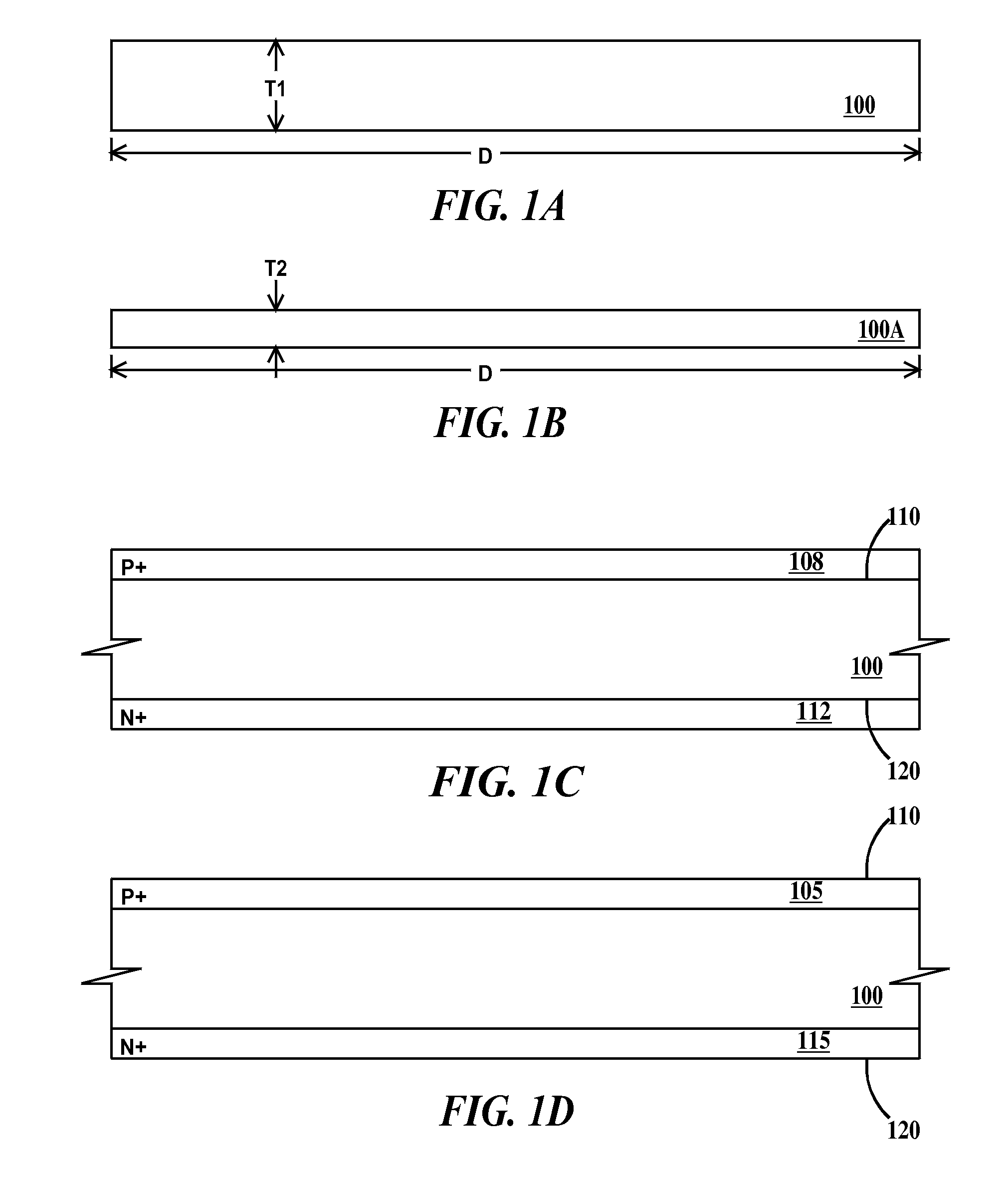

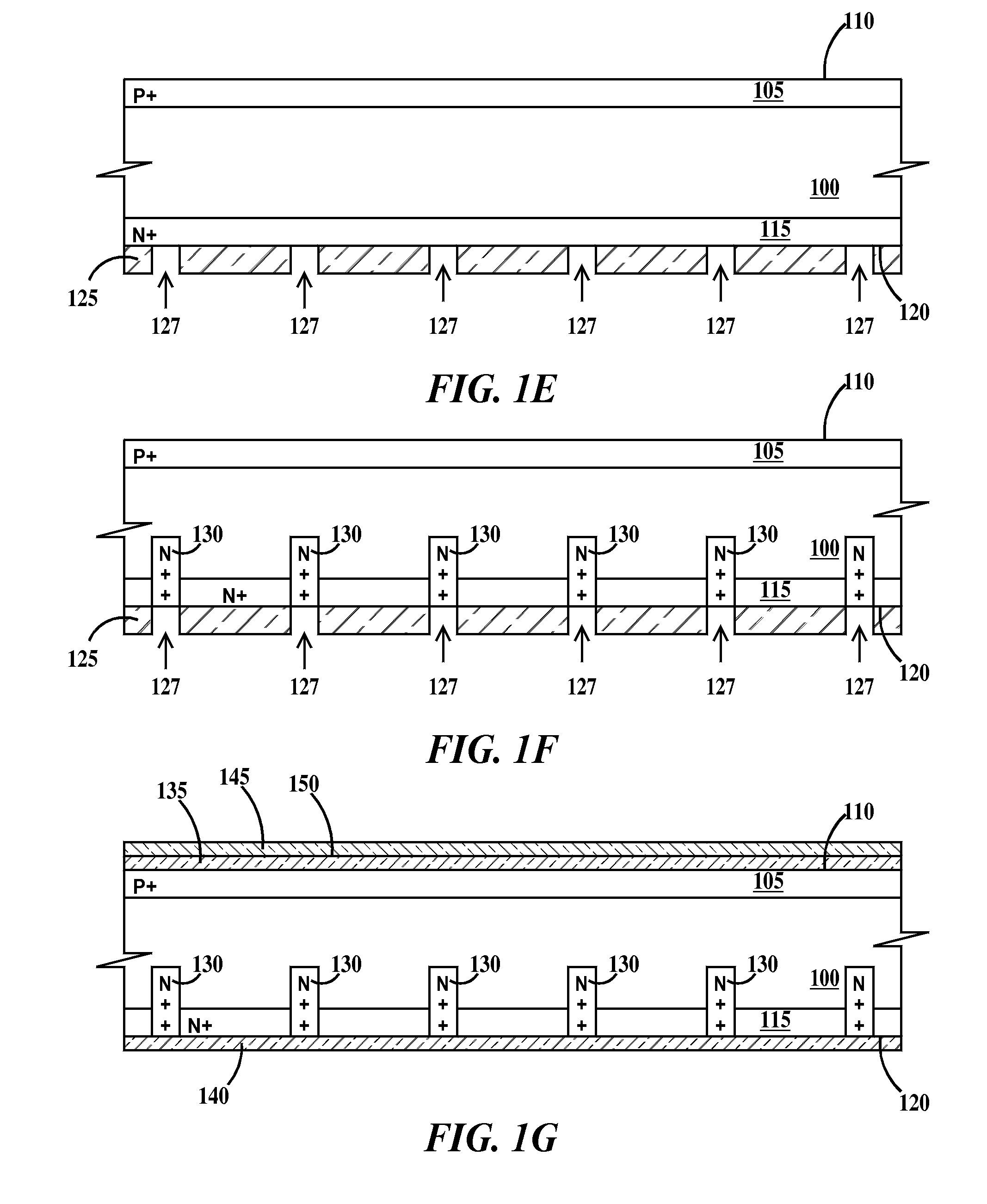

[0011]FIGS. 1A through 1J are cross-sectional drawings illustrating fabrication of a solar cell according to embodiments of the present invention. Generally, integrated circuit chips are fabricated using semiconductor substrates that are thin disc shaped substrates called wafers. The terms substrate and wafer may be used interchangeably herein. An integrated circuit chip is defined as a solid-state device including transistors (e.g., field effect and / or bipolar transistors) forming logic and / or memory circuits. The logic and / or memory circuits may be analog or digital.

[0012]In FIG. 1A, a bulk single-crystal silicon substrate 100 has a thickness T1 and a diameter D. In one example, D is about 300 mm and T1 is about 700 microns. In FIG. 1B, substrate 100 of FIG. 1A has optionally been thinned to a thickness T2. In one example T2 is about 300 microns. In one example T2 is less than 700 microns. In one example, T2 is less than about 700 microns and not less than about 300 microns. In on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More