Chip packaging method and structure thereof

a technology of chip packaging and golden wires, applied in the direction of electrical apparatus, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of wasting golden wires and too long length of connecting golden wires, and achieve the effects of saving metal wire cost, shortening the length of metal wires, and raising the transmission speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

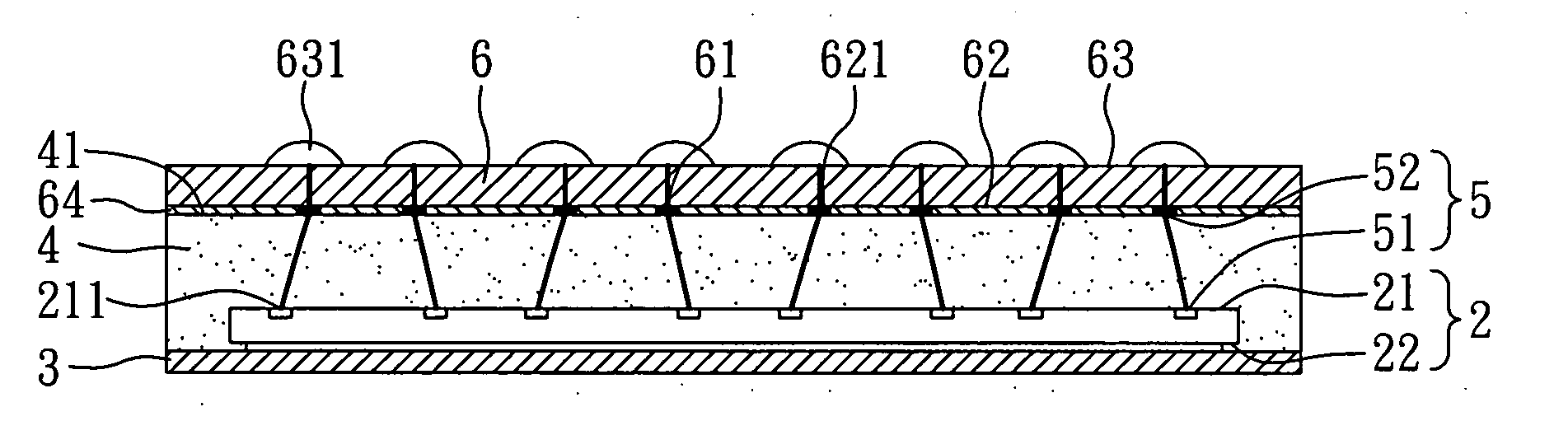

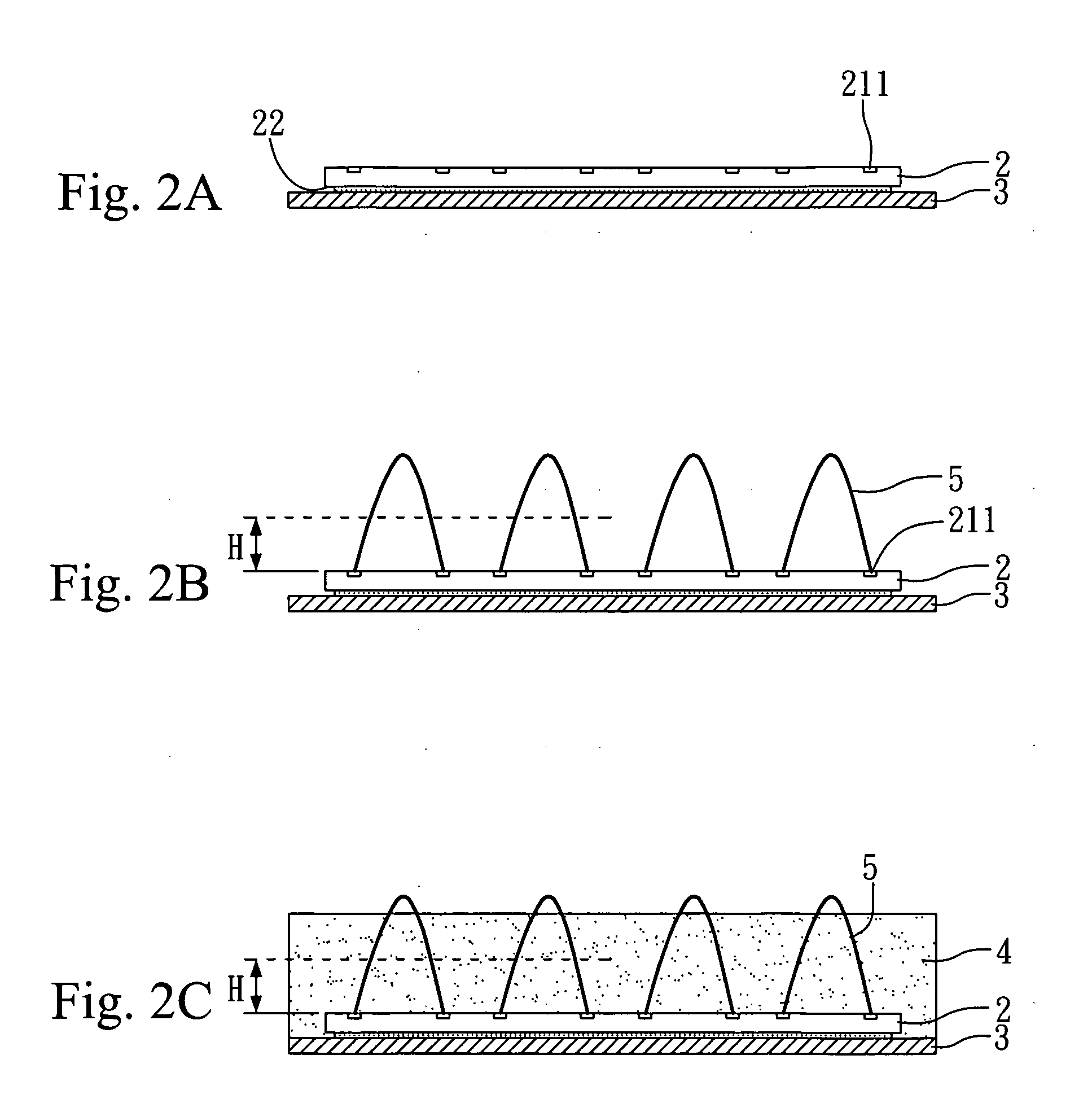

[0020]Please refer to FIGS. 2A to 2F together with FIG. 3. FIGS. 2A-2F are cross-sectional diagrams of each step for a chip packaging method of a preferred embodiment of the invention, and FIG. 3 is a flow chart of a preferred embodiment of the invention. Firstly, as shown in FIG. 2A, a chip 2 is provided, a plurality of bonding pads 211 are provided on an upper surface 21 thereof and a lower surface 22 of the chip 2 is mounted on a carrier board 3 (step A in FIG. 3). However, the carrier board 3 may be added in dependence of the condition or need and is mainly used for protecting the chip 2, while facilitating the proceeding of the packaging process.

[0021]Next, as shown in FIG. 2B, a plurality of metal wires 5 are connected out via bonding (step B in FIG. 3), and a middle part of each of the plurality of metal wires 5 is bent to be higher than a predetermined height H, in which two ends of each of the plurality of metal wires 5 are respectively electrically connected to two of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More