System and method for hierarchical power verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

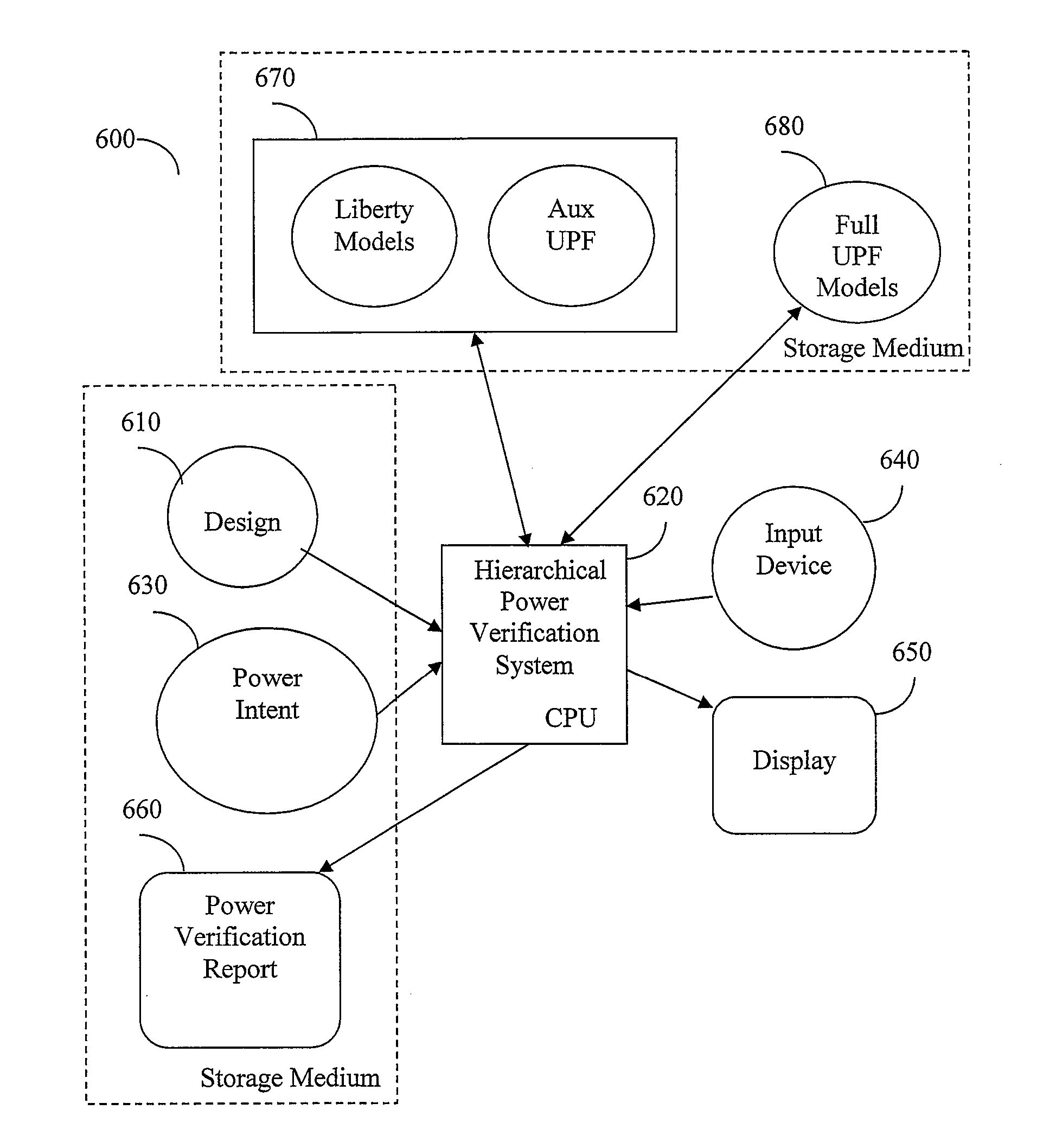

[0022]The hierarchical power verification system (HPVS) uses abstract models to significantly reduce power verification time. The HPVS creates abstract models of modules that it successfully verifies. The abstract models simplify the module definition by omitting internal module details but provide sufficient information for power verification of higher level modules that incorporate this abstracted module. After replacing modules with abstracted models the HPVS can quickly verify an entire SoC with a small memory footprint. When a user modifies a module, the HPVS need only verify the changed module and related modules at higher levels of module hierarchy. In contrast, existing power verification systems have to verify the entire design after a change.

[0023]FIG. 1 is an exemplary and non-limiting flowchart 100 showing how the hierarchical power verification system (HPVS) uses abstract models to significantly reduce power verification time. In S110 the HPVS reads the design, the powe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More