Wire bonding apparatus and manufacturing method for semiconductor apparatus

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

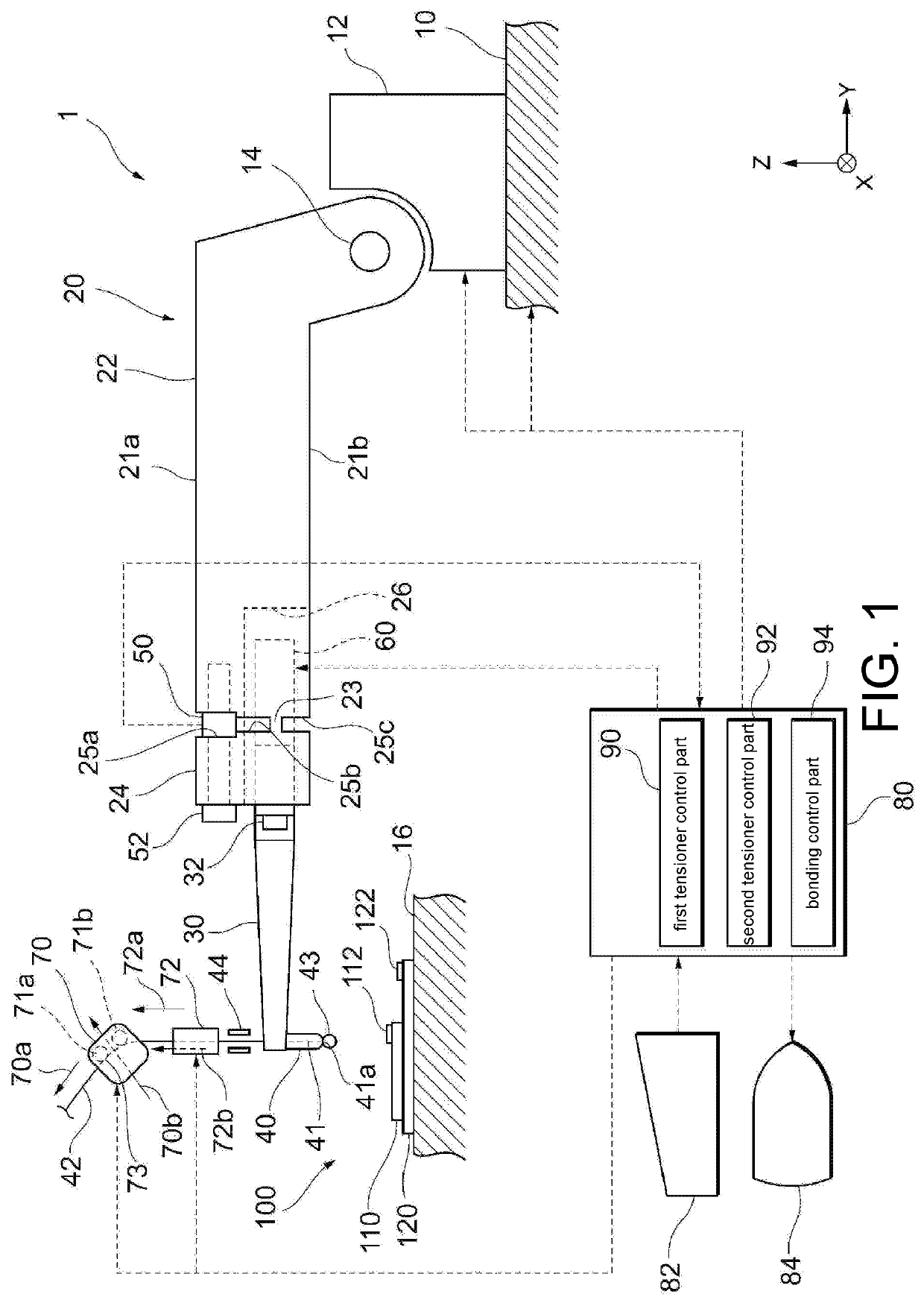

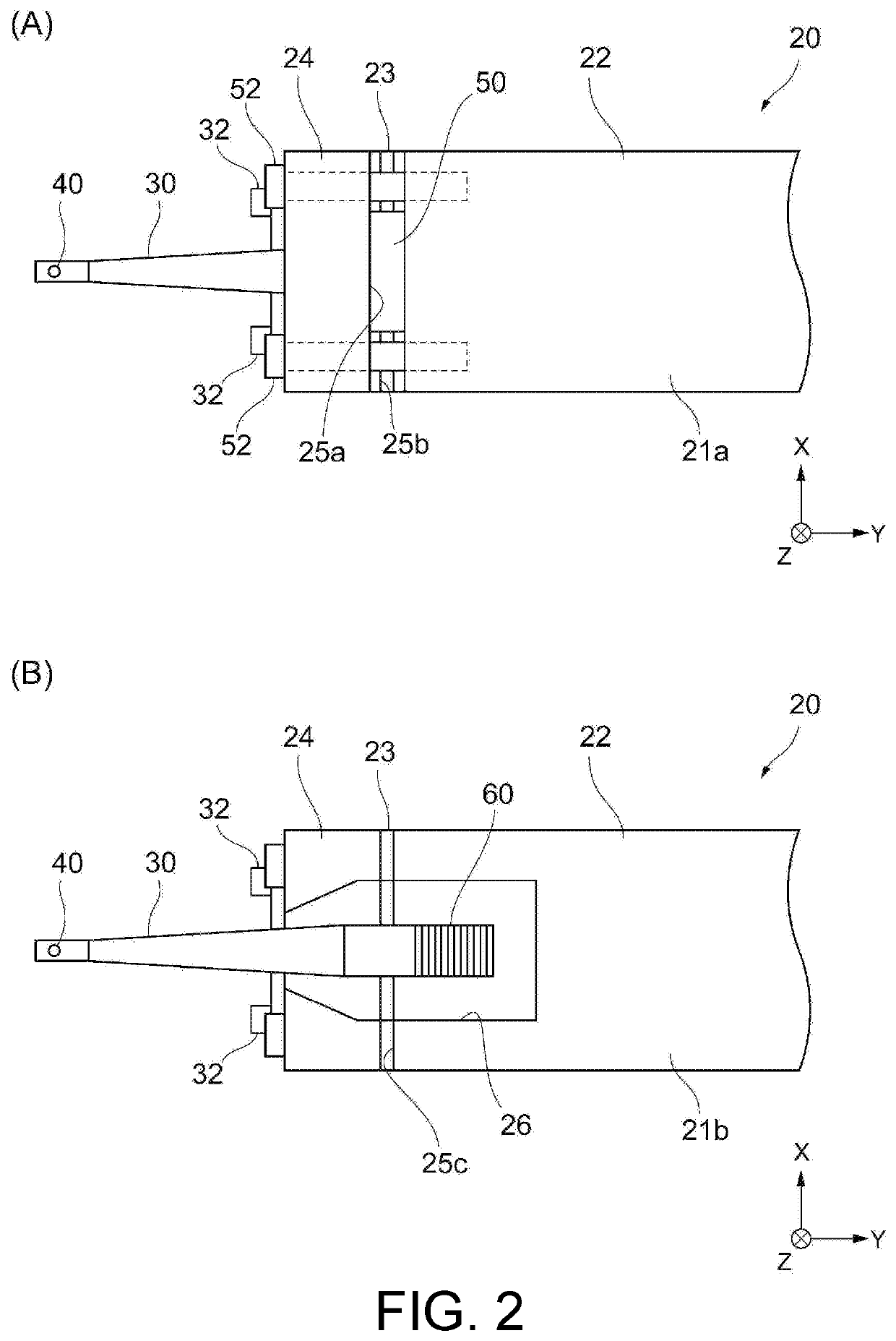

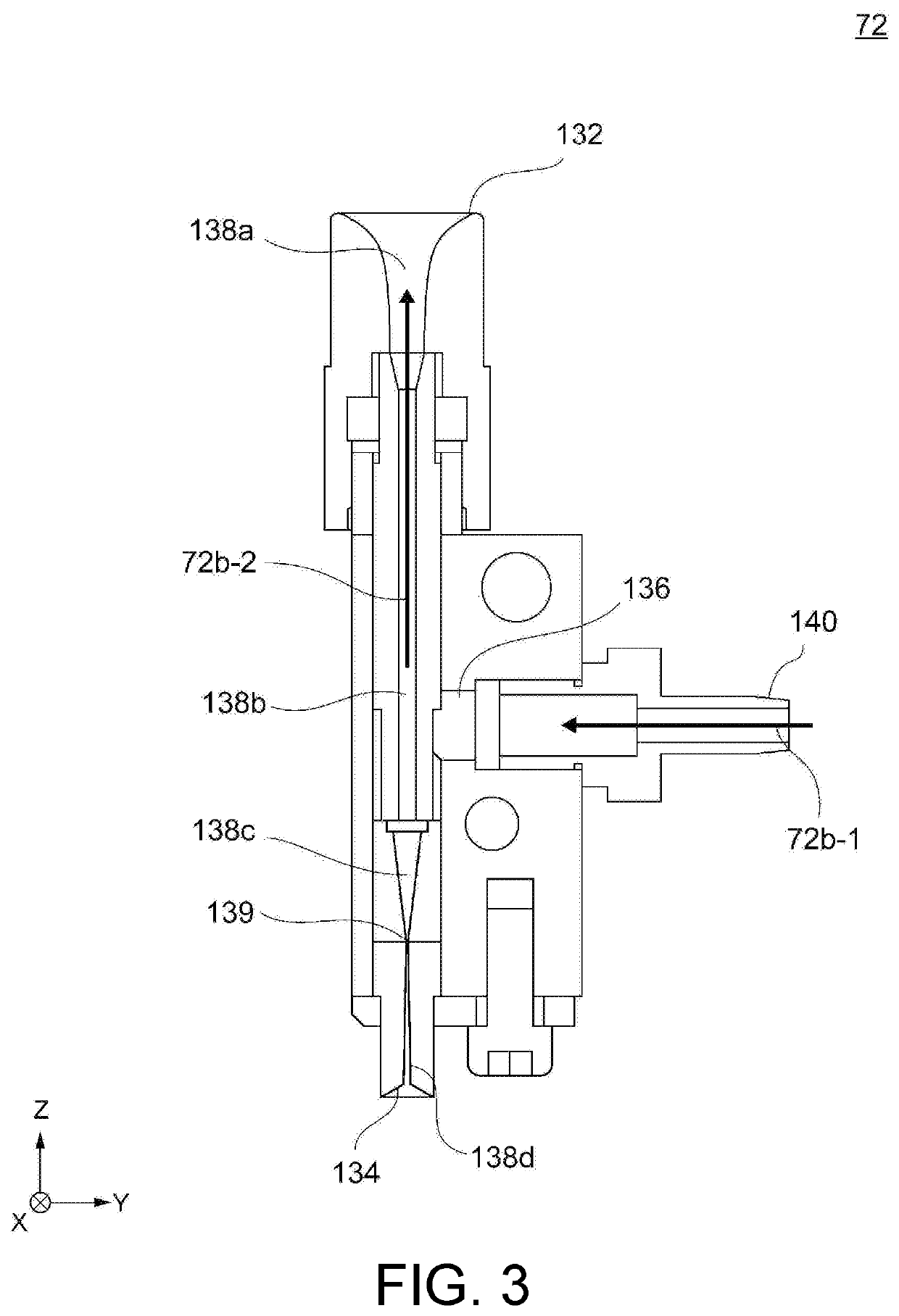

[0020]FIG. 1 is a diagram showing an overall outline of a wire bonding apparatus of the embodiment. In addition, FIGS. 2(A) and 2(B) are partially enlarged views of a bonding arm in the wire bonding apparatus. Specifically, FIG. 2(A) shows a top view of the bonding arm, and FIG. 2(B) shows a bottom view of the bonding arm. FIG. 3 is a diagram showing details of a second tensioner.

[0021]As shown in FIG. 1, a wire bonding apparatus 1 includes an XY drive mechanism 10, a Z drive mechanism 12, a bonding arm 20, an ultrasonic horn 30, a bonding tool 40, a load sensor 50, an ultrasonic vibrator 60, a first tensioner 70, a second tensioner 72, and a control part 80.

[0022]The XY drive mechanism 10 is configured to be slidable in an XY-axis direction (direction parallel to the bonding surface), and the Z drive mechanism (linear motor) 12 capable of swinging the bonding arm 20 in a Z-axis direction (direction perpendicular to the bonding surface) is arranged in the XY drive mechanism (linear ...

second embodiment

[0070]Next, a manufacturing method for semiconductor apparatus of a second embodiment of the present invention is described with reference to FIGS. 7(A)-7(G) and FIG. 8. FIGS. 7(A)-7(G) are schematic diagrams showing the operation, and FIG. 8 is a timing chart of FIGS. 7(A)-7(G). Besides, the times t4-t8 in FIGS. 7(A)-7(G) coincide with the times t4-t8 in FIG. 8. In the following embodiment, the same parts as those in the first embodiment are denoted by the same reference signs.

[0071]In the first embodiment, after the wire tail 42c connected to the wire loop 42a is formed, the wire tail 42d is formed by cutting off the wire 42 (FIGS. 5(F) and 5(D)). However, in the second embodiment, the wire tail 42c is formed at first after the wire 42 is cut off. In addition, in the second embodiment, the HIGH control is performed on both the first tensioner 70 and the second tensioner 72 in the period till time t5, and the OFF control is performed in the period from time t6a to time t7b. Hereina...

third embodiment

[0084]Next, a manufacturing method for semiconductor apparatus of a third embodiment of the present invention is described with reference to FIGS. 9(A)-9(F) and FIG. 10. FIGS. 9(A)-9(F) are schematic diagrams showing the operation, and FIG. 10 is a timing chart of FIGS. 9(A)-9(F). Besides, the times t4-t8 in FIGS. 9(A)-9(F) coincide with the times t4-t8 in FIG. 10. In the following embodiment, the same parts as those in the first embodiment are denoted by the same reference signs.

[0085]The third embodiment is the same as the first embodiment in terms of forming the wire tail 42d by cutting off the wire 42 after forming the wire tail 42c connected to the wire loop 42a. The third embodiment is different from the first embodiment in that the HIGH control is performed on both the first tensioner 70 and the second tensioner 72 in the period till time t4 and the OFF control is performed in the period from time t5 to time t6b. Hereinafter, points different from the first embodiment are des...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More