Method for controlling a non-volatile semiconductor memory device

a non-volatile semiconductor and memory device technology, applied in the direction of static storage, digital storage, instruments, etc., can solve the problems of interference noise, becoming more difficult to avoid interference noise between adjacent cells, and noise interferen

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040]Illustrative embodiments of this invention will be explained with reference to the accompanying drawings below.

[0041]Basic Configuration and Basic Write-control Scheme

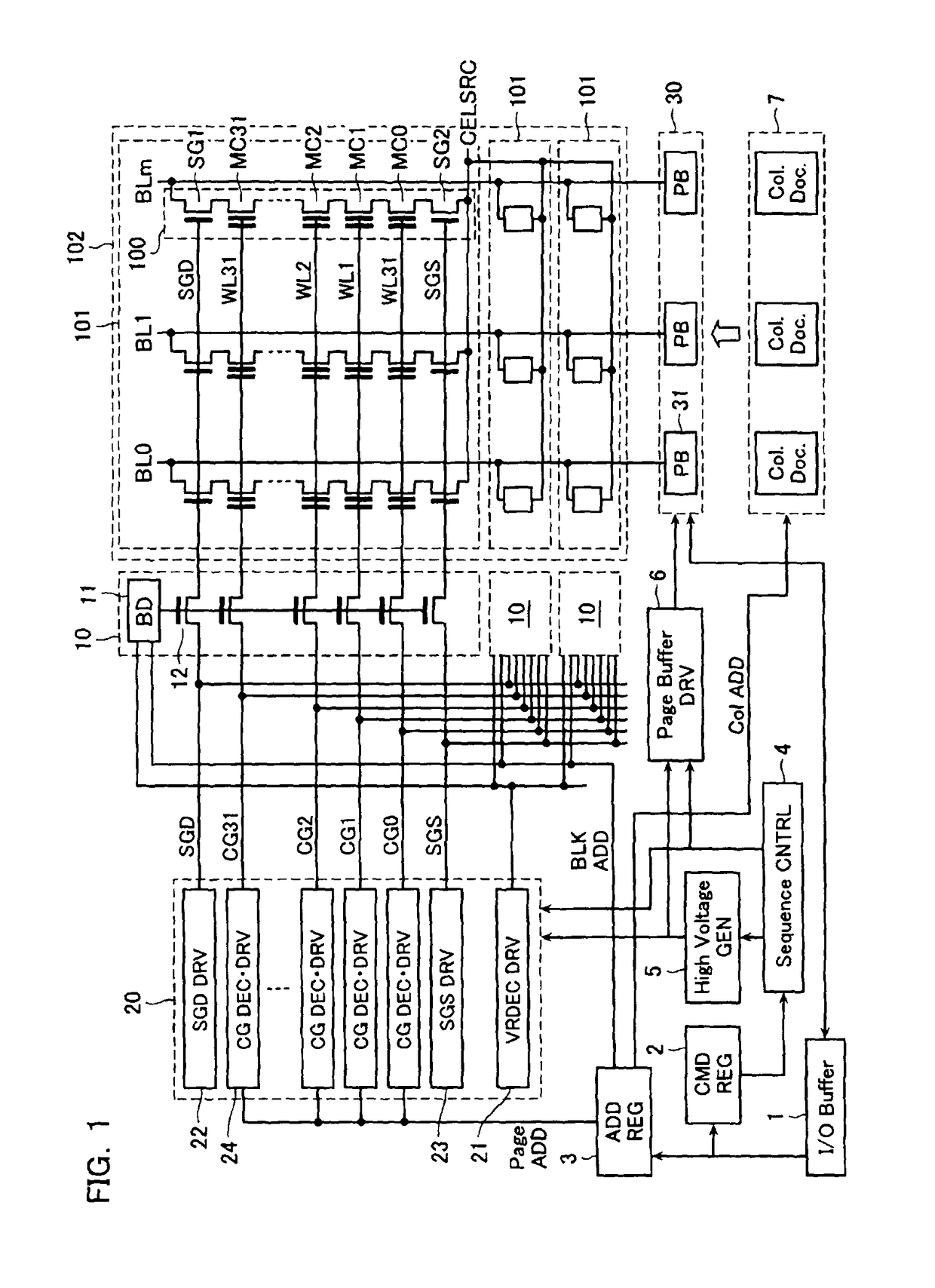

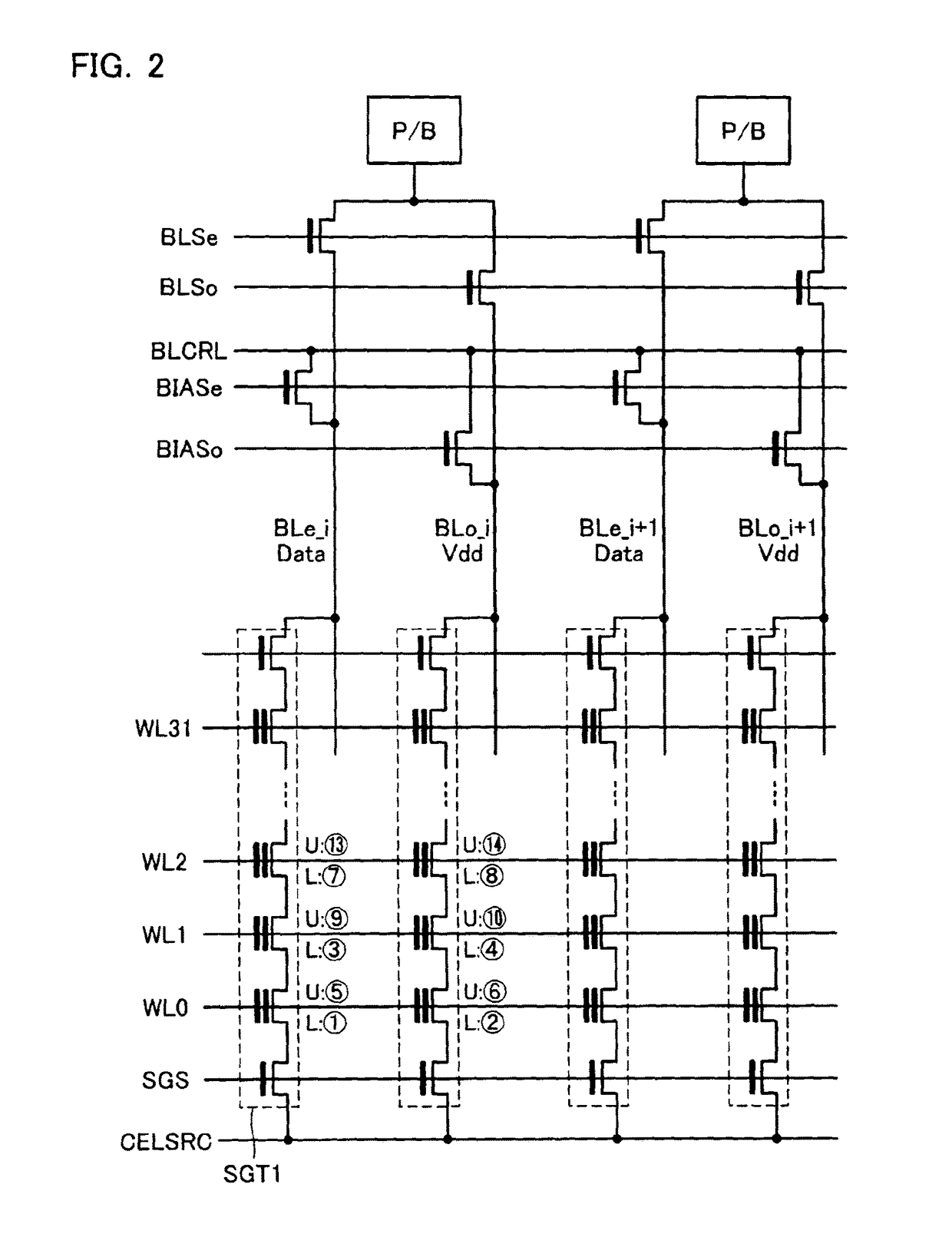

[0042]FIG. 1 shows the whole configuration of a NAND-type flash memory in accordance with an embodiment. NAND cell unit (i.e., NAND string) 100, which is a basic unit of the NAND-type flash memory, has plural memory cells MC0-MC31 connected in series and two select gate transistors SG1 and SG2 disposed at the both ends.

[0043]One end of NAND cell unit 100 is coupled to bit line BL via the select gate transistor SG1; and the other end is coupled to common source line CELSRC via the select gate transistor SG2.

[0044]One memory cell has N-type source and drain diffusion layers formed on a P-well formed on a silicon substrate, and a stacked gate structure with a floating gate and a control gate stacked above the channel region defined by the source and drain layers. ChangingBy changing the charge amount held in the flo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com