Address multiplexing logic implementation method with SDRAM compatible

A technology of address multiplexing and logic, which is applied in the field of compatibility between address multiplexing logic and SDRAM, and achieves the effects of simple software operation, convenient logic implementation, and fewer control signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

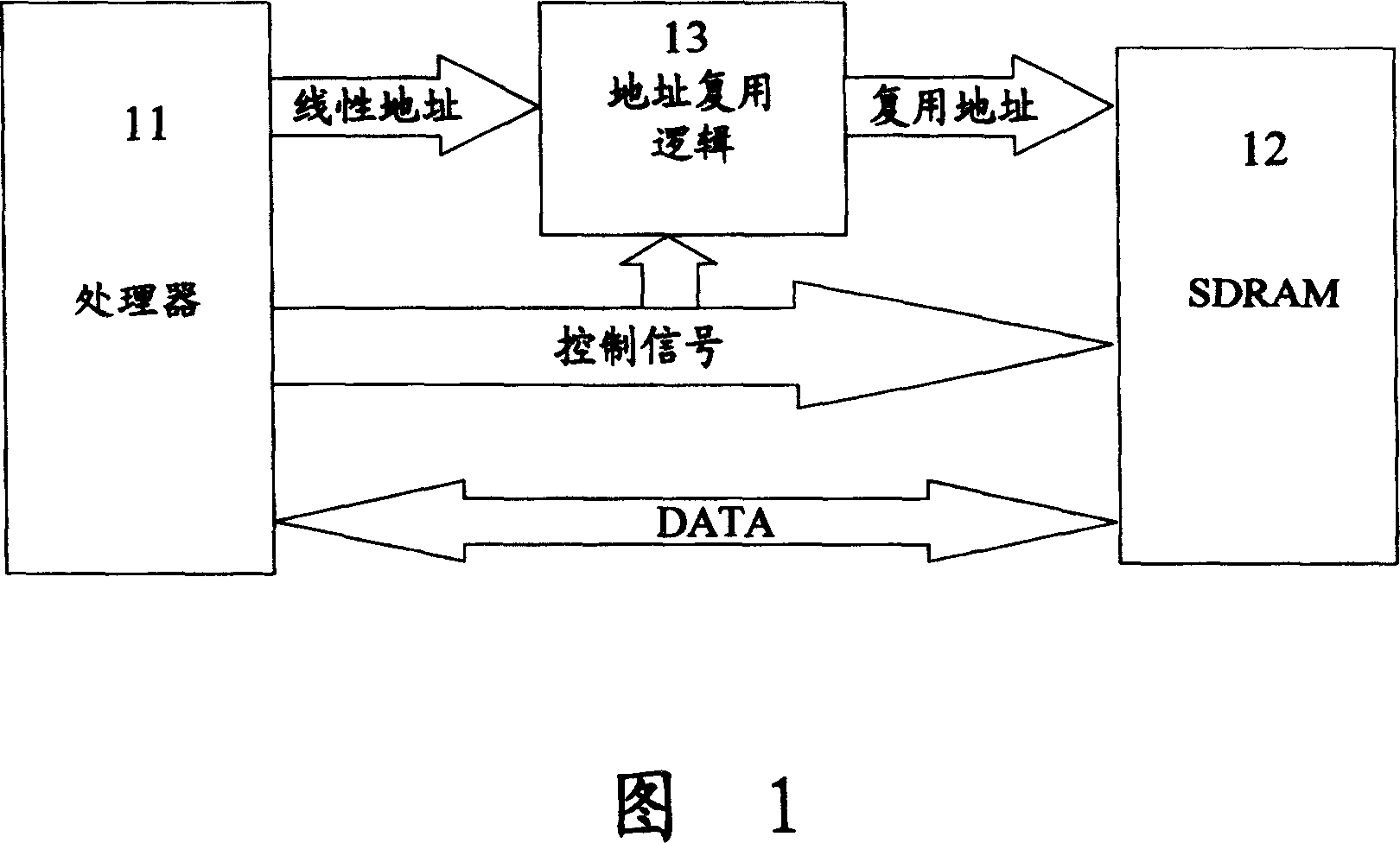

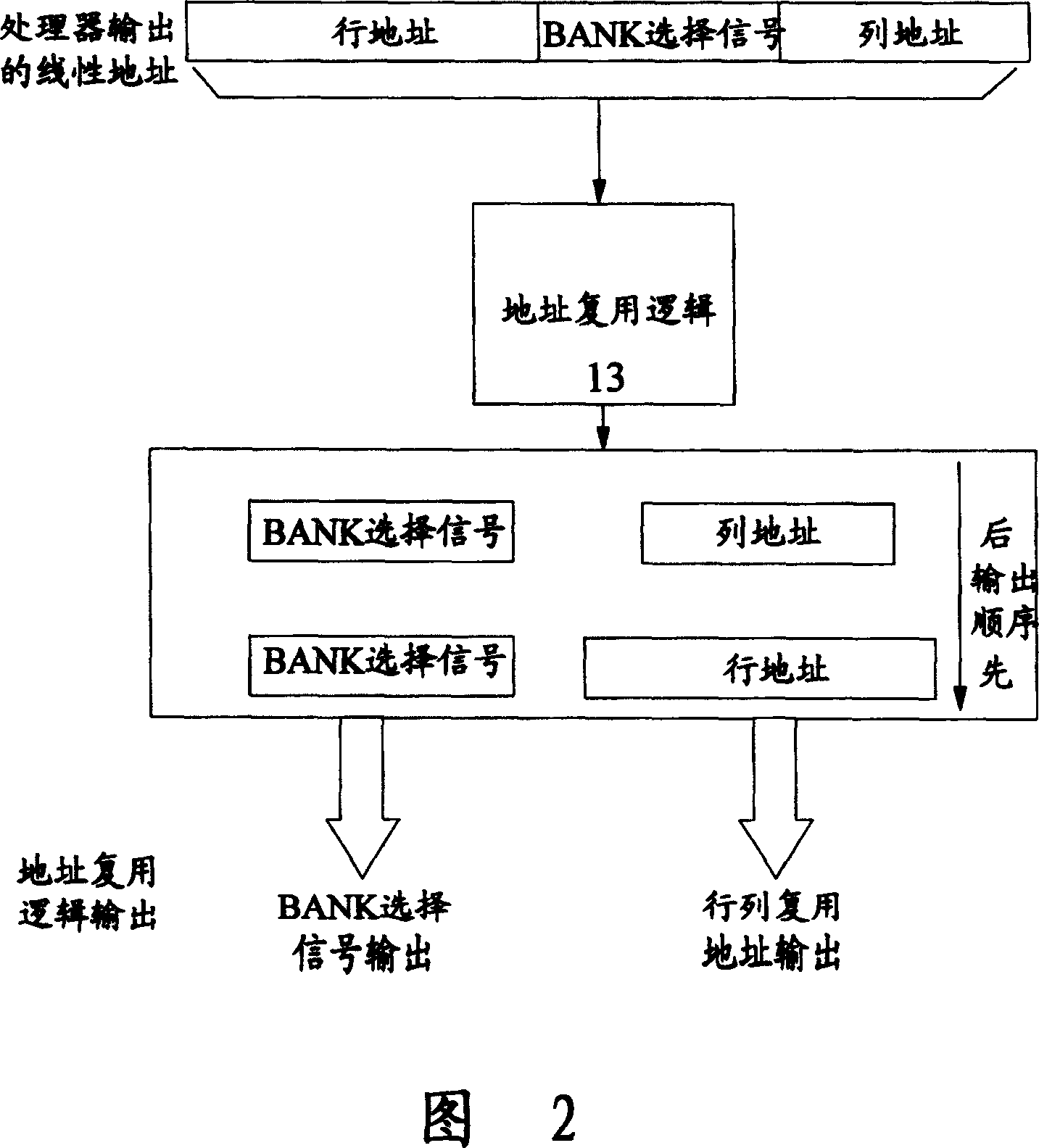

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

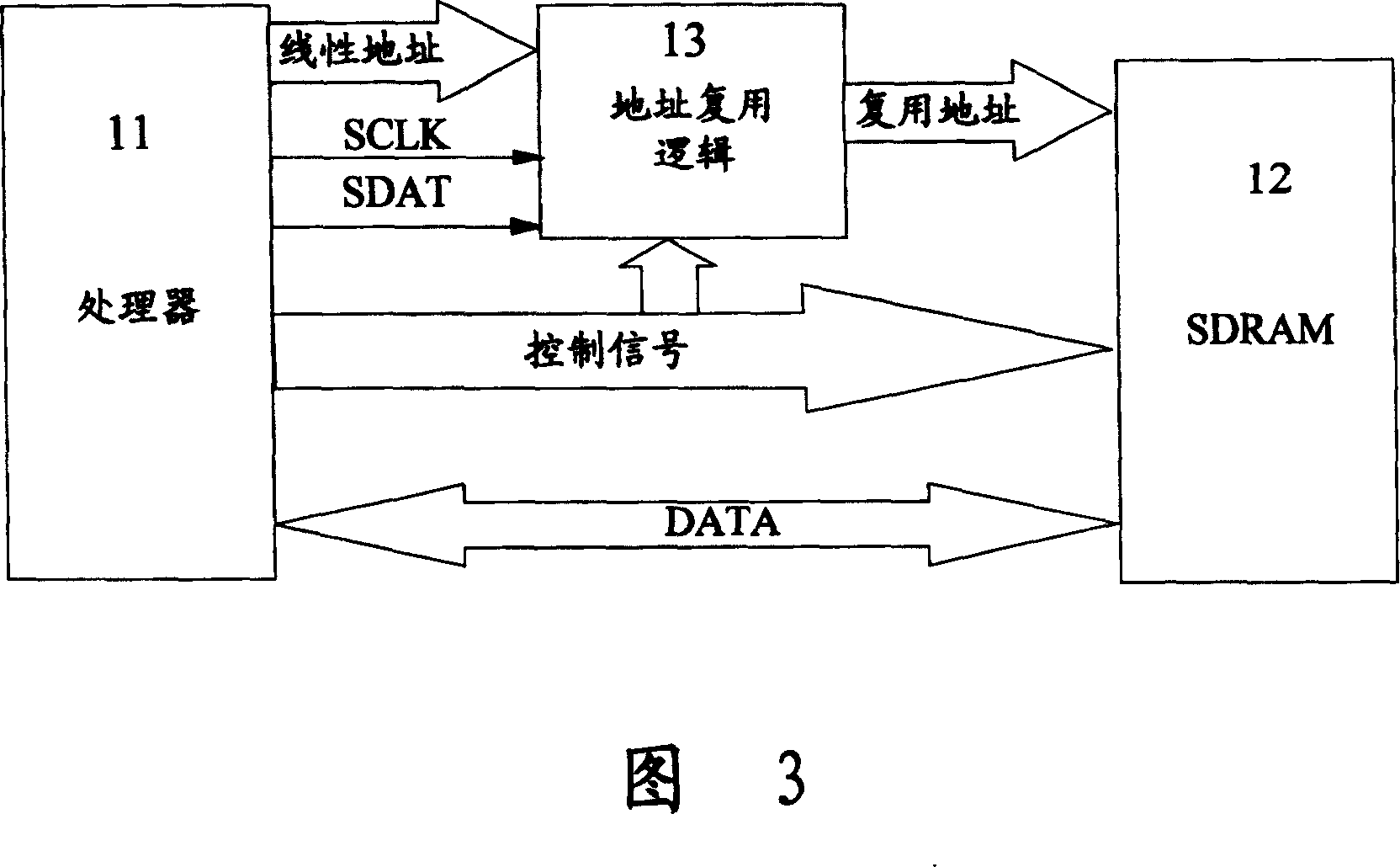

[0028] The object of the present invention is realized by adding an interface between the address multiplexing logic unit and the processor, including a clock signal line (SCLK) and a data signal line (SDAT).

[0029] Processor I / O

foot name

signal direction

Defaults

SCLK

Processor --> Address Multiplexing

logic unit

Clock line, address multiplexing logic unit sampling reception

The clock SCLK required for SDAT, the clock passes through

The SCLK line is sent to the address multiplexing logic unit

high level

SDAT

Processor --> Address Multiplexing

logic unit

data line, used to send SDRAM driver information, the

Driver information is sent by the processor via the SDAT line to the

Address multiplexing logic unit;

Processor on the falling edge (or rising edge) of SCLK

To send SDAT data, the address multiplexing lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More