Non-volatile memory and making method

A non-volatile, manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of increasing process cost and time spent, complicated steps, expensive, etc., to prevent short-circuit phenomenon, The effect of saving manufacturing cost and preventing short circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

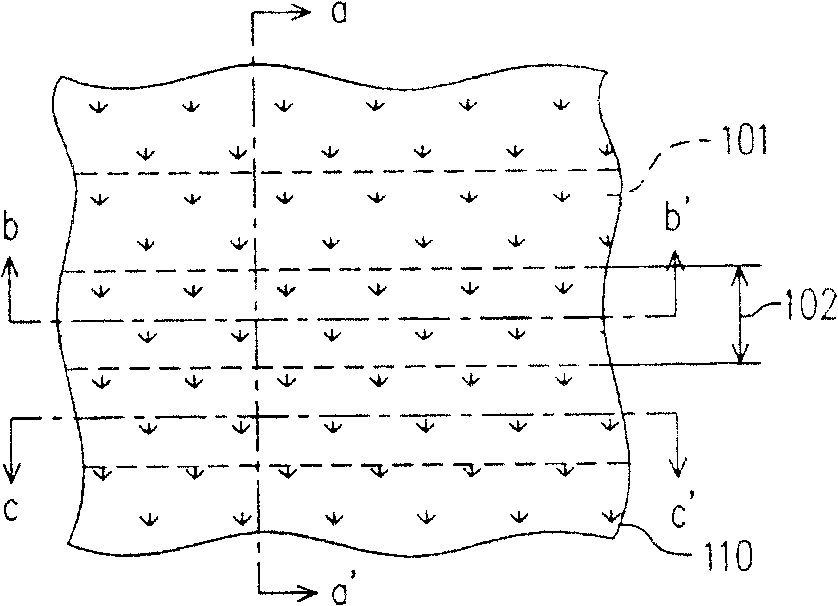

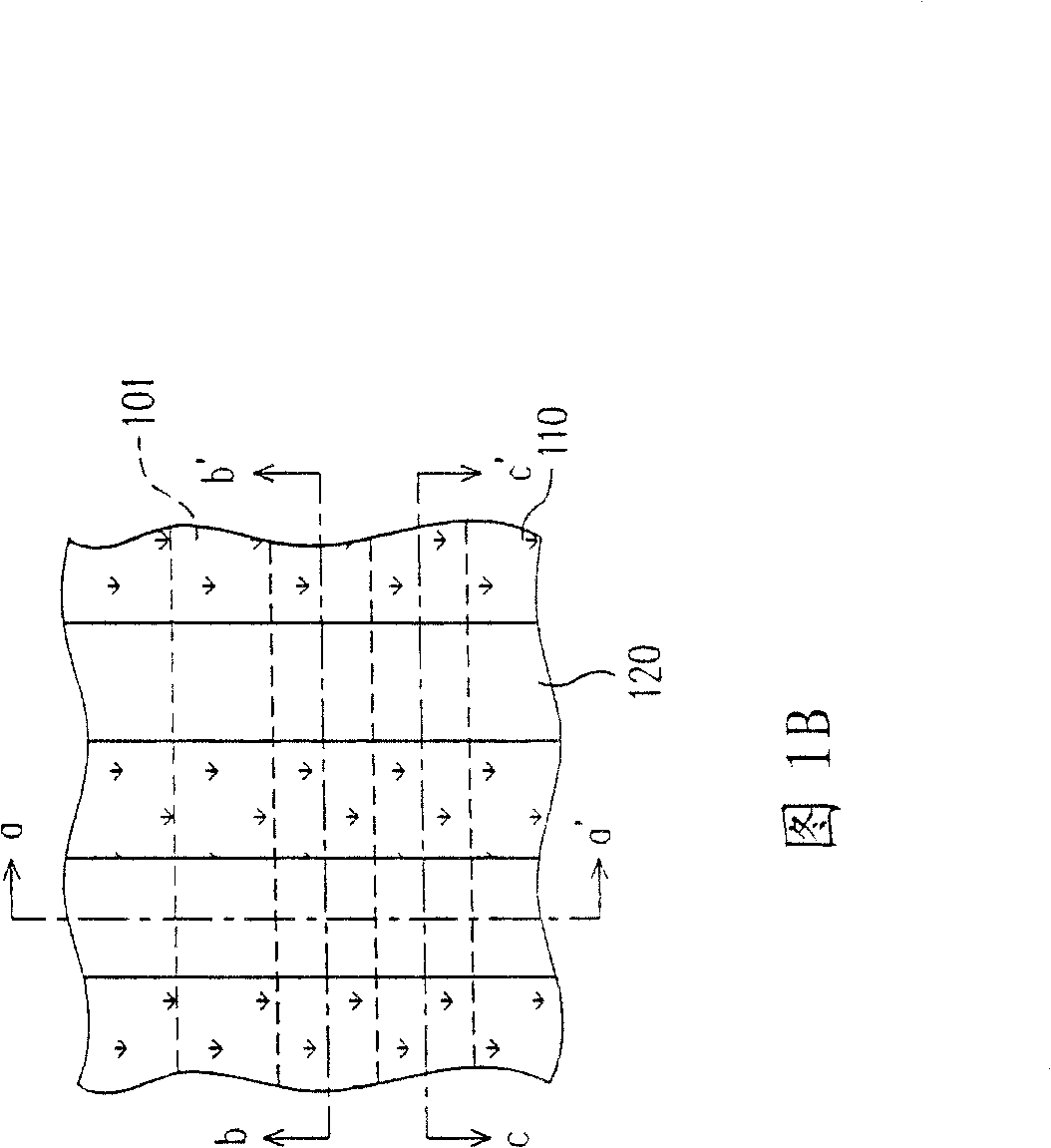

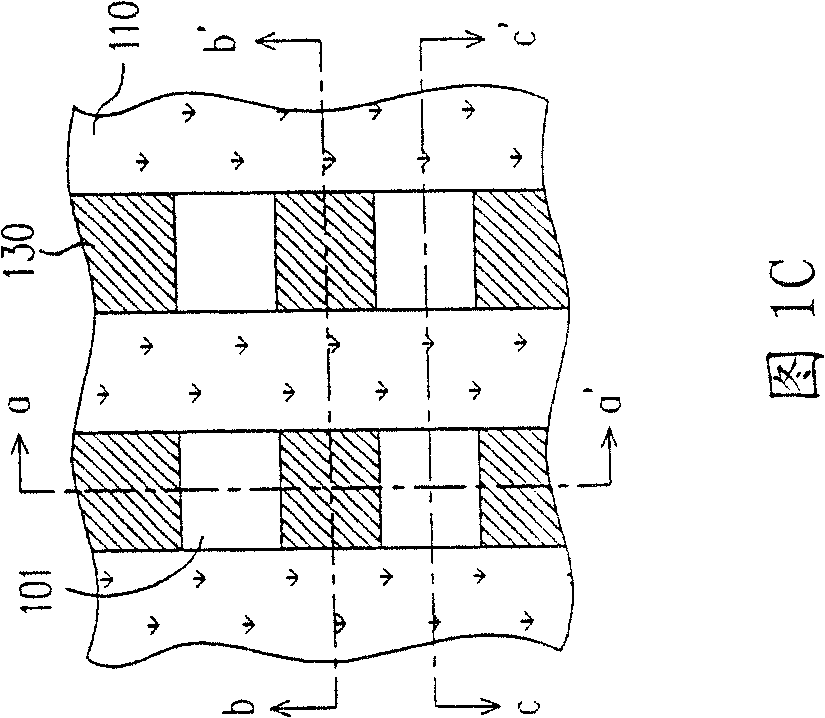

[0049] Figure 1A FIG. 1F shows a top view of the manufacturing process of a non-volatile memory according to an embodiment of the present invention. Figure 2A to Figure 2F respectively show Figure 1A To the schematic cross-sectional view along the a-a' line in Fig. 1F. Figure 3A to Figure 3F respectively show Figure 1A To the schematic cross-sectional view along b-b' line in Fig. 1F. Figure 4A to Figure 4F respectively show Figure 1A To the schematic cross-sectional view along c-c' line in Fig. 1F. Wherein, the line a-a' is a cutting line along the word line; the line b-b' is the cutting line along the active region; c-c' is the cutting line along the isolation structure.

[0050] The manufacturing method of the non-volatile memory proposed by the present invention is, for example, suitable for forming a flash memory of a NAND gate array. Of course, the manufacturing method can also be used to form other types of non-volatile memory. Please refer to Figure 1A , FIG. 2A ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More