Non-volatile storage and its producing method

A non-volatile, manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as increased manufacturing costs, heat dissipation and noise, and obstacles to increasing memory accumulation, and achieve shortening Manufacturing process, reduction of manufacturing cost, and effect of reduction in the number of photomasks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

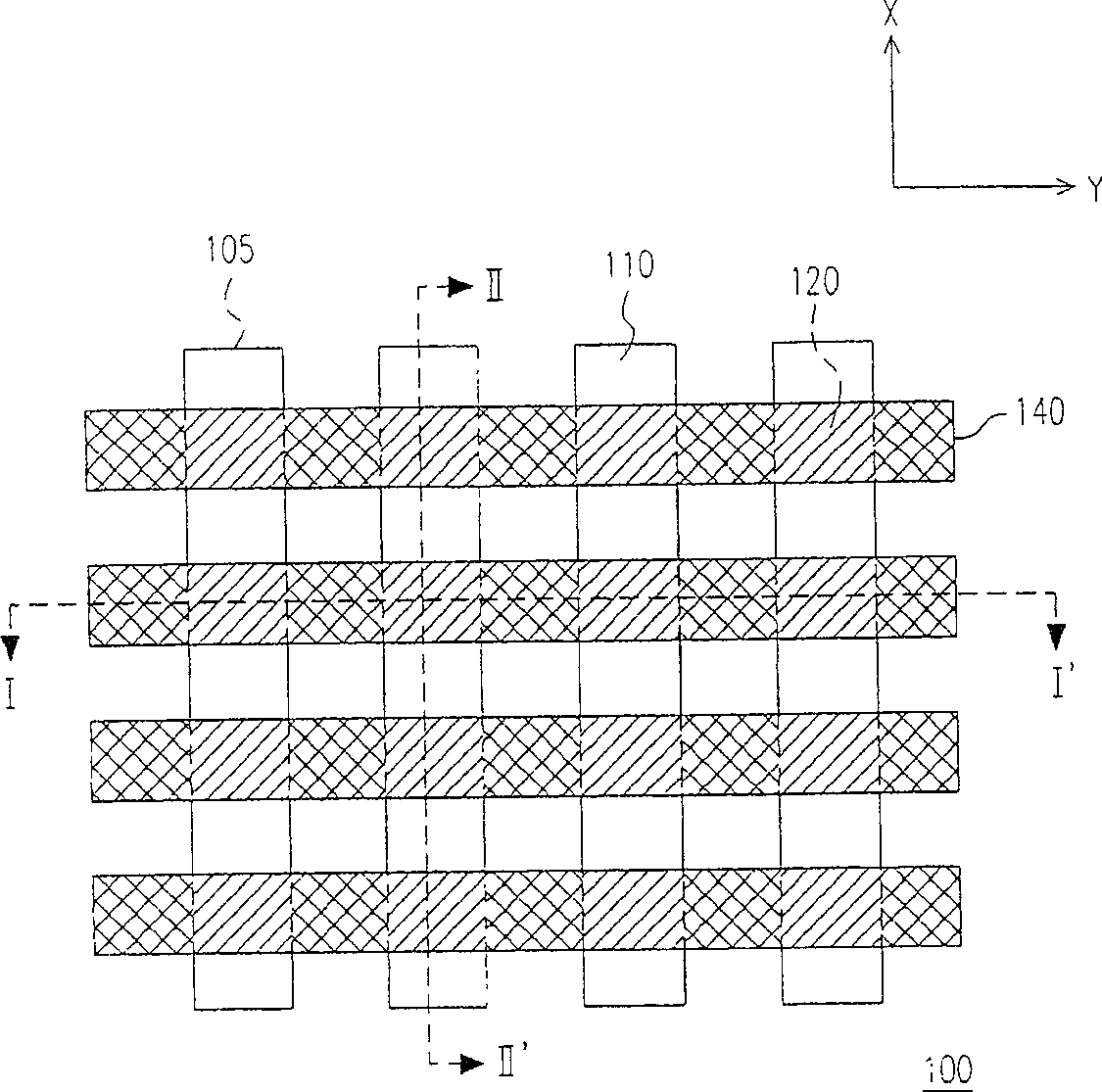

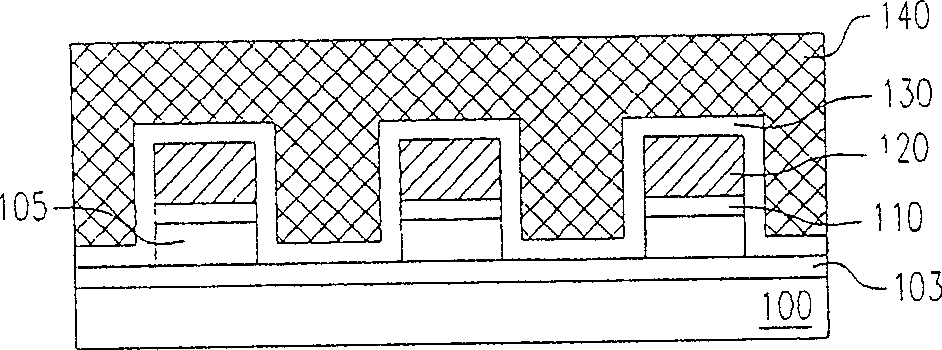

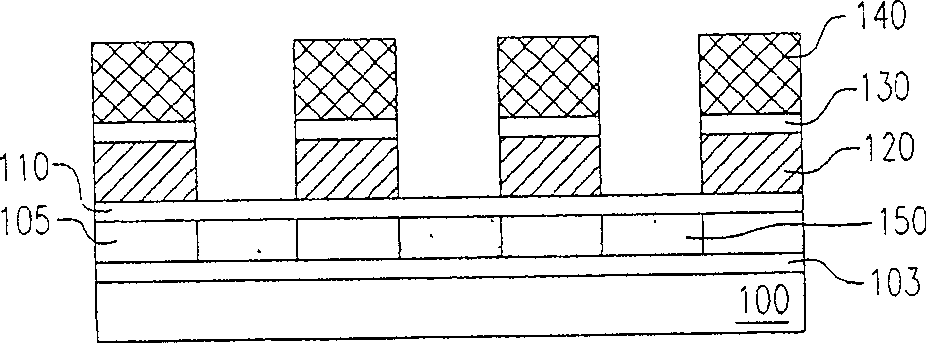

[0040] Figure 1A It is a top view of a non-volatile memory according to an embodiment of the present invention. Figure 1B and Figure 1C to draw separately Figure 1A The cross-sectional view of the structure along the line I-I' and line II-II'.

[0041] Please refer to Figure 1A , Figure 1B and Figure 1C , this non-volatile memory is, for example, a NAND flash memory, which is at least composed of a substrate 100, an insulating layer 103, a plurality of body layers 105, a plurality of tunneling dielectric layers 110, and a plurality of floating gates electrode 120 , a plurality of inter-gate dielectric layers 130 , a plurality of control gates 140 and a plurality of doped regions 150 .

[0042] For example, an insulating layer 103 is disposed on the surface of the substrate 100 . The main body layer 105 is disposed on the base 100 , and the main body layer 105 is arranged in strips in parallel and extends toward the X direction. The control gates 140 are, for exampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More