Low trigger voltage silicon control rectifier and its circuit

A technology of silicon controlled rectifier and low trigger voltage, which is applied in circuits, electric solid-state devices, electrical components, etc., and can solve problems such as the inability to use power protection and the inability to eliminate the locked state

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

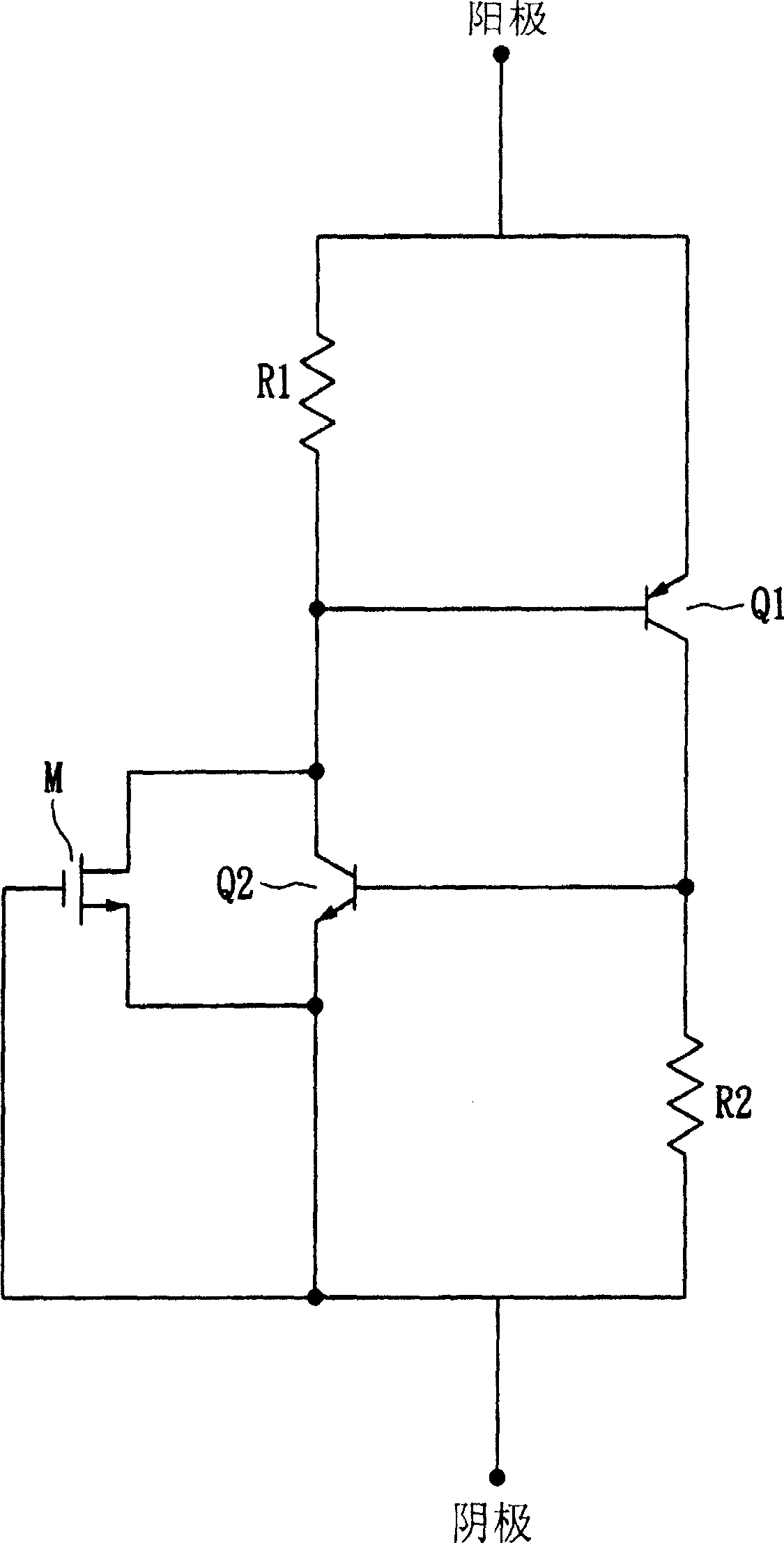

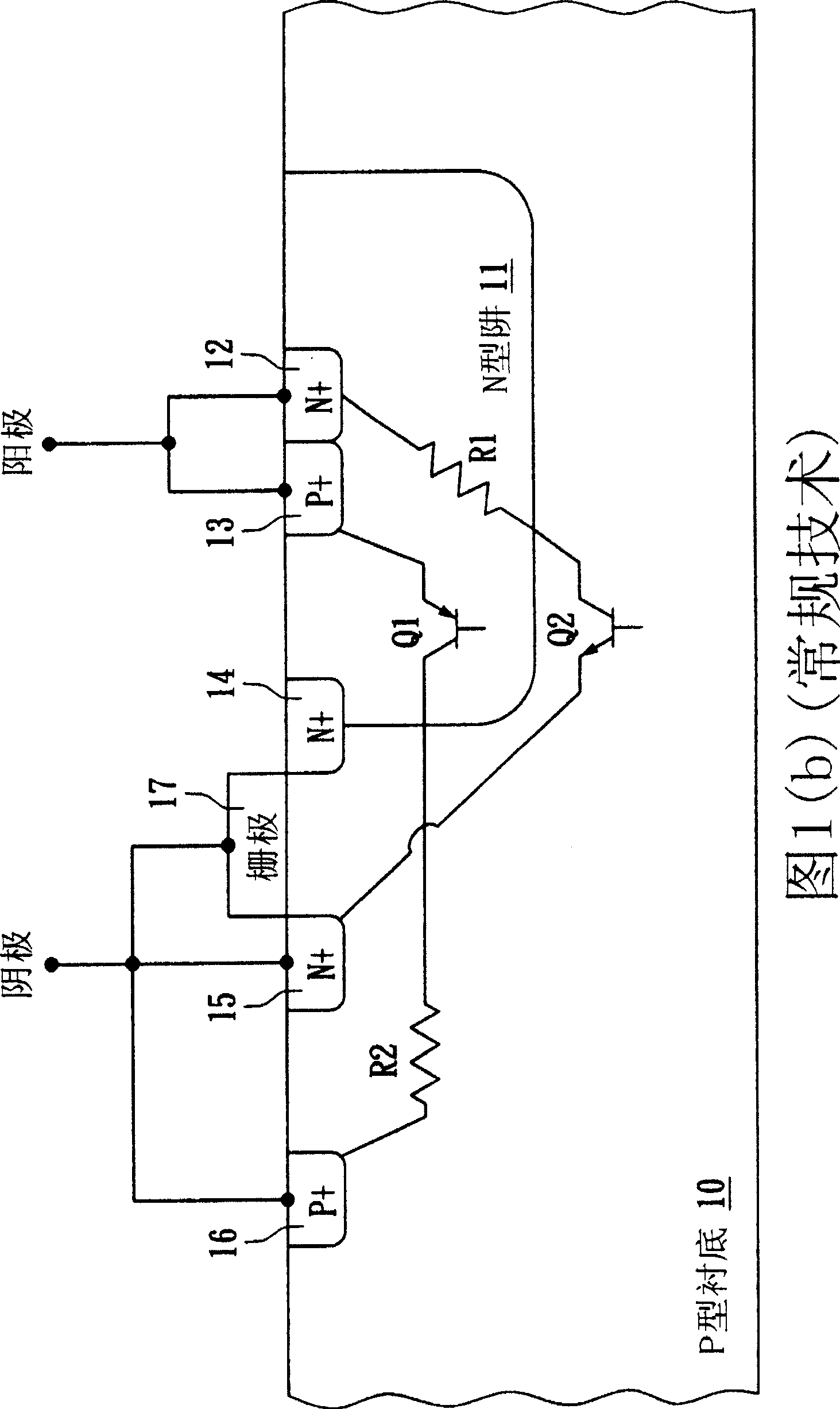

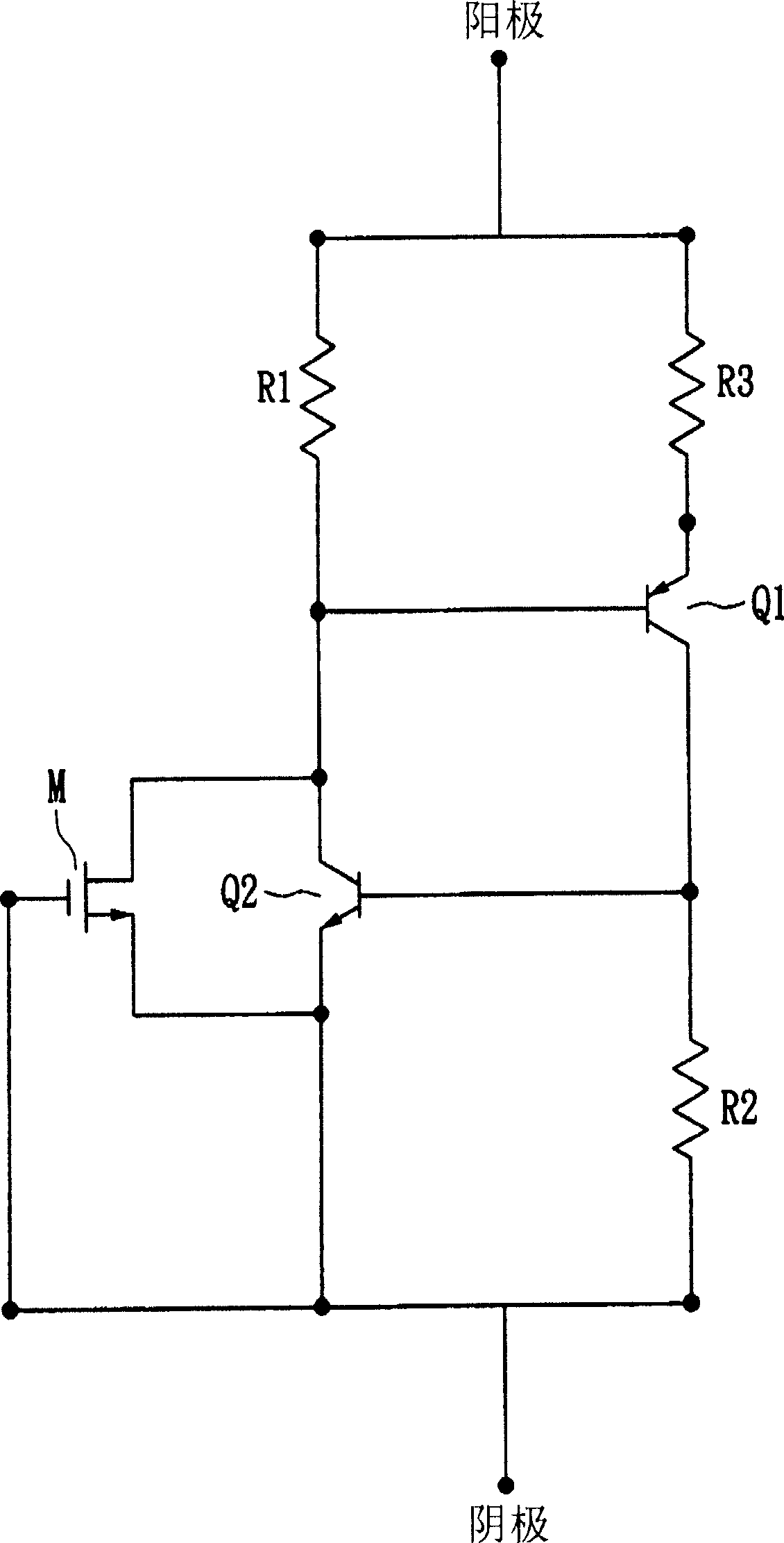

[0022] figure 2 It is the equivalent circuit of the low trigger voltage silicon-controlled rectifier of the present invention, which is to add a resistor R3 between the anode and the emitter of the parasitic bicarrier PNP transistor Q1 in the circuit of FIG. 1(a). Its operating principle is as follows. Because the breakdown voltage of the NMOS transistor M is lower than the breakdown voltage of the parasitic bicarrier NPN transistor Q2, when an ESD occurs, the NMOS transistor M is first turned on, and the current conduction acting on the NMOS transistor M will make a and The parasitic bipolar NPN transistor Q2 coupled with the resistor R2 is also turned on, and the current conduction of the parasitic bipolar NPN transistor Q2 will cause the parasitic bipolar PNP transistor Q1 to turn on. The current acting on the parasitic bipolar PNP transistor Q1 will accelerate the current conduction of the parasitic bipolar NPN transistor Q2, and finally enter into a locked state. At thi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More