Insulation layer and semiconductor conducting layer aligning error electrical testing structure in micro-electro-mechanical system

A micro-electromechanical system and alignment error technology, which is applied in semiconductor/solid-state device testing/measurement, electric solid-state devices, semiconductor devices, etc., can solve problems such as alignment error extraction, achieve consistent measurement methods, simple test equipment, and test The effect of simple method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

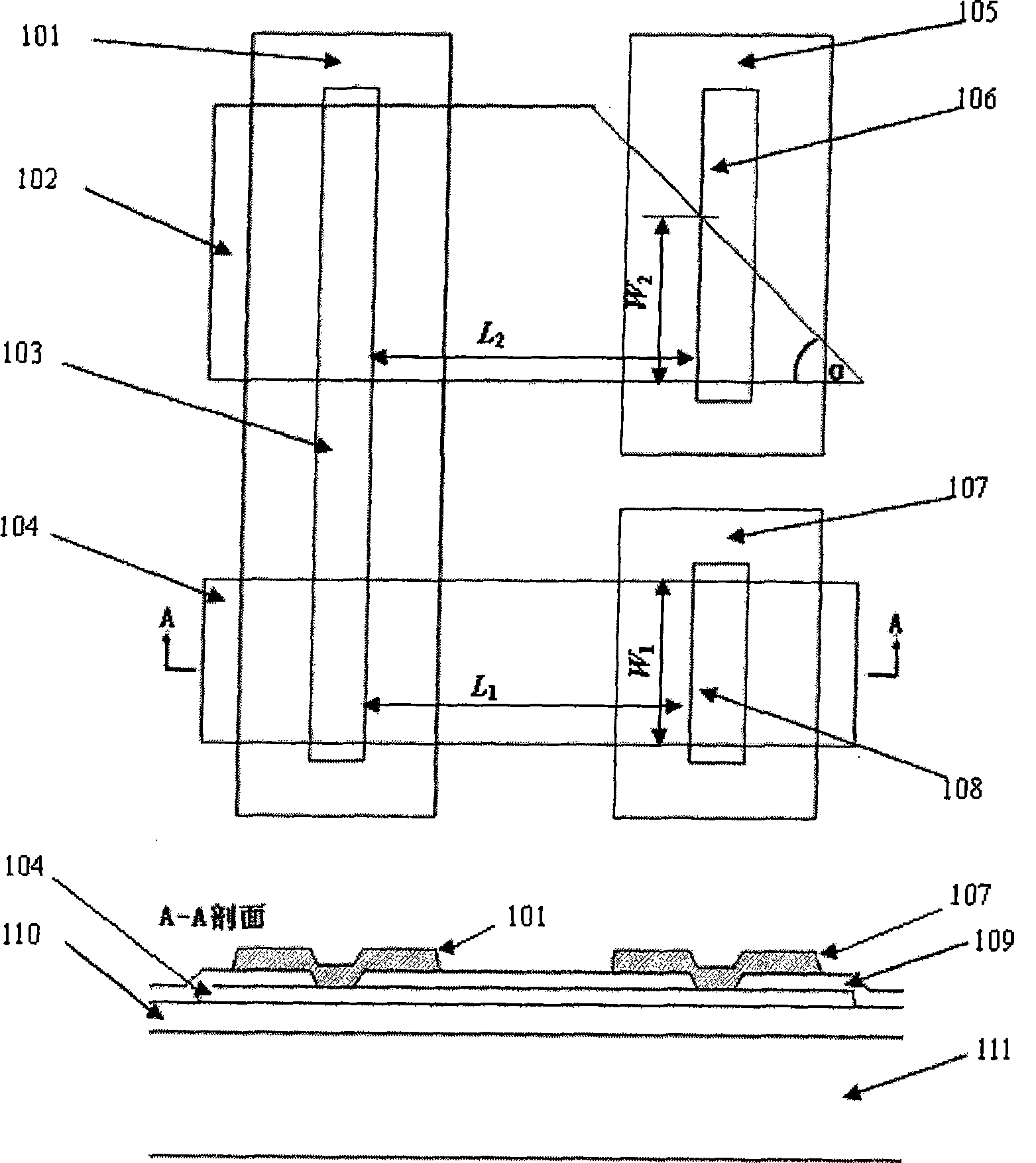

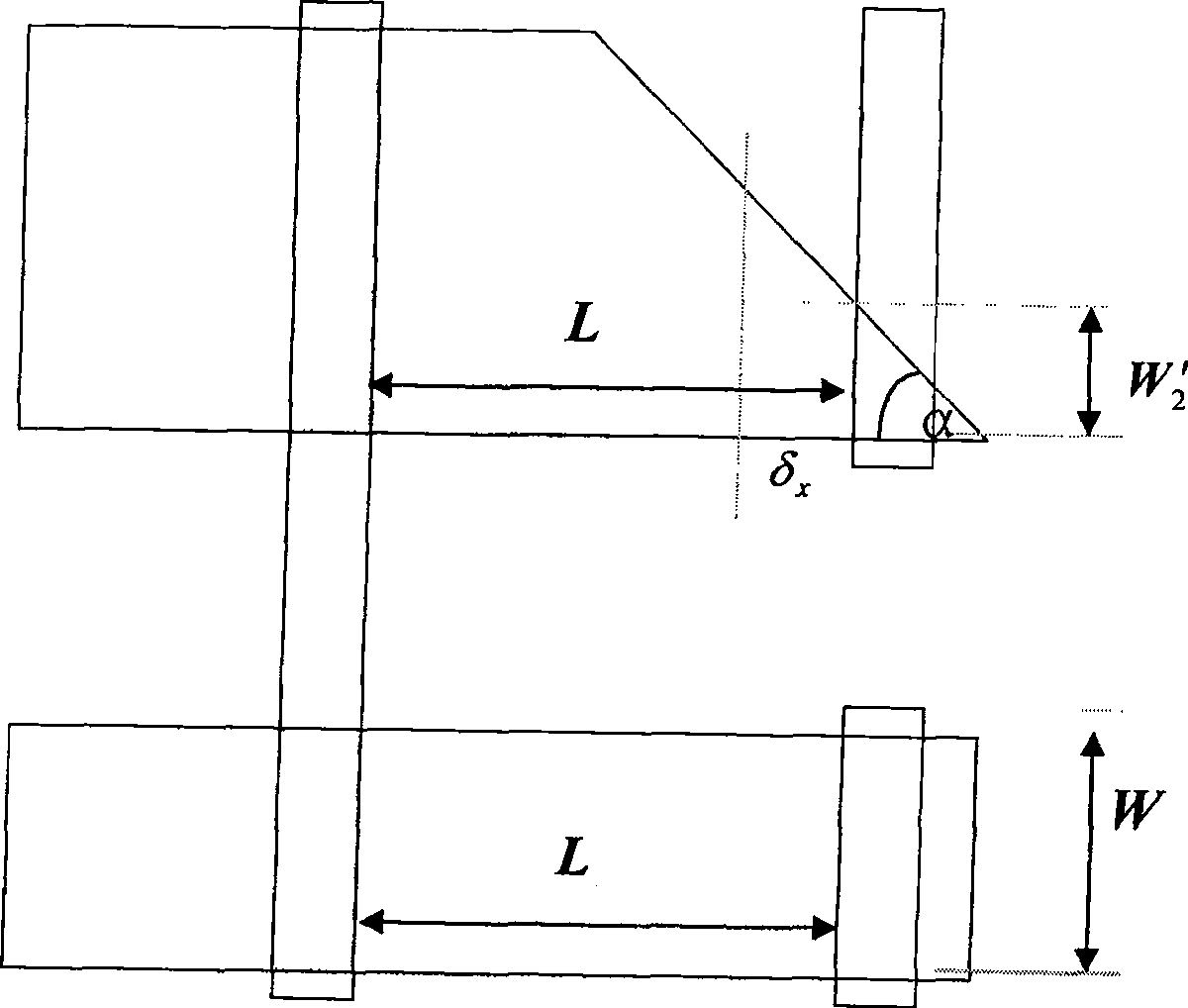

[0014] figure 1 The test structure pattern of the pattern error of the insulating layer pattern aligning with the semiconductor conductive layer pattern is given, and the cross-sectional structure of the structure is also given in the figure. In the test structure, 102 is a trapezoid and 104 is a rectangle. The materials of these two patterns are semiconductor material layers, which can be polysilicon 1 or polysilicon 2. They are both conductive due to doping. Of course, they must also be There is resistance. 103, 106, 108 are lead holes opened on the insulating layer 109, 101, 105, 107 are strip-shaped metal layers, covering the holes of the insulating layer, and their size is larger than the size of the holes to ensure that the metal pattern and insulation are When the layer pattern is offset, it can still completely cover the hole. 110 is an insulating material, usually silicon nitride. 111 is a silicon substrate. The semiconductor conductive layer between 103 and 108 f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More