Patents

Literature

79results about How to "Simple test equipment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

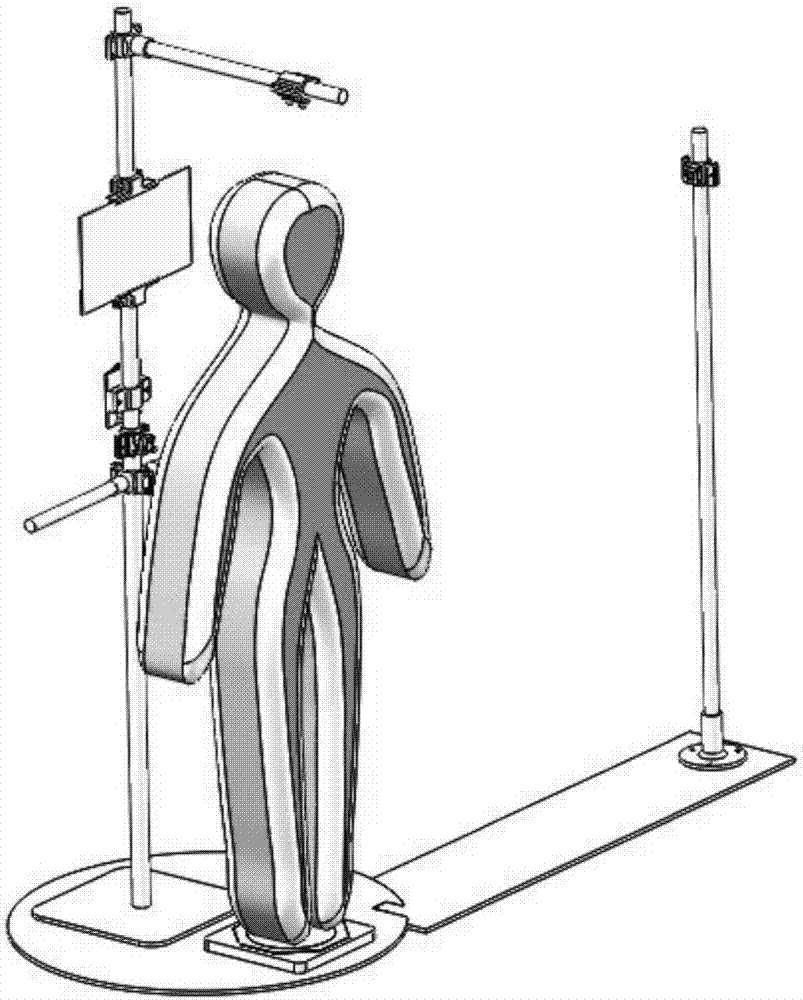

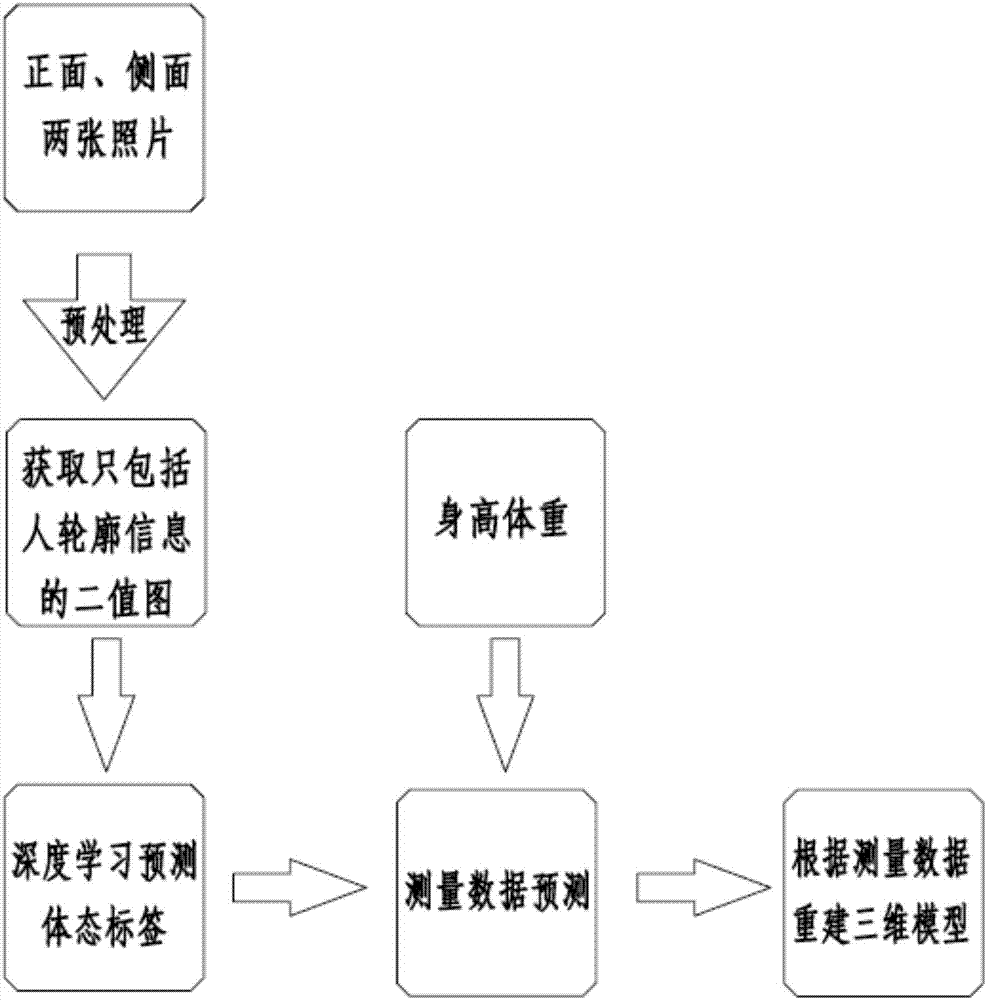

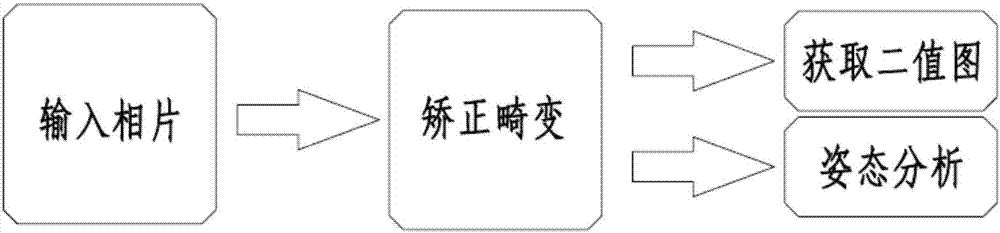

Method for predicting human body measurement data

ActiveCN107194987AEasy accessSimple test equipmentDiagnostic recording/measuringSensorsMeasurement deviceHuman body

The invention relates to a method for predicting human body measurement data, and solves the problems of complex and expensive used measurement device, test discomfort caused to a human body and difficulty in accurately recovering real posture data of the human body in an existing measurement method. The method comprises the steps of 1) establishing a model library; 2) generating a posture tag; 3) obtaining body height and body weight of the to-be-measured human body and photo information containing a to-be-measured part; 4) processing a photo into a binary image; 5) according to the established model library, performing deep convolutional neural network learning on the binary image; 6) predicting the posture tag of the to-be-measured human body according to a learning result; and 7) predicting measurement data of the to-be-measured human body. According to the method, input data is easy to obtain; the problem of complex input of an existing algorithm is solved; a test device is simple; and input information collection can be finished only by the simple device, so that the test cost is low.

Owner:XIAN SUANIER ELECTRONICS TECH

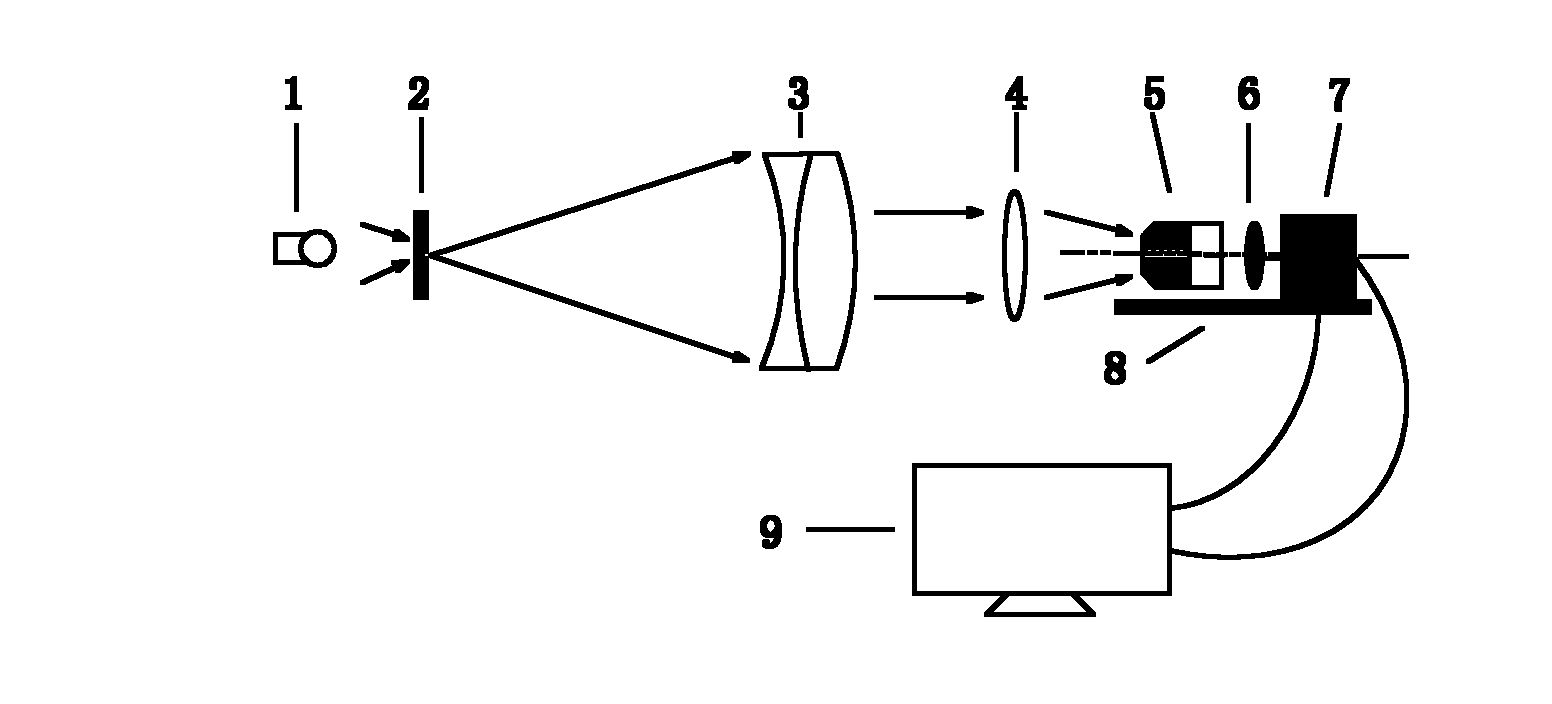

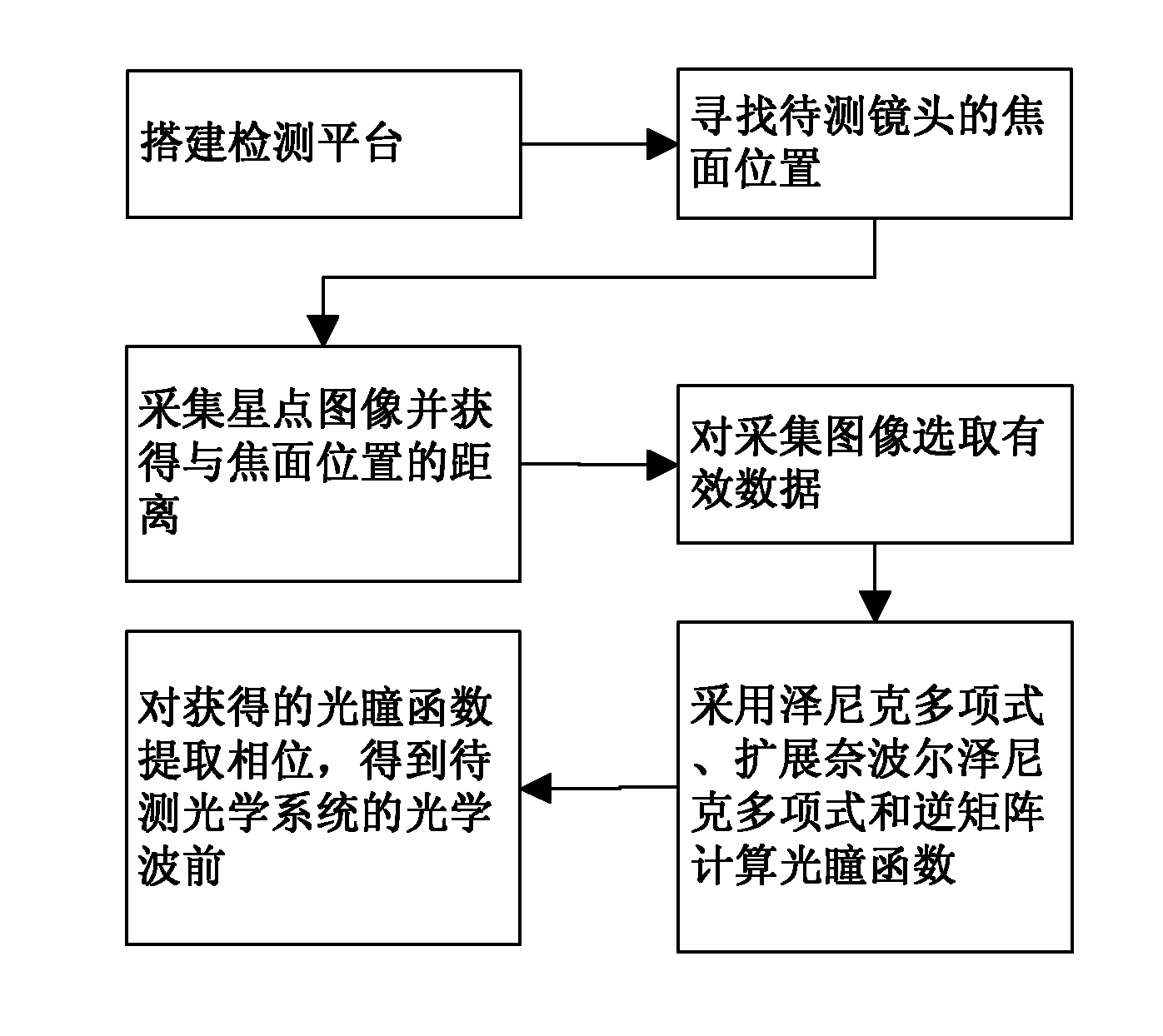

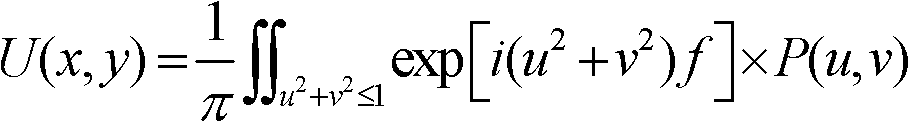

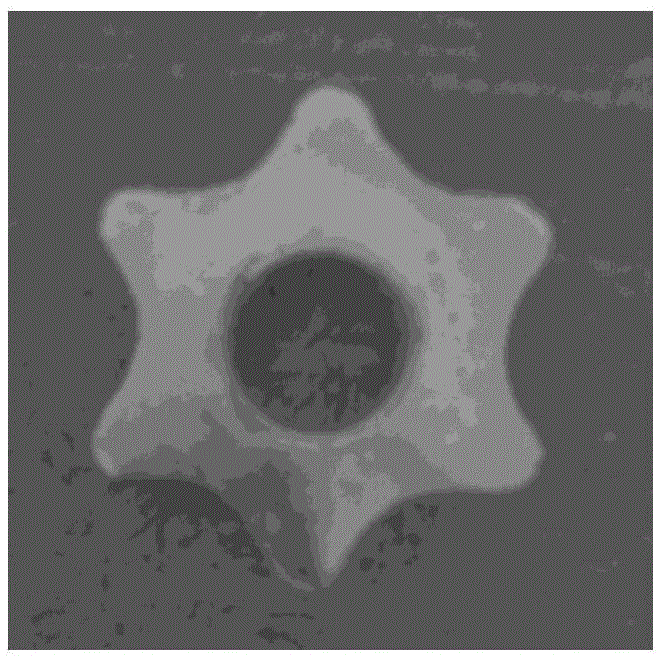

Single focal plane high-precision testing method for optical wavefront of optical imaging system

InactiveCN102252763ASolve for uniformitySolve the errorOptical measurementsPupil functionCalculation error

The invention discloses a single focal plane high-precision testing method for optical wavefront of an optical imaging system, relates to the technical field of optical testing, solves the problems that exit pupil amplitudes are not distributed uniformly and calculation errors are introduced by fast Fourier transform in the conventional phase retrieval algorithm, and provides the scheme for eliminating the influence of vibration in the process of image acquisition on detection accuracy. The method comprises the following steps of: establishing a detection platform of the optical imaging system; detecting the position of the focal plane of a lens to be detected by using a detection device in the detection platform and acquiring an out-of-focus stellar image of the lens to be detected by the detection device; selecting effective data according to the acquired out-of-focus stellar image and calculating a pupil function of an optical system; and extracting the phase of the acquired pupil function to obtain the optical wavefront of the optical imaging system. The pupil function of the optical system is calculated by a Zernike multinomial, an extended Nijboer-Zernike multinomial, and a generalized inverse matrix. The single focal plane high-precision testing method is low in cost, and high in accuracy and is suitable for manufacturing enterprises, scientific research and detection units of the optical imaging system.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

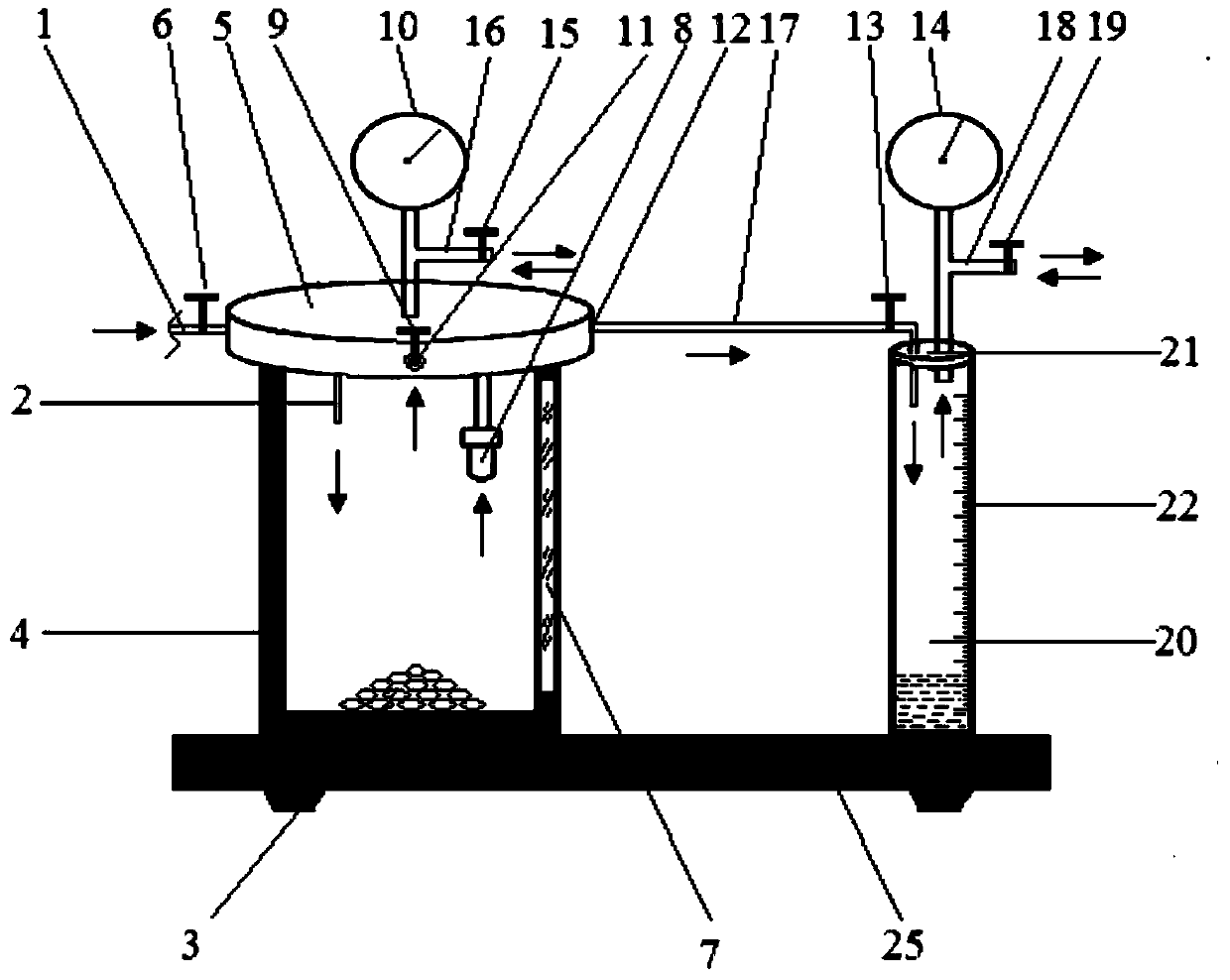

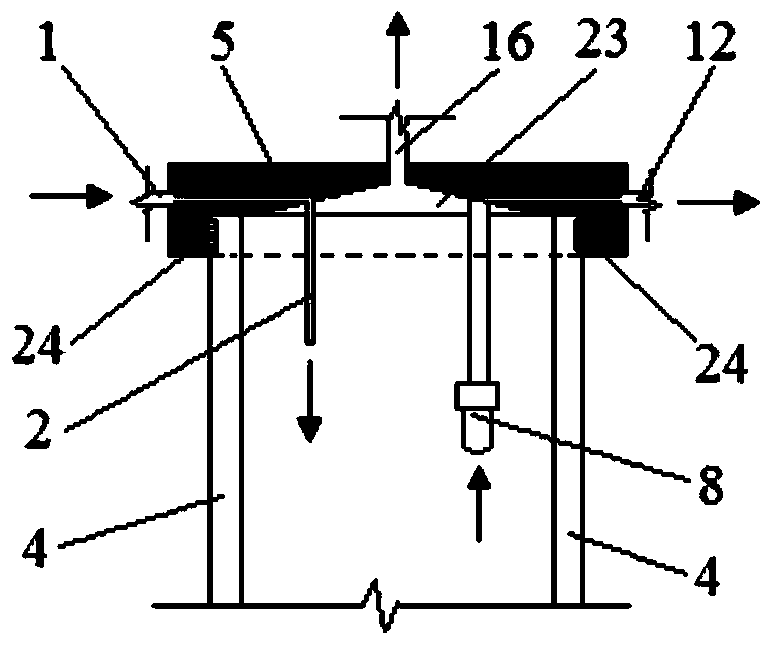

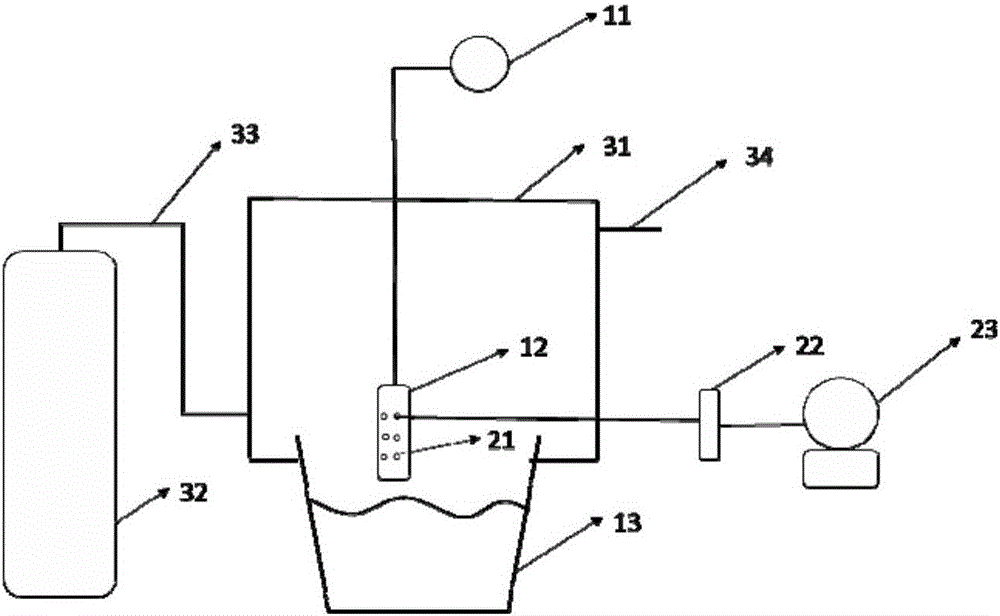

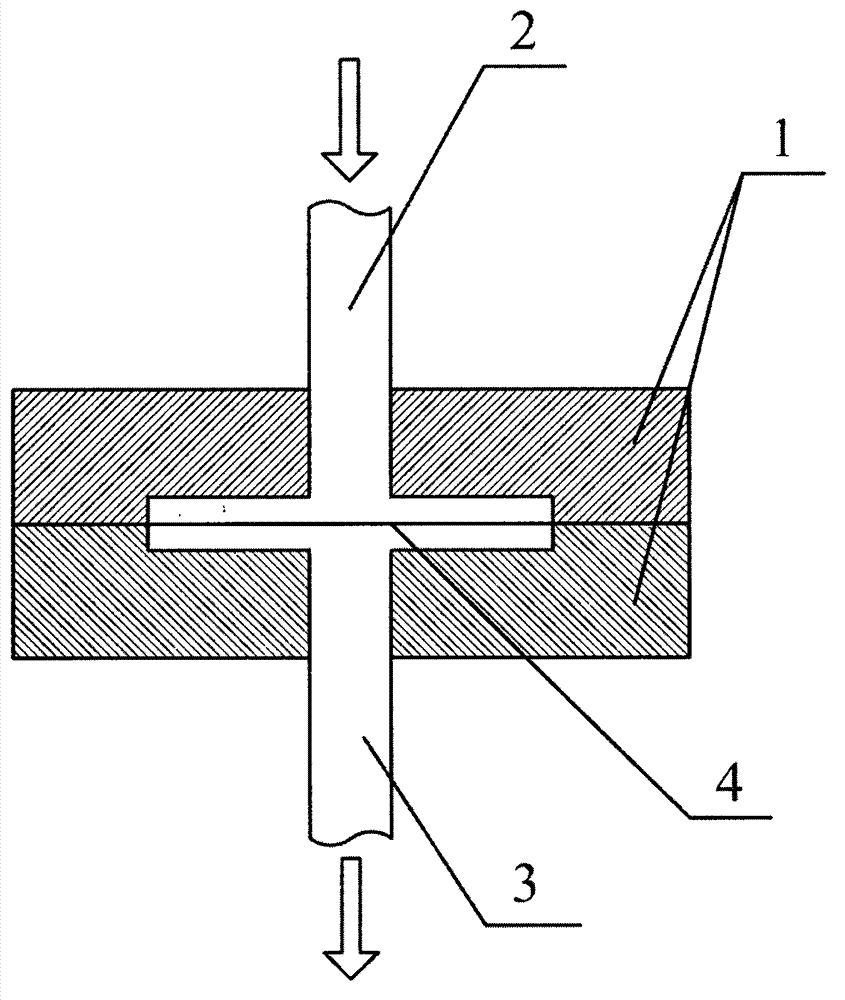

Variable-pressure controllable gas replacement reaction device and application thereof in preparation of gas-containing soil sample

ActiveCN103698186ASimple test equipmentThe operation process is easy to masterPreparing sample for investigationSpecific gravityChemistry

The invention belongs to the technical field of manually simulated sample preparation tests for gas-containing sediment in geotechnical engineering, and particularly discloses a variable-pressure controllable gas replacement reaction device and application thereof in preparation of a gas-containing soil sample. The device comprises a reaction vessel and a measuring cylinder which are fixed on the upper surface of the same base, and gas replacement reactions and accurate measurement of gas output under different pressure can be achieved through adjustment of pressure in the reaction vessel and the measuring cylinder; a quantitative relation between mass of gas-absorbable solid particles and replaced gas in different pressure environments under a constant temperature condition can be established; and artificial quantitative control for preparing the gas-containing soil sample is achieved based on the relation. For soil sample preparation, by means of specific crystal structure and high hydrophilicity of zeolite and due to the fact that the specific gravity of the zeolite is close to that of a soil particle, zeolite particles for absorbing saturated methane gas are uniformly mixed with the soil particles, then water is added, the methane gas absorbed in the zeolite particles is replaced by water, so that a bubble-containing soil body is formed, and the prepared gas-containing soil sample is uniform.

Owner:INST OF ROCK AND SOIL MECHANICS - CHINESE ACAD OF SCI

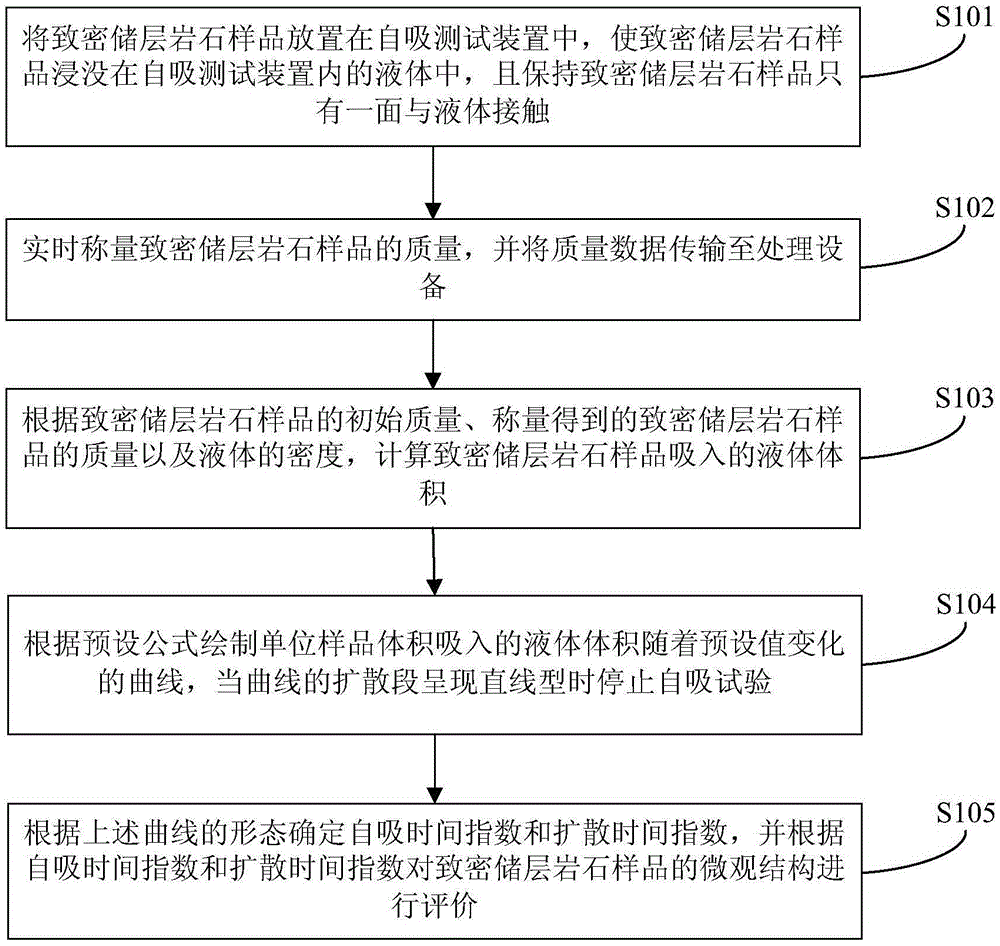

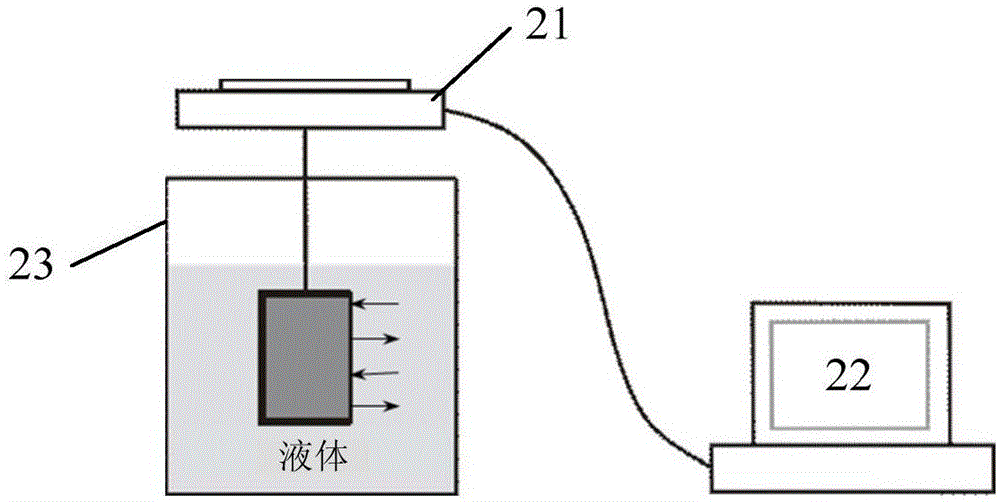

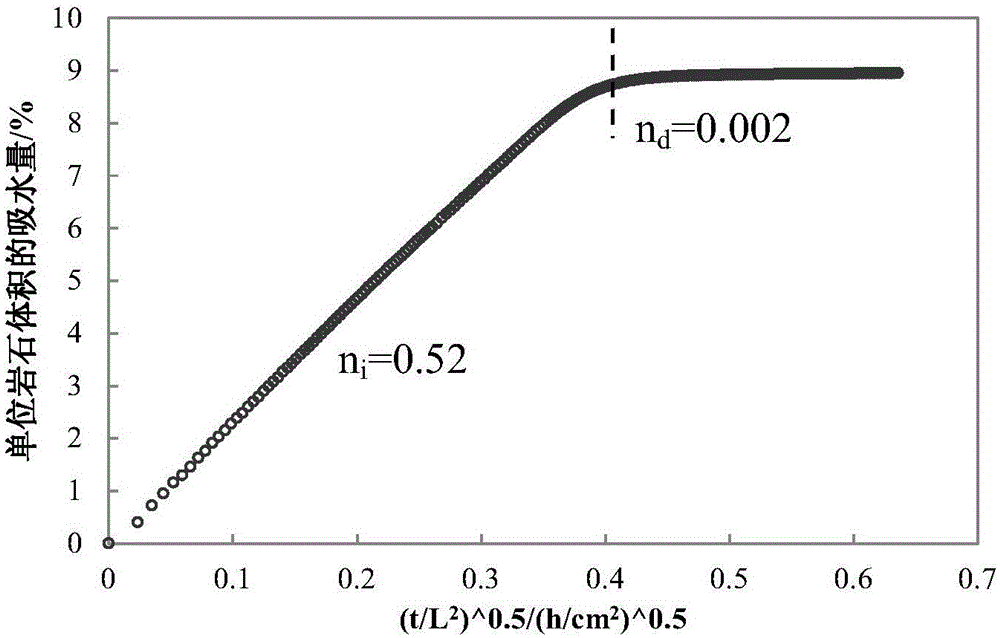

Method for evaluating microstructure of compact reservoir rock

InactiveCN105067795AImprove visibilitySimple test equipmentEarth material testingMicrostructureEnvironmental geology

The invention discloses a method for evaluating the microstructure of a compact reservoir rock. The method comprises the following steps: soaking a compact reservoir rock sample in a liquid in a self-absorption testing device, wherein only one surface of the sample contacts the liquid; weighing the sample in real time; calculating the volume of the liquid absorbed by the sample according to the initial sample weight, the weighed weight, and liquid density; according to a preset formula, drawing a curve representing the relationship between the volume of the absorbed liquid and the change of the preset values, stopping the self-absorption test, when the expansion section of the curve becomes linear; according to the shape of the curve to determine the absorption time index and diffusion time index, and evaluating the microstructure of the compact reservoir rock sample according to the self-absorption time index and the diffusion time index. The shortage that in the conventional methods, the self-absorption curve is difficult to recognize, is overcome; and the method can be used to carry out quantitative evaluation and research on matrix diffusion effect of compact reservoir rock and clay minerals.

Owner:CHINA UNIV OF PETROLEUM (BEIJING)

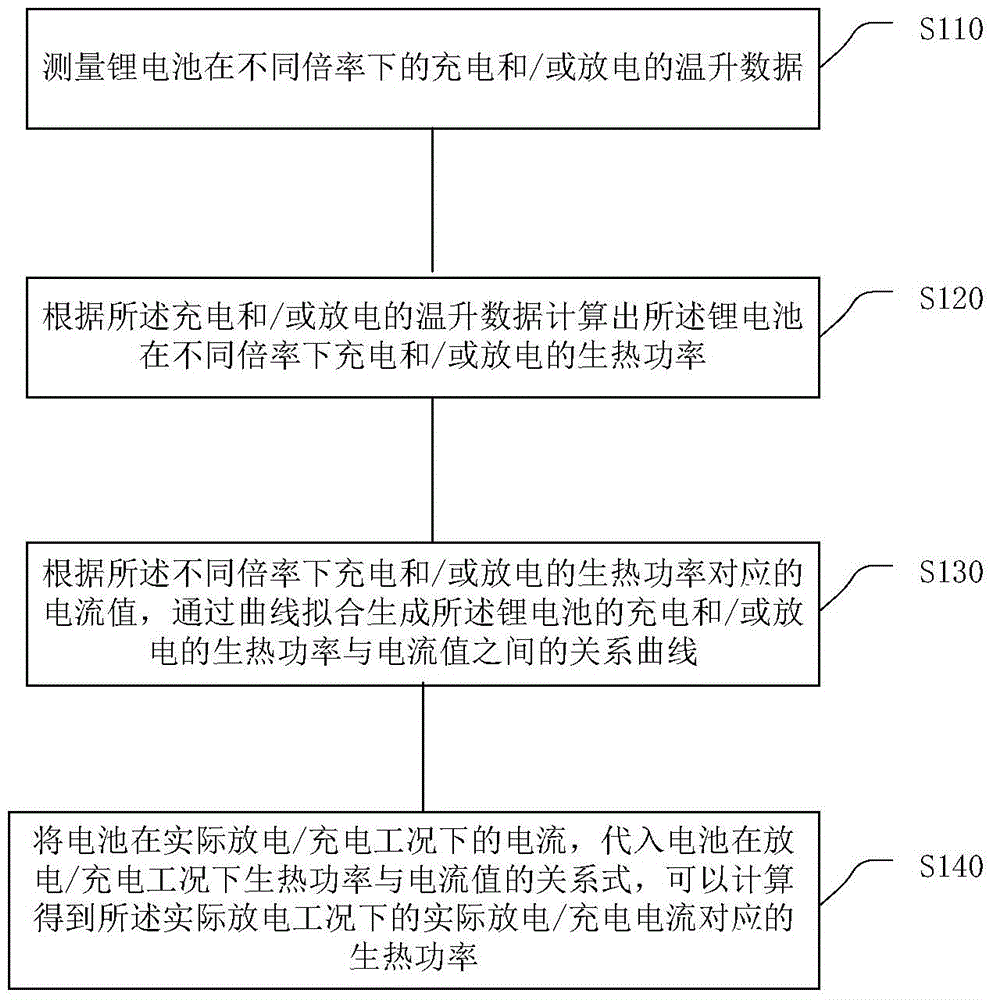

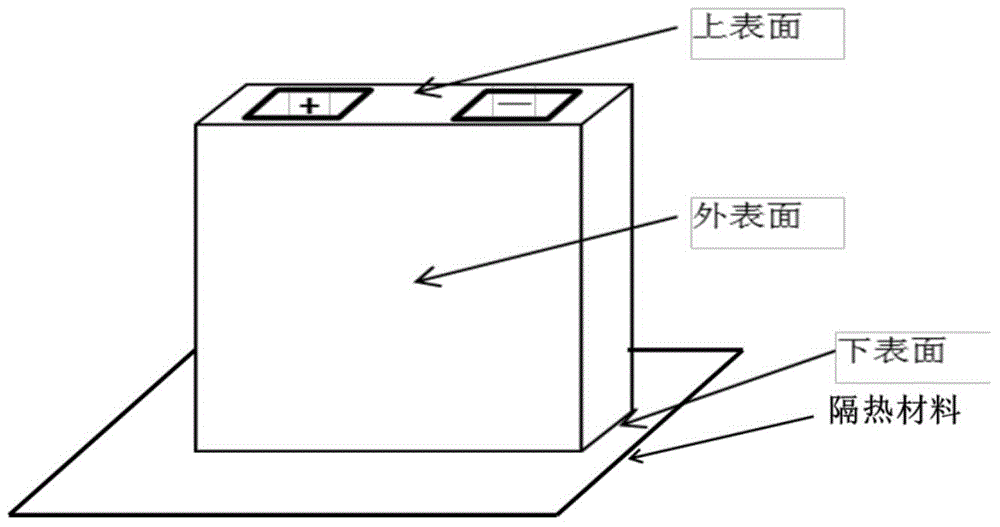

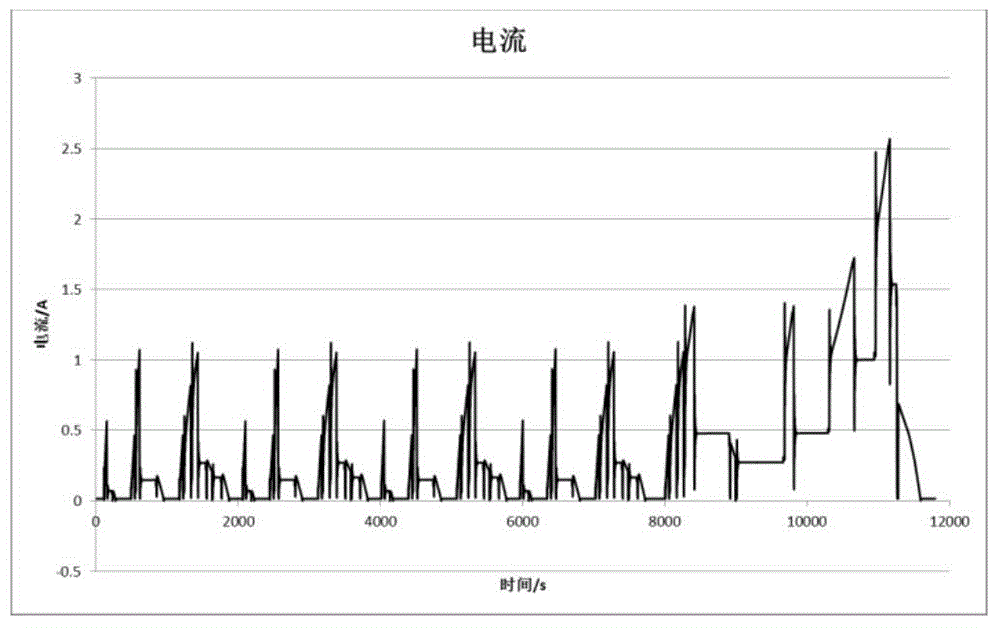

Method and device for measuring heat generation power of batteries in condition of variable current

ActiveCN104569836ASimple test equipmentEasy to implementElectrical testingSpecial data processing applicationsElectrical batteryCharge and discharge

Embodiments of the invention provide a method and device for measuring heat generation power of batteries in condition of variable current. The method comprises the following steps: measuring charging and / or discharging temperature rise data of a battery at different rates, and calculating charging and / or discharging heat generation powers of the battery at different rate according to the charging and / or discharging temperature rise data; generating a relation between the charging and / or discharging heat generation powers of the battery and the current values through curve fitting according to the current values corresponding to the charging and / or discharging heat generation powers at different rates. According to the embodiment of the invention, the relation among the heat generation powers as well as the current and time in condition of variable working current of the battery can be obtained by simply testing the temperature rise data of the battery at a fixed rate and then performing theoretical calculation according to the test result; the test equipment is simple, convenient to implement, and low in cost; a solution for effectively measuring the heat generation power of the battery in the process of charging and discharging in condition of variable current is provided.

Owner:BEIJING ELECTRIC VEHICLE

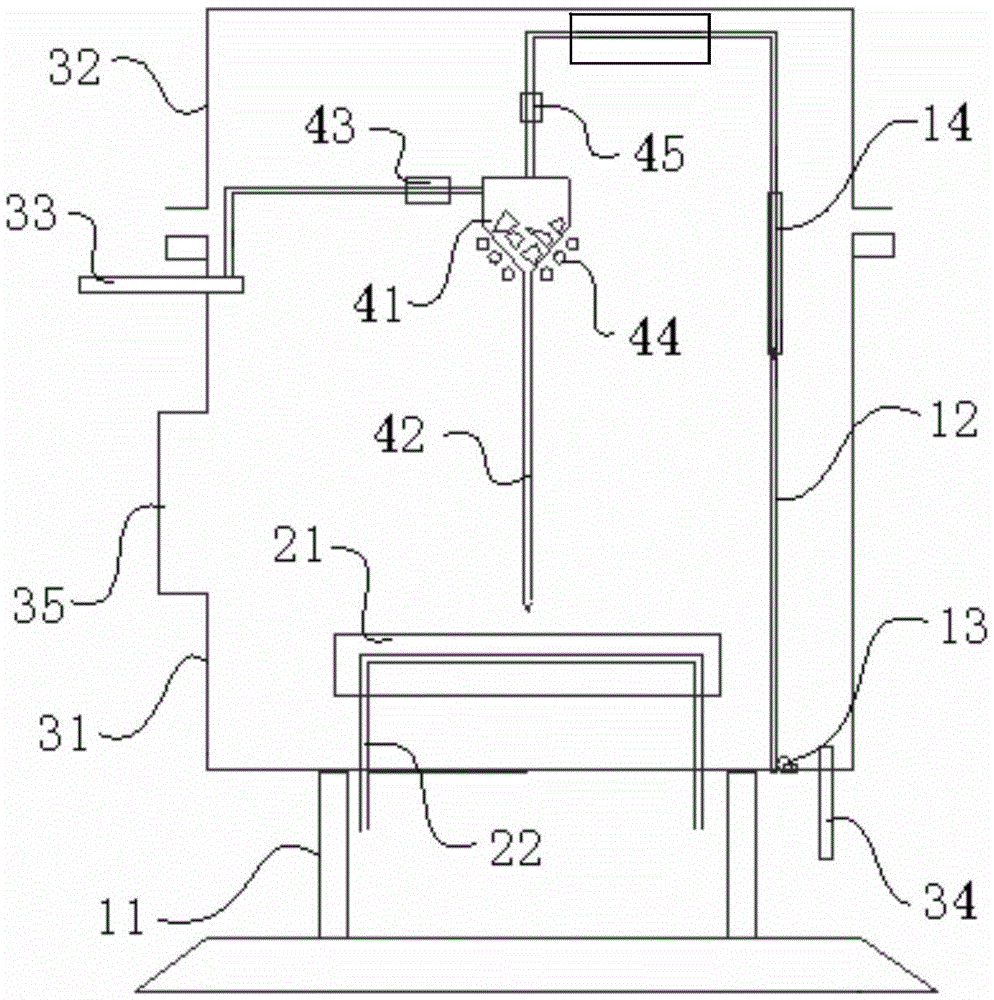

Metal 3D (three-dimensional) printing device and metal 3D printing method

ActiveCN105537591ASimple test equipmentEasy to operateAdditive manufacturing apparatusElectricityControl system

The invention discloses a metal 3D (three-dimensional) printing device and a metal 3D printing method. The printing device comprises a rack system, a heating printing system, a cooling shaping system and an atmosphere control system; the rack system comprises a working table and a spatial three-axis moving component, wherein the working table is used for supporting the other three systems, and the spatial three-axis moving component is used for driving the heating printing system; the heating printing system comprises an electrical heating fire-resistant container; the bottom part of the fire-resistant container communicates with a vertical quartz tube; a dropping liquid hole of which the diameter is less than 0.1 mm is formed in the bottom end of the quartz tube, and an inner cavity of the fire-resistant container communicates with an air pressure component; the cooling shaping system is located below the quartz tube; the heating printing system and the cooling shaping system are arranged in an atmosphere protection chamber of the atmosphere control system. The metal 3D printing device disclosed by the invention is simple in equipment structure and convenient to operate, can be suitable for common metal powder or bulk metals, has high applicability of consumptive materials, can be free of manufacture cost for high-difficulty consumptive materials, and is low in printing cost.

Owner:CENT SOUTH UNIV

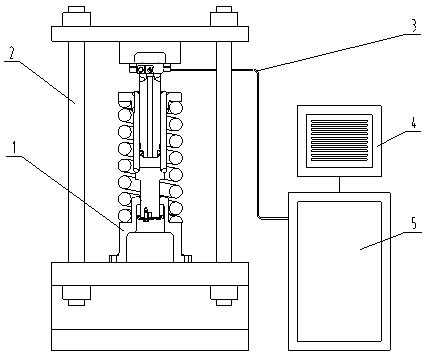

Rapid immersion type metal solidification heat transfer test device and application and application method thereof

InactiveCN106645278ASimple methodSimple test equipmentMaterial heat developmentDirect testGas cylinder

The invention discloses a rapid immersion type metal solidification heat transfer test device and an application method of the device. The test device comprises a mechanical system, a data acquisition system and an atmosphere control system; the mechanical system comprises an induction furnace heated electrically, and an immersion type copper mould controlled by a motor; the data acquisition system comprises a thermocouple located in the copper mould and an external data acquisition card and computer; the atmosphere control system comprises a protective gas hood for accommodating the induction furnace and the copper mould, gas inlet and outlet pipes and a gas cylinder; the mechanical system and key parts of the data acquisition system are both arranged in an atmosphere protection room of the atmosphere control system. The test equipment disclosed by the invention is simple and easy in method, high in accuracy and wide in application range and can be used for carrying out heat transfer testing during a metal rapid solidification process in a laboratory scale, thereby replacing direct testing in industrial production, not affecting the normal production, and further being small in consumption and low in test cost.

Owner:CENT SOUTH UNIV

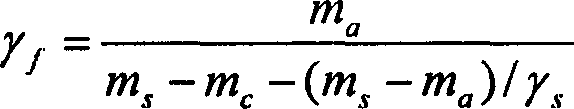

Method for measuring density of mixture of compacted asphaltum

InactiveCN1540311AFast curingReduce difficultySpecific gravity measurementEngineeringSilicone rubber

First, mass of dried test piece in air is weighed. Then, sealed test piece is prepared by using liquid silicone rubber as sealing medium to seal dried test piece. Weighing masses of sealed test piece in air and in water obtains density of test piece. Steps of sealing procedure are as: mixing round bicomponent of liquid silicone rubber evenly; coating liquid silicone rubber on surface of dried test piece evenly to seal surface of the test piece; after liquid silicone rubber being solidified at normal temperature, sealed test piece by silicone rubber is obtained. Features of the invention are: good sealability, and accurate testing result.

Owner:SOUTH CHINA UNIV OF TECH

Method for determining porosity of polymer porous plate-type membrane material

InactiveCN102809531AAvoid influenceImprove accuracyPermeability/surface area analysisPorosityChemical physics

The invention discloses a method for determining porosity of a polymer porous plate-type membrane material. The method comprises the following steps: adding the polymer porous plate-type membrane material to be tested in a plate-type membrane soaking component, enabling water to pass through the membrane material to be tested for 5-60min at the pressure of 0.01-0.5MPa, filling the membrane pores with water fully, taking the membrane material to be tested out of the component, suspending the membrane material to be tested on a hook of a density balance and soaking the membrane material in water, obtaining the mass Wa of the membrane material to be tested by measurement, then taking the membrane material to be tested out of the water, wiping the surface of the membrane to dry by cloth full of water, obtaining the mass Wb of the membrane material in air by measurement, later drying the membrane material to be tested to constant weight in air, obtaining the mass Wc of the membrane material in air by measurement, and finally carrying out calculation according to a formula: epsilon=(Wb-Wc) / (Wb-Wa), thus obtaining the porosity of the membrane material. By the method for determining the porosity of the polymer porous plate-type membrane material, the influence of a high-temperature boiling process in the traditional soaking method on the pore structure of a polymer is avoided and the method has the characteristics of simple technology and correct determination result.

Owner:TIANJIN POLYTECHNIC UNIV

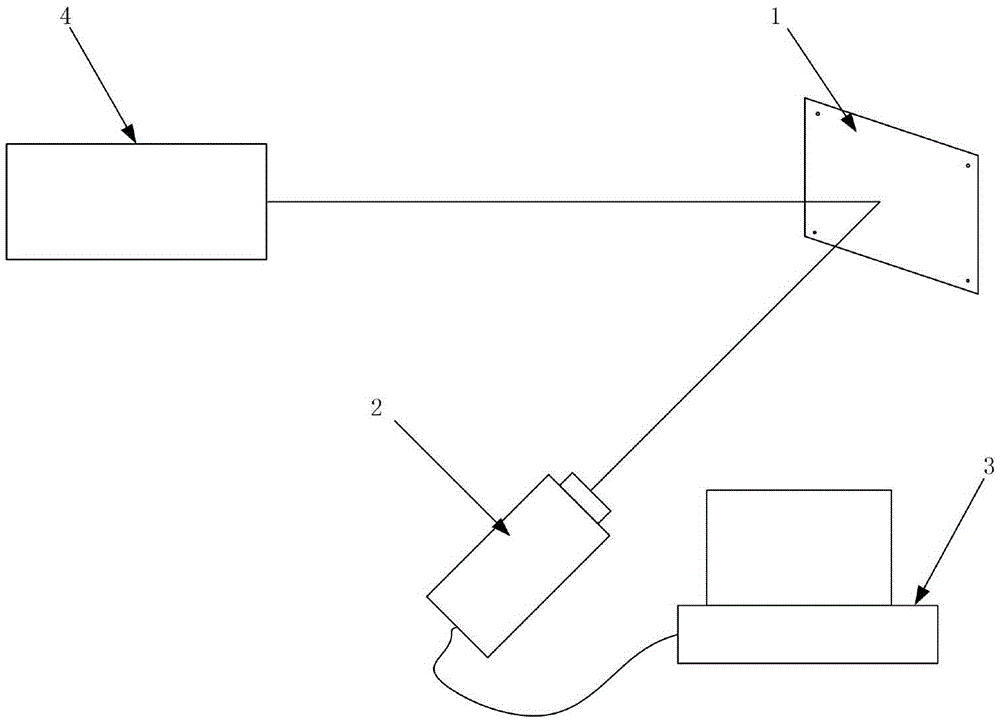

Method for measuring large power CO2 laser divergence angle

ActiveCN105466667AImprove protectionAccurate measurementTesting optical propertiesOptical axisDrift angle

The invention discloses a method for measuring a large power CO2 laser divergence angle, and belongs to the large power CO2 laser technology field. In order to solve the problem of measuring the large power CO2 laser divergence angle accurately in prior art, a large power CO2 laser to be measured is fixed; a diffuse reflection board is arranged vertical to the direction of an optical axis of the laser to be measured to make a laser light spot at the center of the diffuse reflection board; four black bodies are arranged at the four drift angles of the diffuse reflection boards to keep the diffuse reflection board powered on and make the black bodies hot; then, an infrared imaging device is installed in a way that a certain angle is formed between the infrared imaging device and the incidence plane of the diffuse reflection board and the distance is the focal length of the infrared imaging device; finally, the infrared imaging device is connected with a computer; the large power CO2 laser to be measured emits laser continuously; then, the infrared imaging device is closed; the laser emission is stopped, at the same time, the infrared imaging device is started; the image generated after the diffuse reflection board being irradiated by the laser is collected; the image data is transmitted to the computer; and the laser divergence angle of the large power CO2 laser is calculated by the computer.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

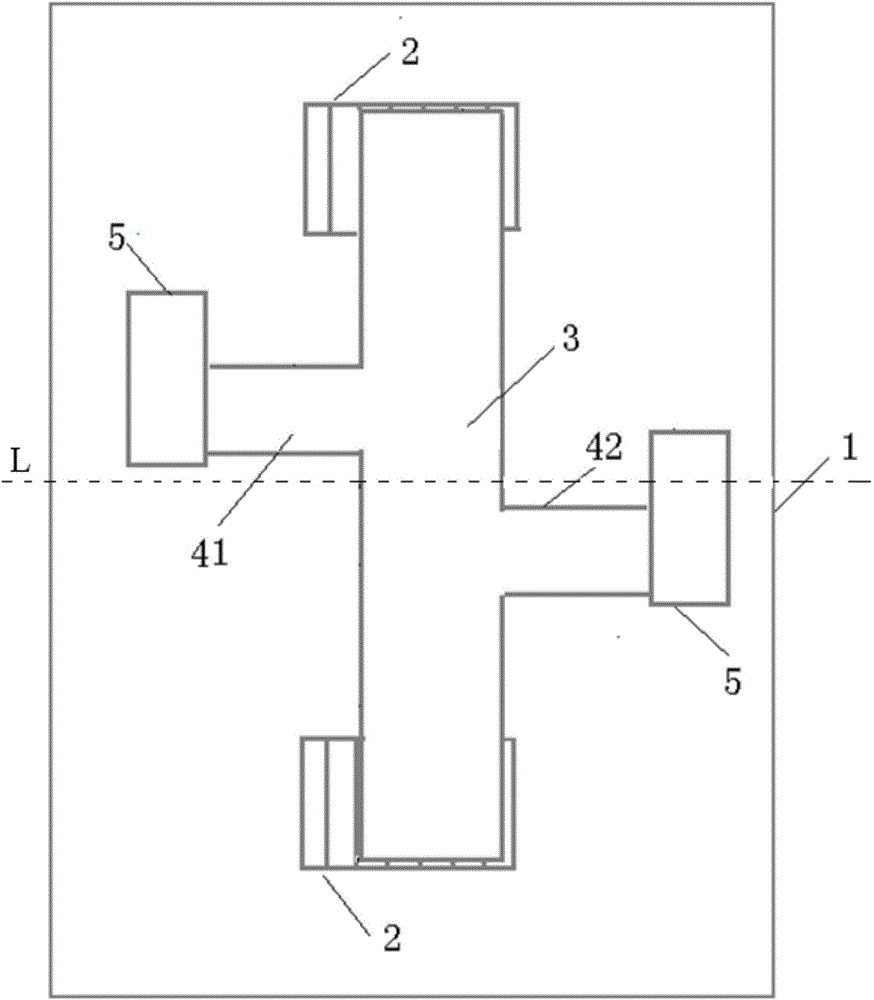

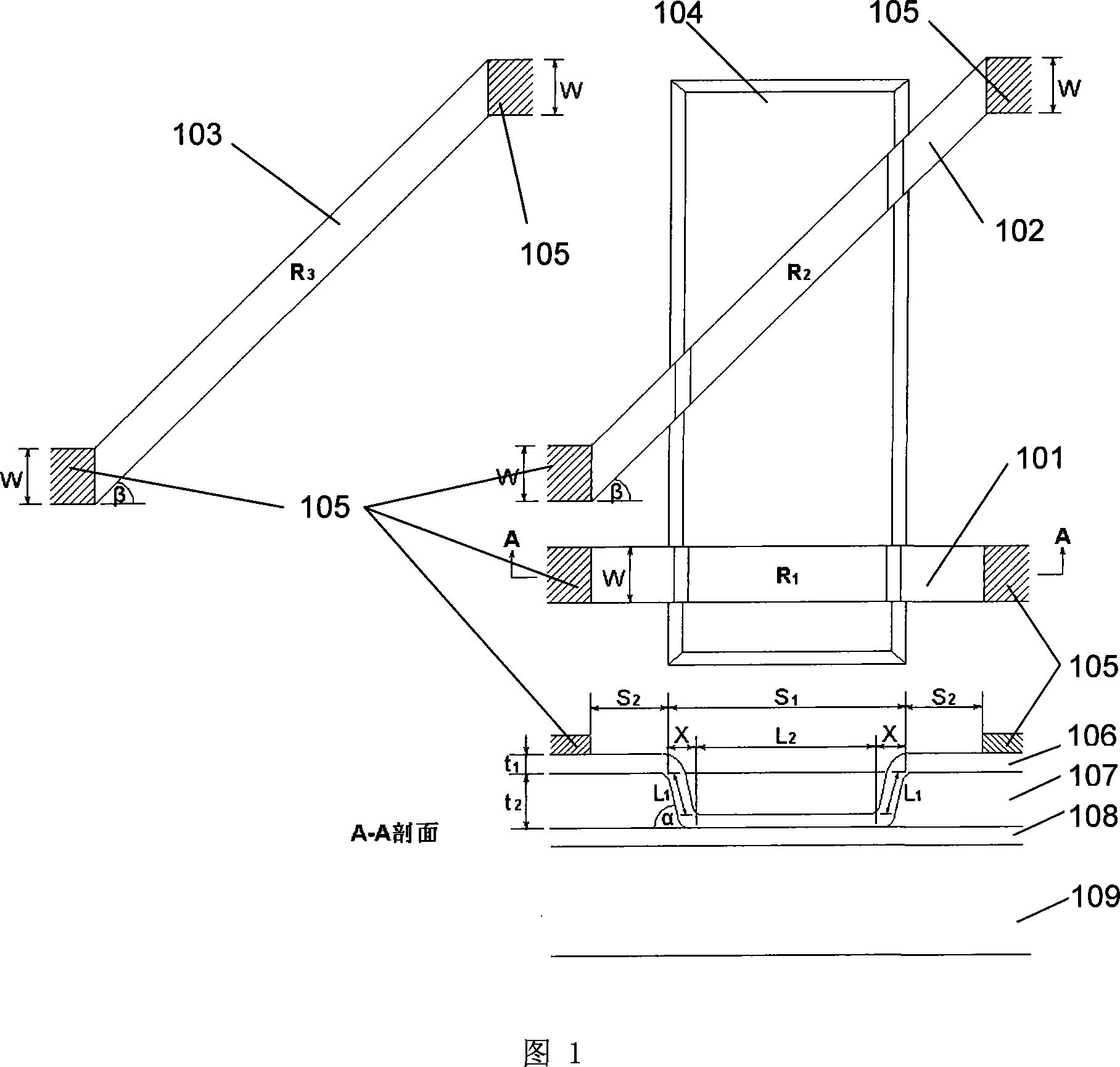

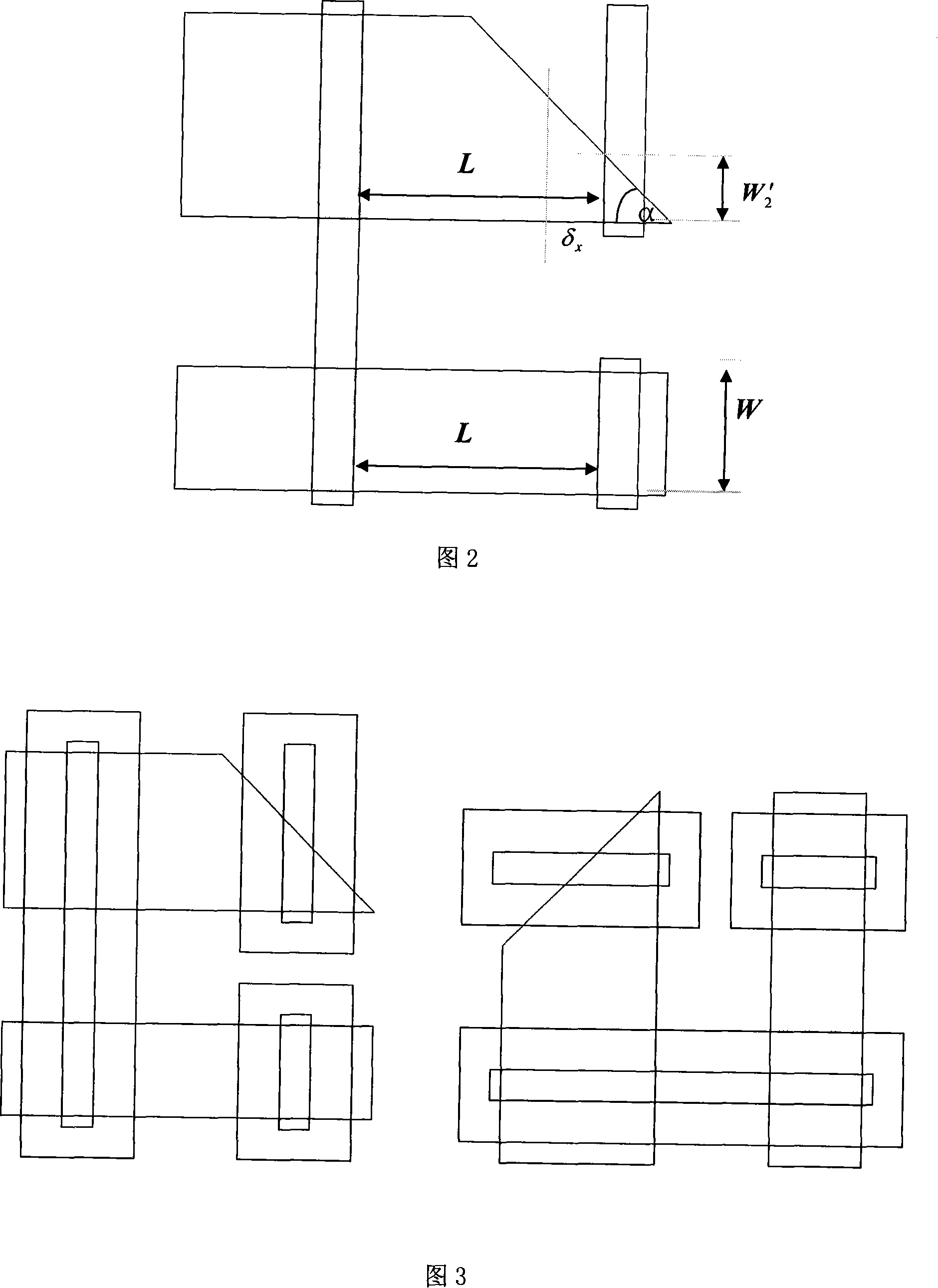

Test structure of micro-machining residual stress of deflection capacitive surface

The invention discloses a test structure of micro-machining residual stress of a deflection capacitive surface. The test structure comprises a substrate, two lower electrode plates, an upper electrode plate, a left beam, a right beam and two anchoring zone. The lower electrode plates are deposited on the upper surface of the substrate, and the two anchoring zones are arranged on the substrate. The upper electrode plate is arranged above the lower electrode plates in a suspended mode, and the left beam and the right beam are identical and located on the two side of the horizontal central axis L of the upper electrode plate respectively, wherein the distance between the left beam and the central axis L is equal to that between the right beam and the central axis L. The right side of the left beam is connected with the left side of the upper electrode plate, and the left side of the left beam is fixed on the side face of one anchoring zone. The left side of the right beam is connected with the right side of the upper electrode plate, and the right side of the right beam is fixed on the side face of the other anchoring zone. The upper electrode plate, the left beam and the right beam are located in the same plane. The test structure is simple and easy to process, and in addition, test equipment is simple and high in precision. The measuring precision can be improved by increasing the area of the upper electrode plate and the area of the lower electrode plates in the test structure, and in addition, with the method for rotating the upper electrode plate in the test structure, a larger capacitance variation can be more easily obtained compared with a horizontally-moving method.

Owner:SOUTHEAST UNIV

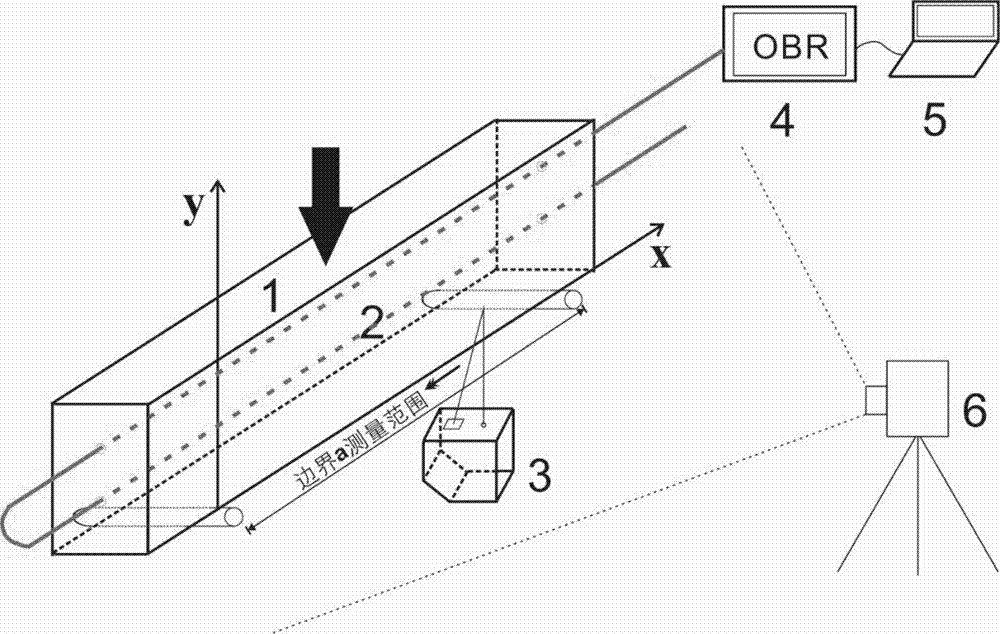

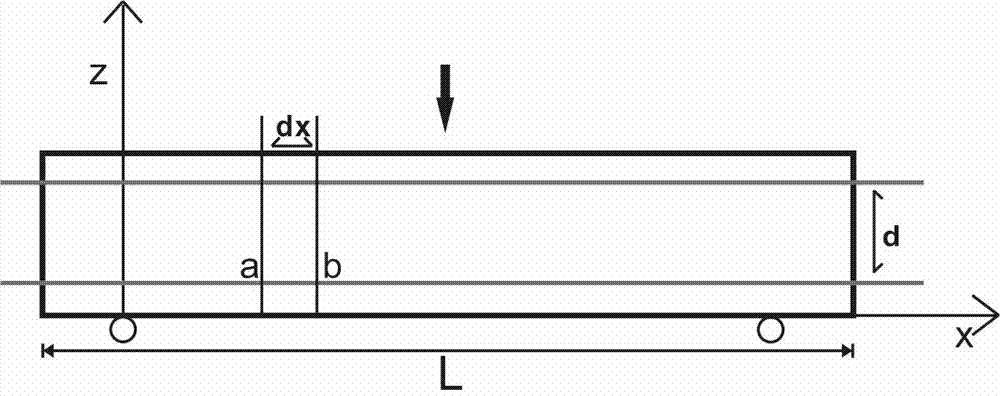

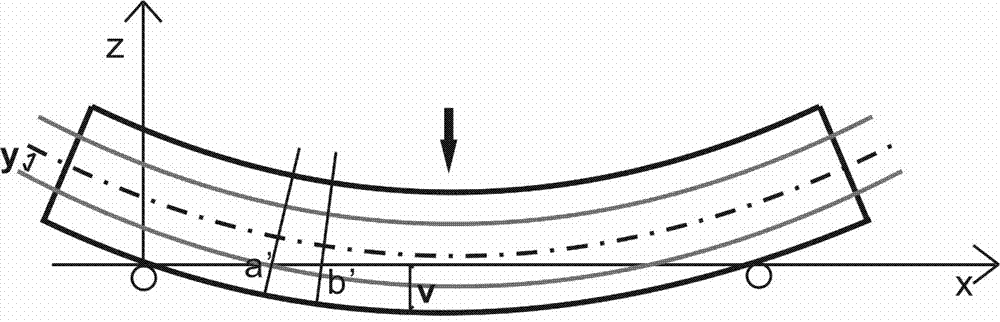

Method for testing sensing optical cable-soil deformation coordination

ActiveCN107063108AHigh precisionThe principle is simpleUsing optical meansOptical apparatus testingStress distributionFiber

The invention discloses a method for testing sensing optical cable-soil deformation coordination. The method includes the following steps that: a test soil strip is prepared, and a sensing optical cable is embedded in the soil strip; the soil strip is made to be bent and deform; the first bending deformation of the soil strip is measured; stress distribution at two sides of the soil strip is measured through a distributed optical fiber sensing technique, and the second bending deformation of the soil strip is calculated; a deformation transfer coefficient t, namely, fiber-soil deformation coordination, is calculated by using a formula described in the descriptions of the invention. According to the method for testing the sensing optical cable-soil deformation coordination of the invention, a new solution is provided for solving a fiber-soil coupling problem; a sound foundation is provided for the improvement of the precision of optical fiber monitoring; and theoretical guidance can be provided for the specific application occasions of the optical fiber monitoring. The principle of the method is simple; required test results can be obtained through a small quantity of test data; and test equipment required by the method is simple and is equipment commonly used laboratories.

Owner:NANJING UNIV

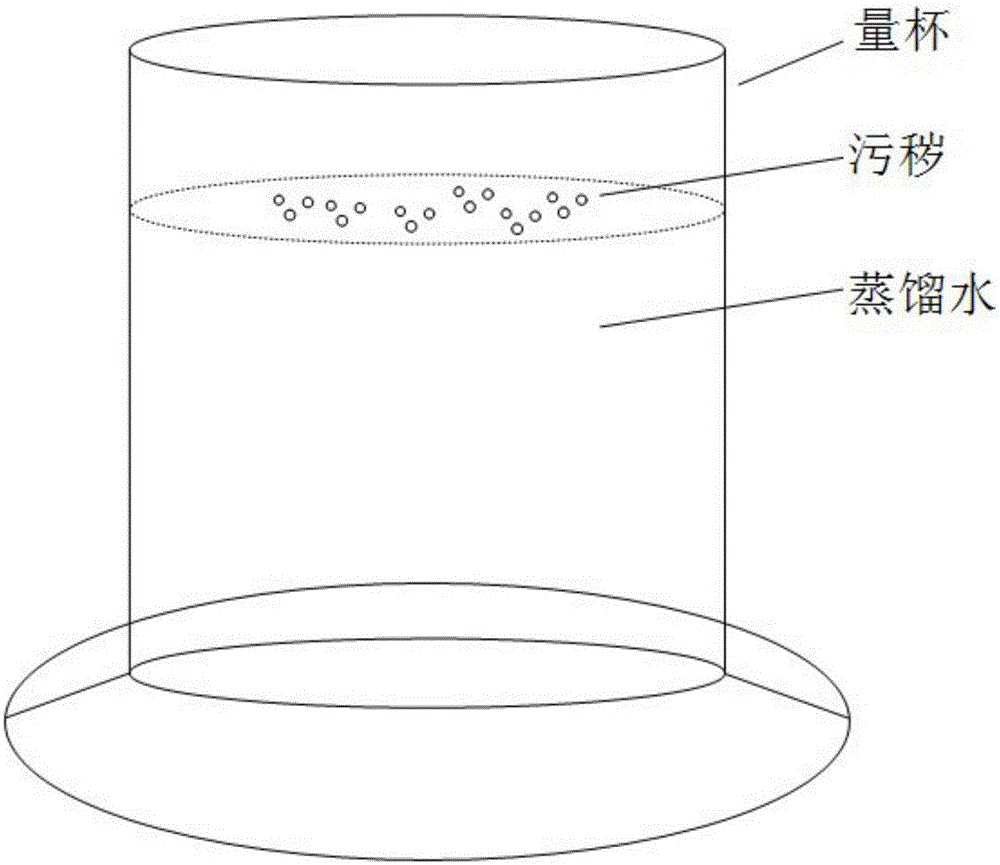

Silicone rubber insulating material hydrophobicityhydrophobicity transfertestingmethod

ActiveCN105067761AReduced workload and security risksSimple test equipmentMaterial analysisWorkloadTimer

The invention relates to a silicone rubber insulating material hydrophobicity transfer testing method, and the technology of the methodis characterized in that: obtaining dirt capable of accurately representing surface state of an insulator in the field; carrying out a pretreatment for insulator surface dirt obtained on the spot ofa laboratory, removing comparatively large particles in the dirty, andtaking dirt of a specific weight; pouring a certain amount of distilled water into a measuring cup and uniformly spreading the dirt of the specific weight on the surface of water in the measuring cup and timing, and recording a dirt wetting time till all the dirt is wetted by distilled water and sinks to the bottom of the measuring cup; determining a hydrophobicity transfer grade of theinsulator surface according to the wetting time of dirt. The invention has a reasonable design,insulators during operation are not needed to be pickeddown, thereby reducing workload and safety risk during test. The test equipment in use is simple, only a timer, an electronic weighing device, a measuring cup and distilled water are needed. Compared with atraditional test method (water spray grading method), the test result has a good consistency and is credible.

Owner:国网(天津)综合能源服务有限公司 +2

Measuring device and measuring method for axial-distribution data of section of rusted steel bar

ActiveCN104198316AImprove detection efficiencyImprove detection accuracyMaterial weighingEngineeringAxial distribution

The invention discloses a measuring device and a measuring method for axial-distribution data of a rusted steel bar. The measuring device comprises a weighing instrument, a clamp, a container for containing liquid and a steel bar lifting device, wherein the steel bar lifting device comprises a speed reducing mechanism, a winding drum, a steel wire, an indexing mechanism and the clamp; the winding drum is arranged on an output shaft of the speed reducing mechanism; the steel wire is wound on the winding drum; the lower end of the steel wire is connected with the clamp; and the indexing mechanism is arranged on an input shaft of the speed reducing mechanism. The container is arranged on the weighing instrument, the upper end of the measured steel bar is clamped by the clamp, the steel bar droops vertically, the lower end of the steel bar is inserted into the liquid in the container, and the measured section of the steel bar is positioned above liquid level in the container; when the indexing mechanism rotates by unit scale, the steel bar falls by a displacement interval value, and the corresponding weighing value corresponding to the displacement interval value is obtained from the weighing instrument. The measuring device disclosed by the invention has the advantages that the testing equipment is simple, the detection efficiency is high and the detection accuracy is high.

Owner:SHENZHEN UNIV

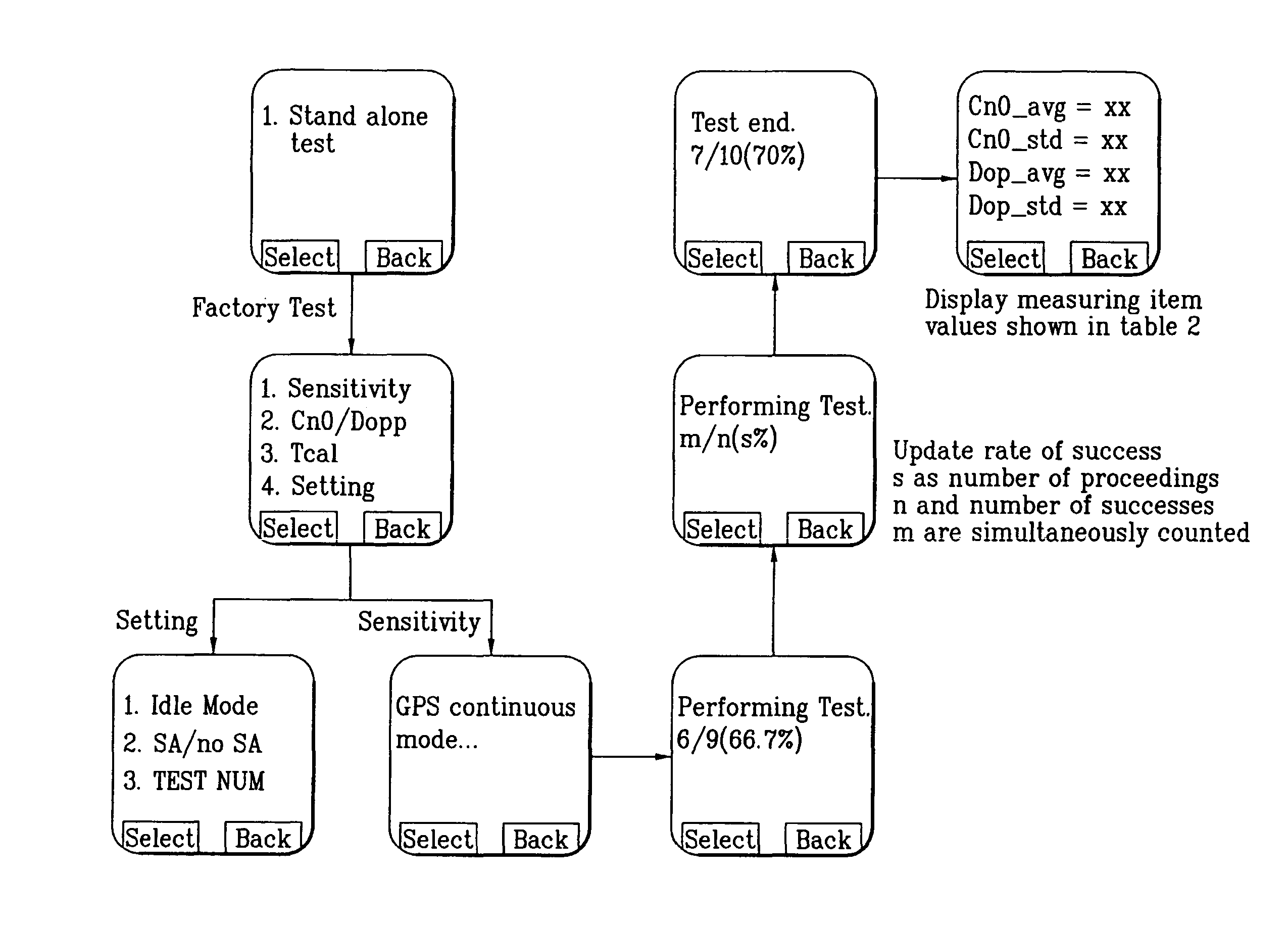

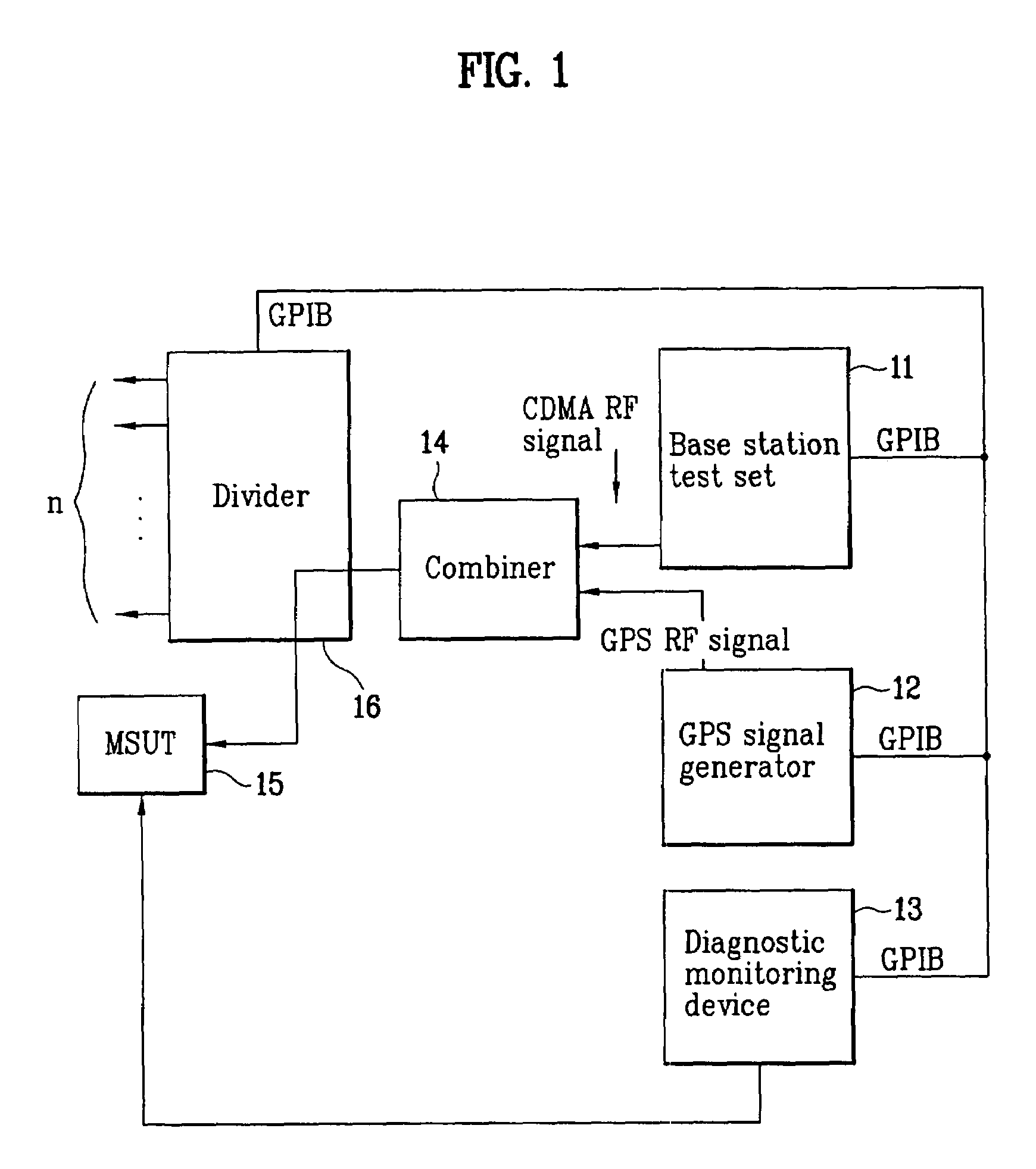

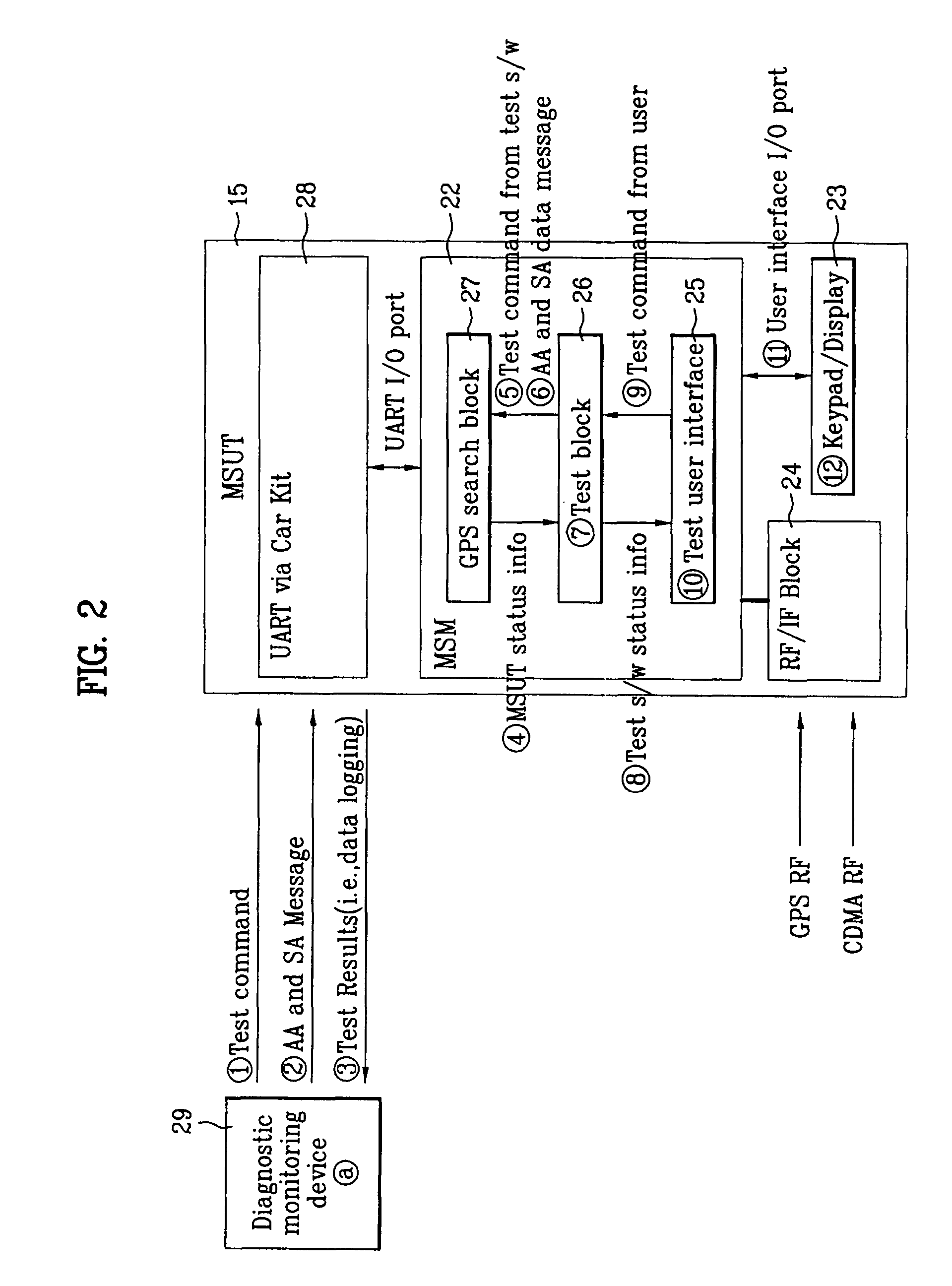

Apparatus and method for testing performance of mobile station having GPS function

InactiveUS7136746B2Simplify test equipmentReduce test timeVehicle testingInstruments for road network navigationReal-time computingUser interface

An apparatus for testing a performance of a mobile station having a global positioning system (GPS) function including a test block having test commands and a test user interface for testing the performance of the mobile station. The test block and test interface are including within the mobile station. Further, the apparatus tests the performance of the mobile station by operating the test block driven through the test user interface.

Owner:LG ELECTRONICS INC

Method for breeding transgenic tetraena mongolica callus and special culture medium thereof

InactiveCN101974479ASimple and fast operationImprove conversion rateVector-based foreign material introductionPlant cellsTetraena mongolicaSkin callus

The invention discloses a method for breeding transgenic tetraena mongolica callus and a special culture medium thereof. The method comprises the following steps: (1) transplanting a tetraena mongolica stem into the tetraena mongolica callus induction culture medium, and culturing to obtain the callus; (2) and transforming the callus obtained in step (1) by using Agrobacterium rhizogenes containing target gene to obtain the transgenic tetraena mongolica callus. In the method, tetraena mongolica seeds from Wuhai in Inner Mongolia are selected as the initial experimental material; after sterileculture to obtain sterile seedlings, the young stem section is cut off to induce the callus; and by using the callus as the explant, and extraneous gene is integrated into the genome of tetraena mongolica by using the Agrobacterium rhizogenes mediated method. By optimizing the processes of transforming and screening callus, the invention establishes a tetraena mongolica callus transformation system which has the advantages of simple operation, high efficiency and high speed.

Owner:INST OF BOTANY CHINESE ACAD OF SCI

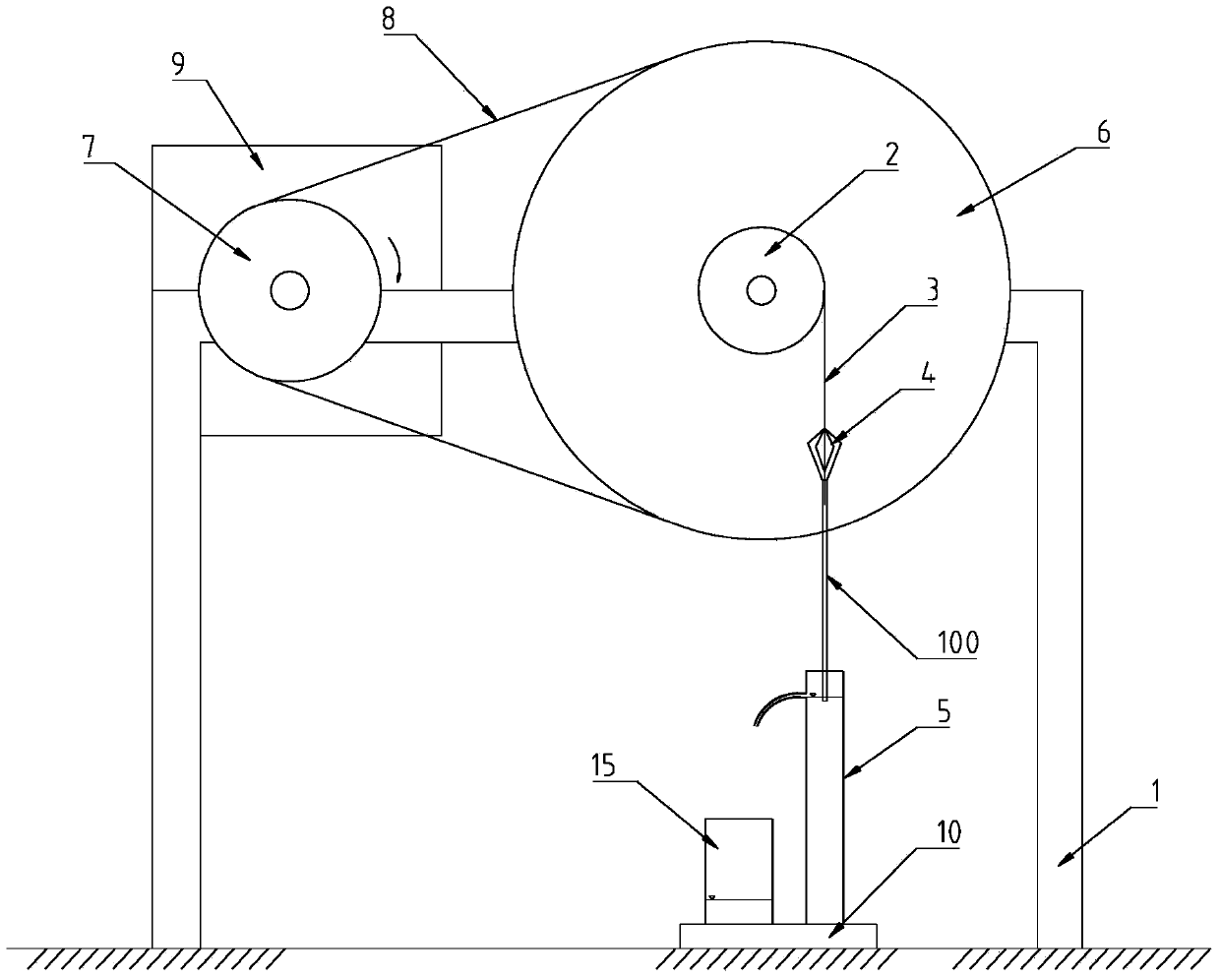

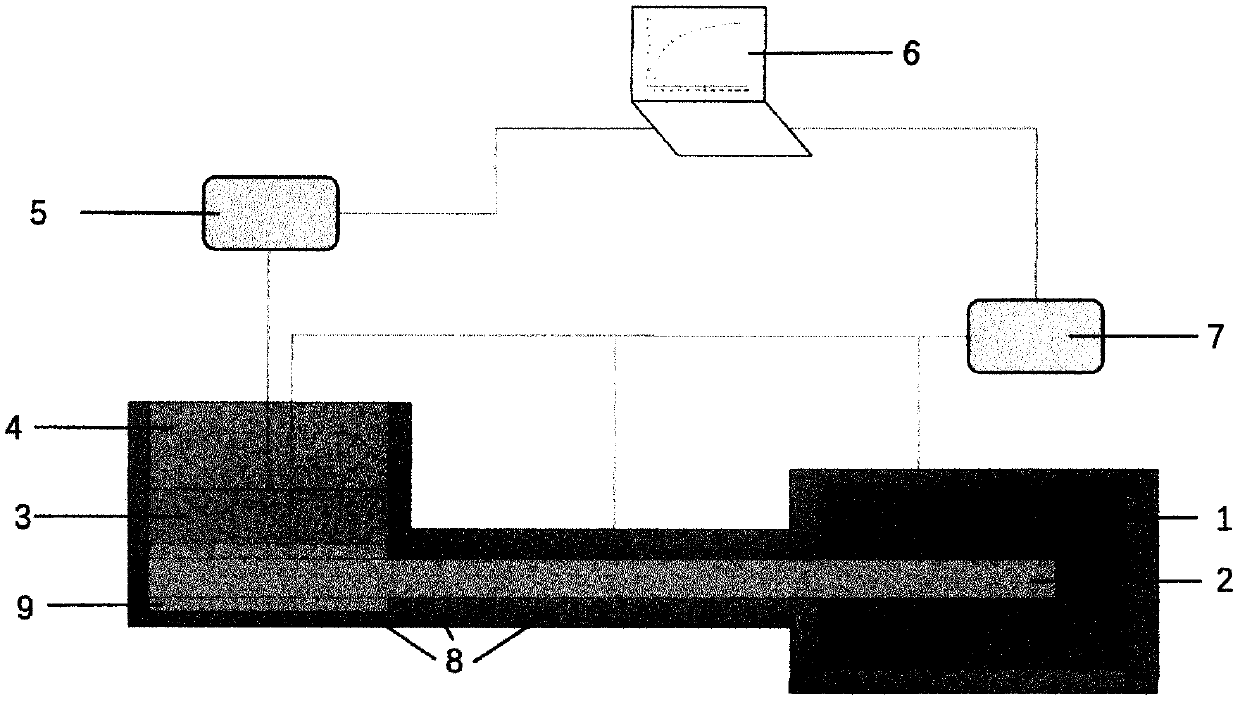

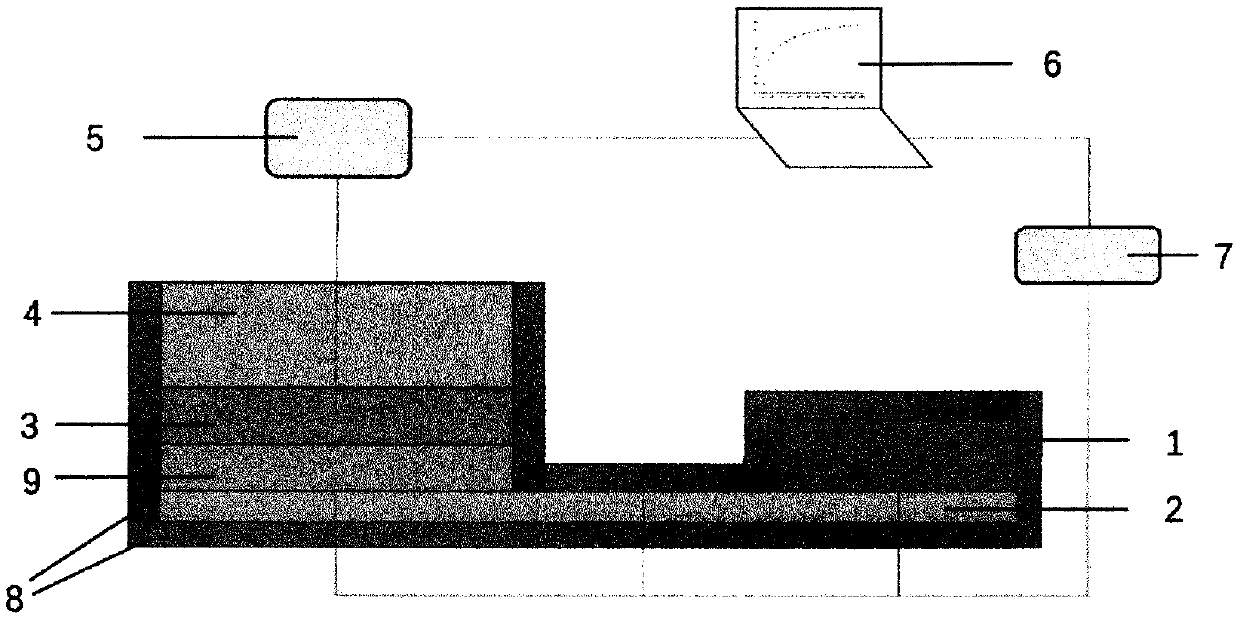

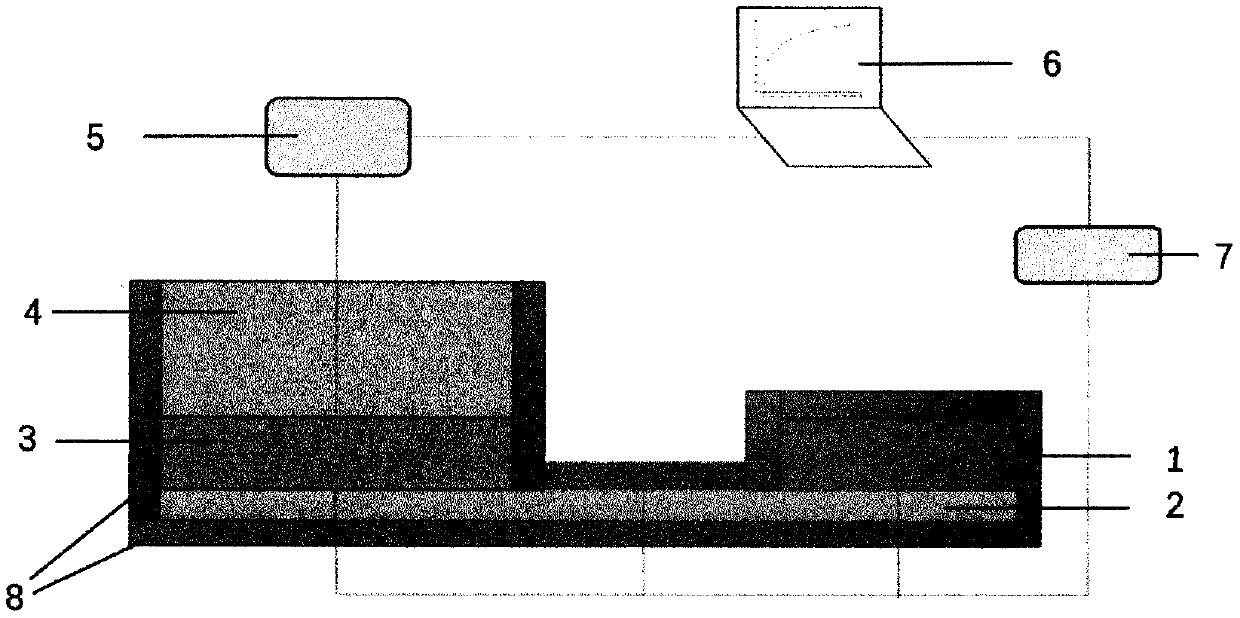

Heat pipe heat transfer performance test device and testing method thereof

InactiveCN111337535ASimple test equipmentEasy to testMaterial heat developmentThermal insulationElectronic computer

The invention relates to a heat pipe heat transfer performance test device and a testing method thereof, which belong to the technical field of heat transfer, and comprise heating equipment (1), a to-be-tested heat pipe (2), a thermoelectric conversion module (3), a cold source system (4), an electrical parameter measuring system (5), an electronic computer (6), a temperature measuring system (7),a thermal insulation material (8) and a transition module (9). During testing, heat is firstly transferred from the heating equipment to the evaporation section of the to-be-tested heat pipe; furthertransferring to a heat insulation section and a condensation section; then the signals are transmitted to the transition module and the thermoelectric conversion module; the real-time conversion condition of the thermoelectric conversion module is measured through the electrical parameter measurement system and the electronic computer, so that the heat transfer capacity can be calculated, the temperature of each temperature measurement point of the heat pipe to be measured is measured in real time through the temperature measurement system, and the heat transfer performance of the heat pipe can be calculated by combining the test data with the size parameters of the heat pipe. The method has the advantages of simple test equipment, convenient test, high test precision and the like.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

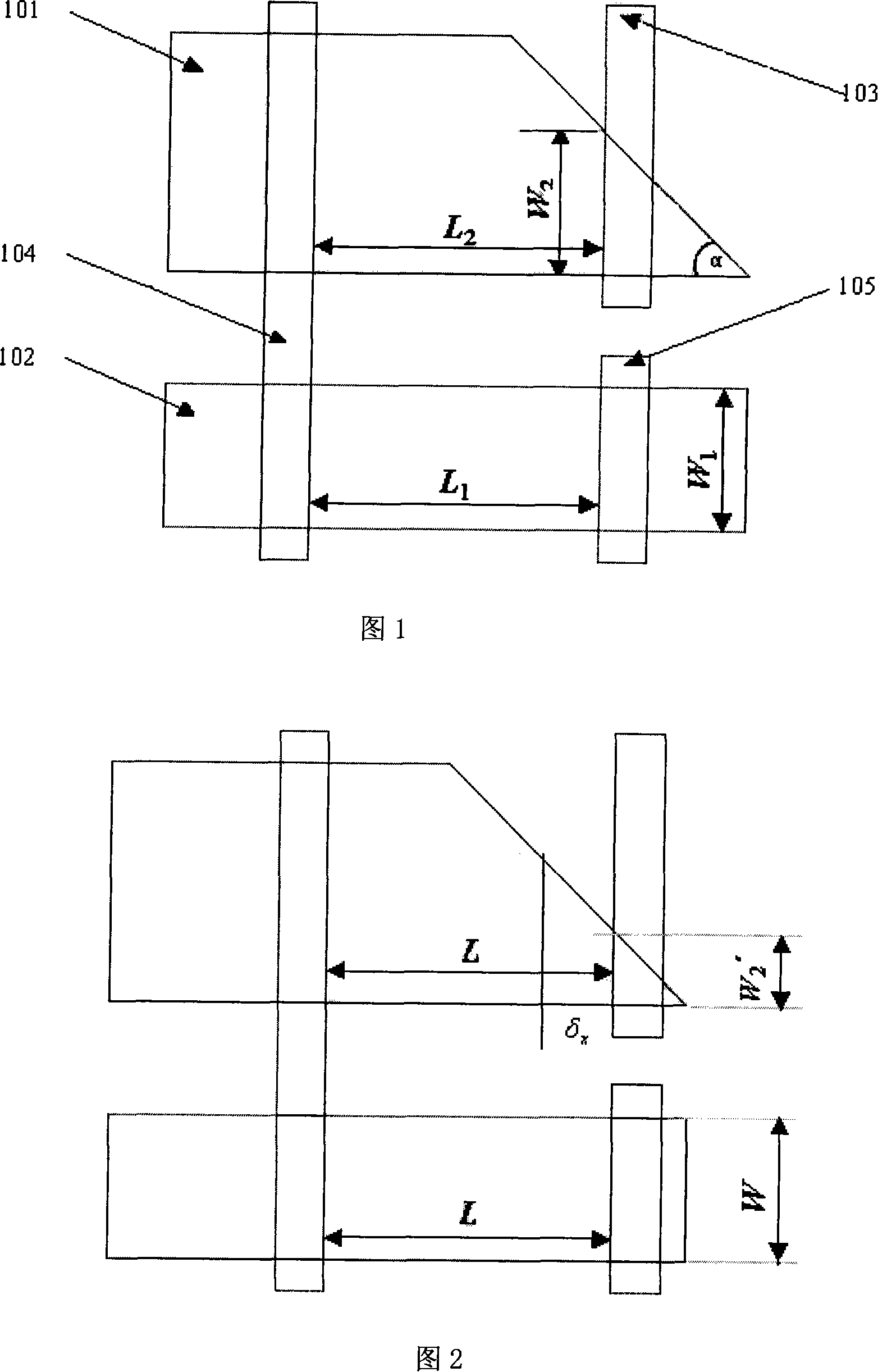

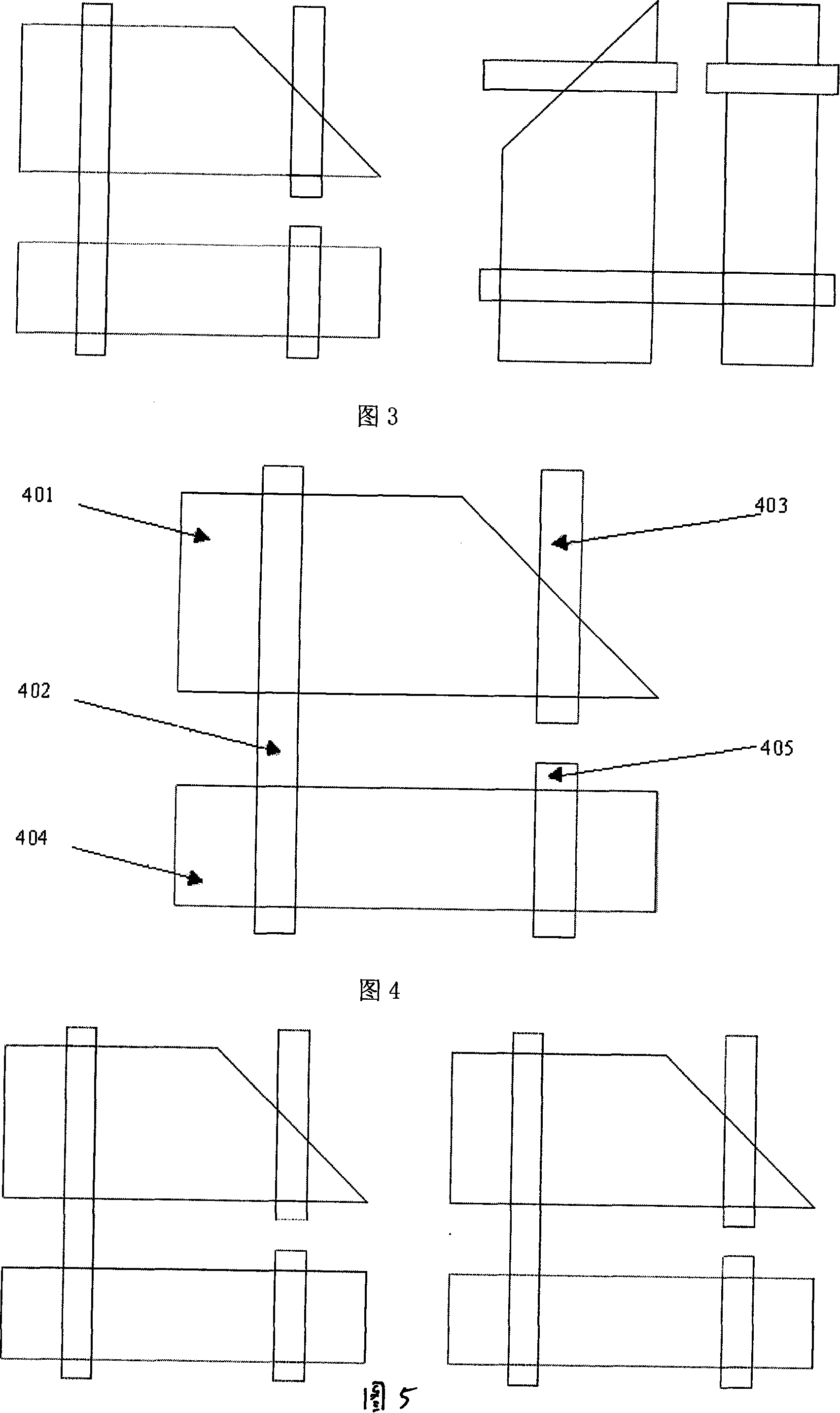

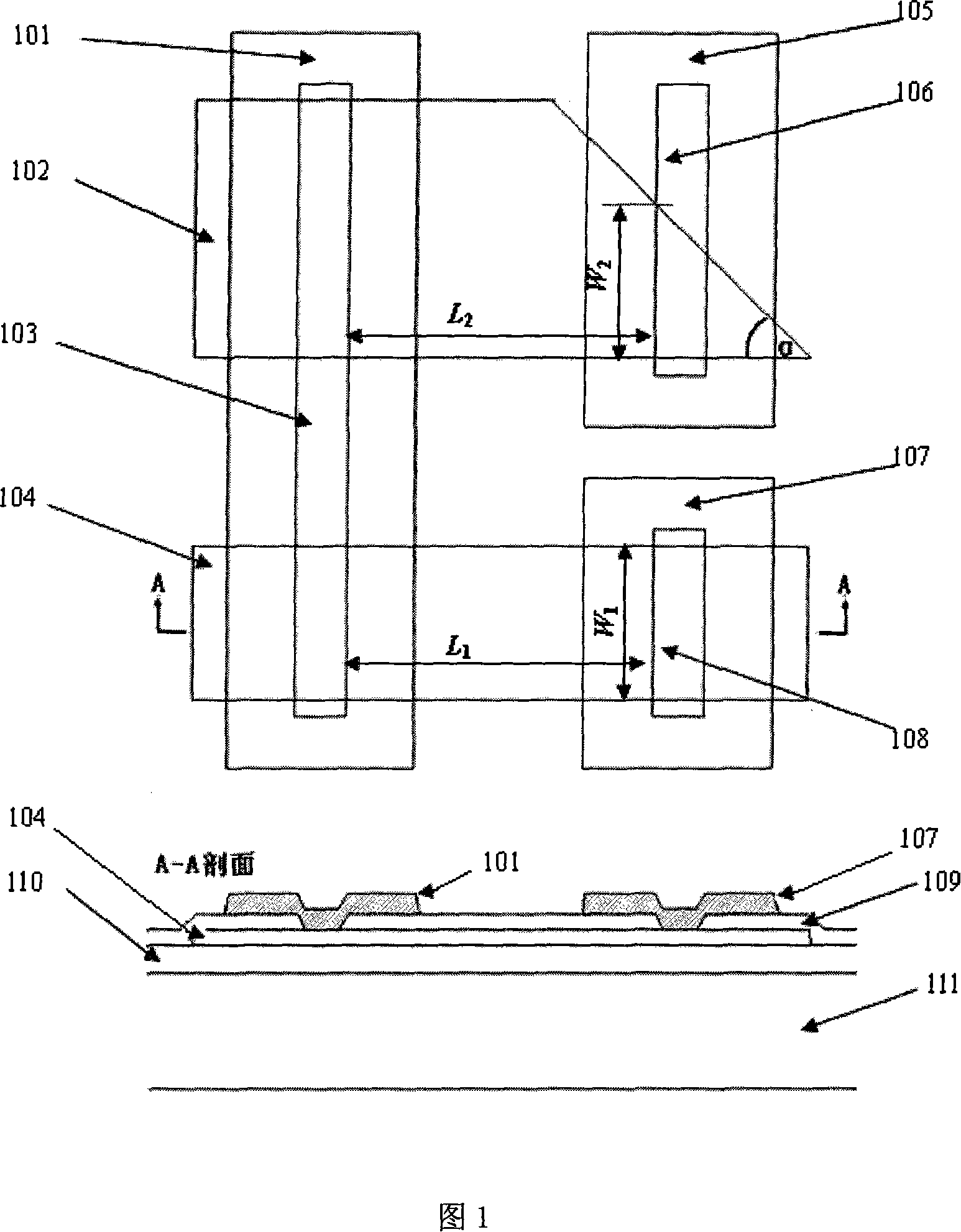

Different conductive layers alignment error electricity testing structure in micromotor system apparatus process

InactiveCN101143704AWith automated extractionNo quantization errorSemi-permeable membranesUsing electrical meansGraphicsElectricity

The invention relates to an electricity test structure for alignment error of different conducting layer graphics in processing of micro-electro-mechanical system components. A metal layer is taken as the base layer to design an alignment error test structure of all conducting layers; in the structure, a semiconductor layer includes two semiconductors which are separated, made in the same material and in different shapes; one of the semiconductors is trapezoidal and the other is rectangular, which are arranged in parallel; the connected metal layer formed includes two paralleled metal bars with spacing, one of which is vertically covered on an upper and a lower bottom sides of the trapezoidal window as well as two long sides of the rectangular window, and the other is covered on the obtuse angle part of the trapezoidal window and two long sides of the rectangular window, and cut off in the separation area between the two semiconductors; the two metal bars and the semiconductors between the metal bars form a resistance with connecting wires; when relative deflection exists between the metal layer graphics and the insulation layer graphics, the testing resistance changes, and the alignment error of the metal layer relative to the semiconductor material graphics can be obtained.

Owner:SOUTHEAST UNIV

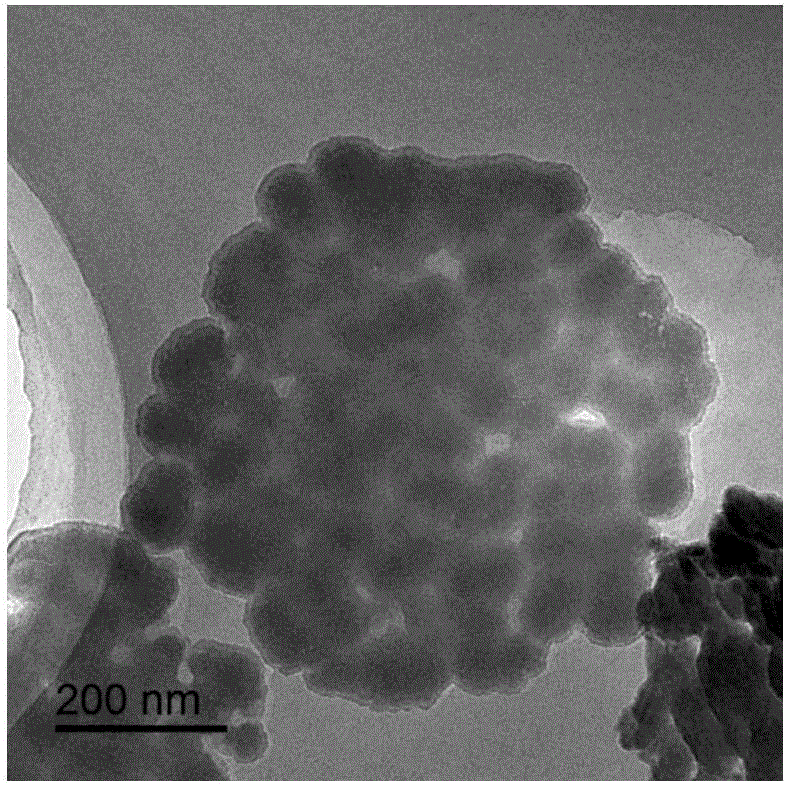

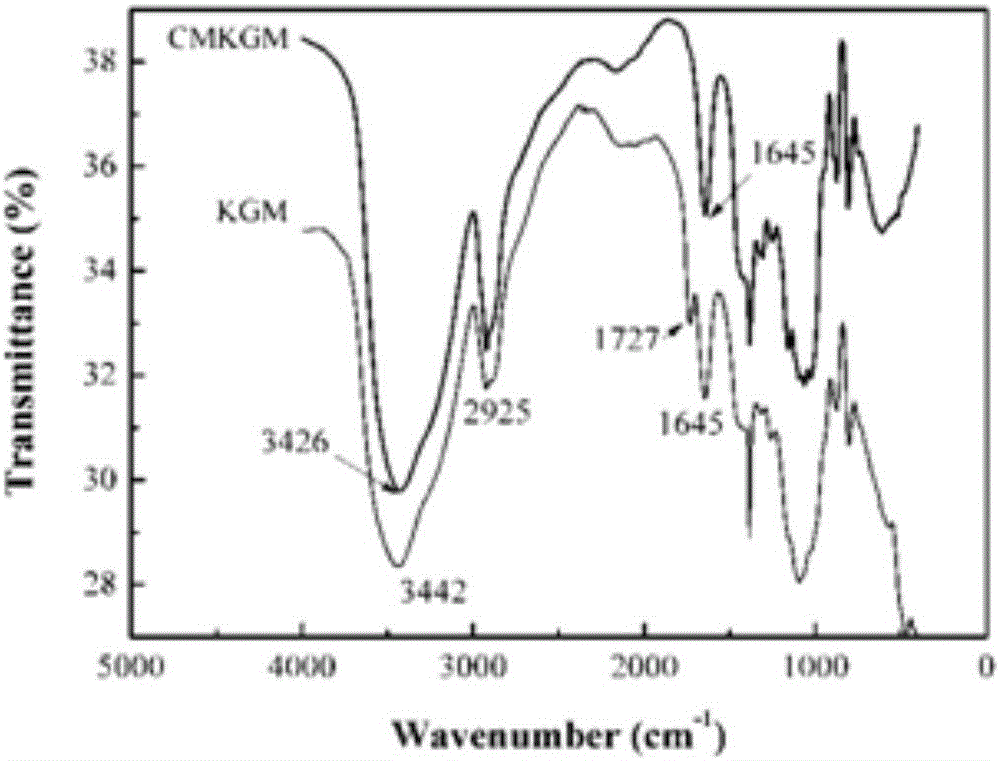

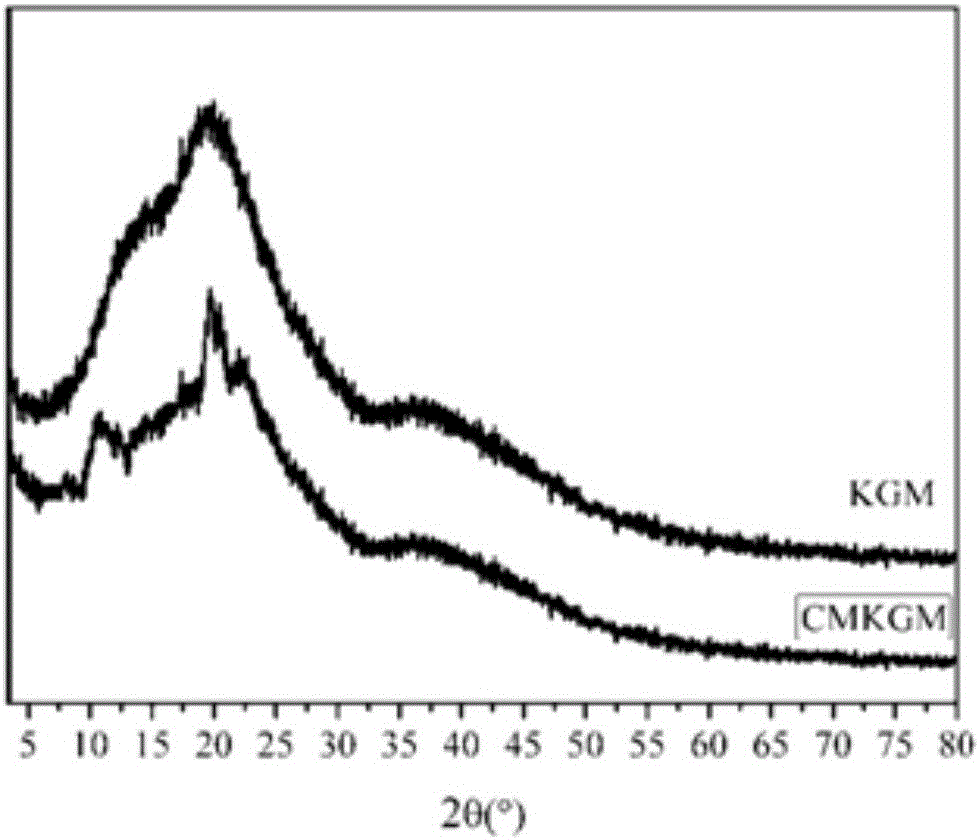

Preparation method of konjac glucomannan gel microspheres

ActiveCN106215819AMaintain active stabilityMaintain biological stabilityMicroballoon preparationMicrocapsule preparationMicrosphereOil phase

The invention discloses a preparation method of konjac glucomannan gel microspheres. The preparation method includes: (1), adding konjac glucomannan into a water solution containing certain alcohol, and stirring to obtain a dispersion; (2), adding the dispersion into an oil phase, adding an emulsifier and alkaline substance, and stirring to obtain an emulsion; (3), adding an acidic solution and glutaraldehyde into the emulsion, and stirring for reaction to obtain gel microspheres; (4), using cyclohexane, alcohol and purified water to wash the gel microspheres to be neutral, and lyophilizing to obtain the konjac glucomannan gel microspheres. By the method, the konjac glucomannan gel microspheres which are uniform in grain size can be prepared and have porous structure. The method can be used for preparing media used for biochemical fine separation and gel microspheres serving as a drug conveying carrier, is expected to be capable of maintaining bioactivity and biostability of drugs and can be used for essence adsorption and controlled-release carriers. Due to small grain size, the konjac glucomannan gel microspheres can be dispersed in media well and are free of settling after being placed for a long time.

Owner:SOUTHWEAT UNIV OF SCI & TECH

Insulation layer thickness electrology test structure in micro electro-me-chanical systems device structure

InactiveCN101158568AWith automated extractionSimple test equipmentSemi-permeable membranesElectrical/magnetic thickness measurementsElectrical resistance and conductanceInsulation layer

The invention provides an electric test structure with the surface processing of the thickness of an insulating layer in MEMS device structure, a basic aim is that the thickness value of the insulating layer is gained by the way of electrical measurement. Of the surface process technology, the insulating layer in the MEMS device structure is usually silica, silicon nitride or polymer. The invention utilizes a conductive poly-silicon on the insulating layer material and a groove arranged on the insulating layer to design the electric test structure, and obtains the thickness of the insulating layer by measuring the resistance of poly-silicon strips with introducing a mathematical model.

Owner:NANTONG SHENGYANG ELECTRIC CO LTD +1

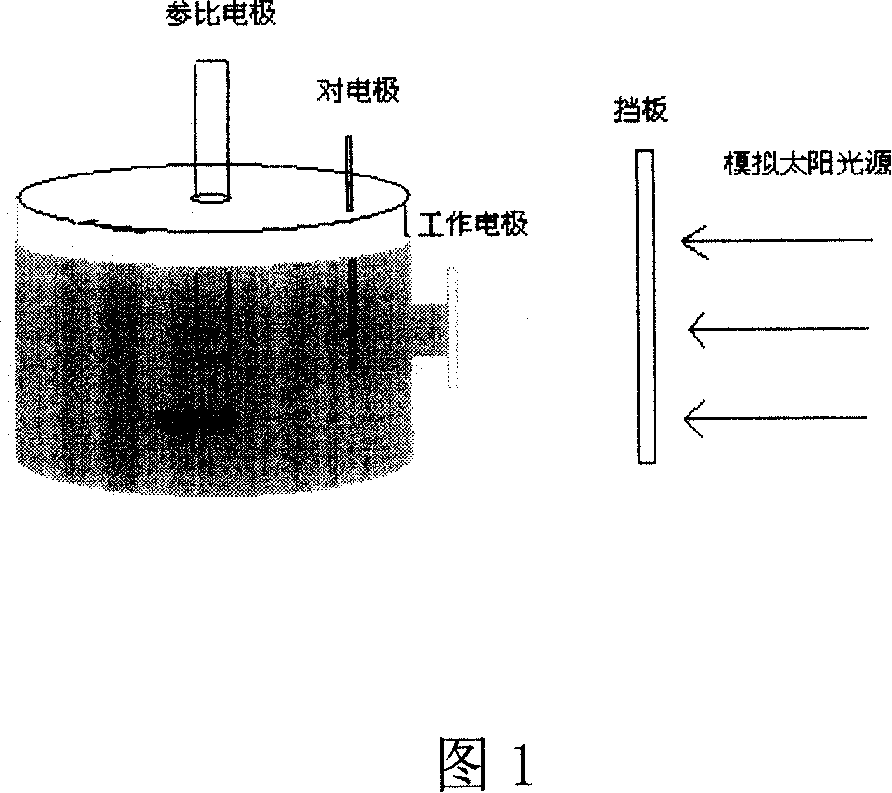

A zinc oxide thin film for solar battery and manufacture method

InactiveCN1964078AHigh light currentShort Photoelectric Response TimeFinal product manufactureVacuum evaporation coatingSputteringZno nanoparticles

The provided simple preparation method for nano ZnO film refers to magnetron sputtering on glass / ITO (In2O3: Sn) or silicon substrate. The product has supper full solar waveband photovoltaic and photoelectric properties. This invention is low cost and fit to production in scale, and has well application future.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

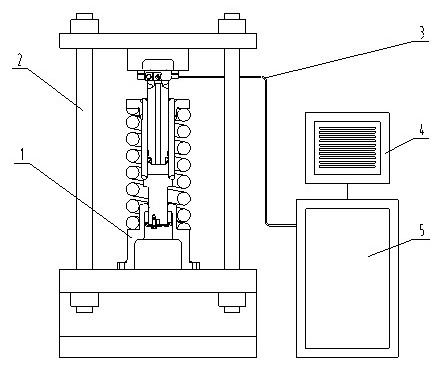

Novel method for testing durability of track tensioning device of hydraulic excavator

InactiveCN102183426ASimple test equipmentDurability TestMaterial strength using repeated/pulsating forcesHydraulic cylinderLine tubing

The invention discloses a novel method for testing the durability of a track tensioning device of a hydraulic excavator. The method comprises the following steps of: calculating a maximum working pressure of an oil cylinder during working according to a maximum load of the track tensioning device of the hydraulic excavator and the diameter of the oil cylinder, taking the maximum working pressure as a maximum hydraulic value provided by a hydraulic pump unit, and connecting the track tensioning device and the hydraulic pump unit with an operating system through an oil supply pipeline; removing grease inside the oil cylinder of the track tensioning device, and realizing periodic compression of a tensioning spring by using periodic reciprocating motions of a piston and the oil cylinder of the track tensioning device; recording a spring compressed frequency before the track tensioning device fails so as to determine the durability of the track tensioning device; and detecting and analyzing a failure mode so as to provide basis for improvement on the durability of the track tensioning device. By using the oil cylinder of the track tensioning device, the reciprocating motion of the tensioning spring is realized, and an auxiliary hydraulic cylinder is avoided; therefore, the whole test equipment is simplified, and the safety protection level is high.

Owner:SANY HEAVY MACHINERY

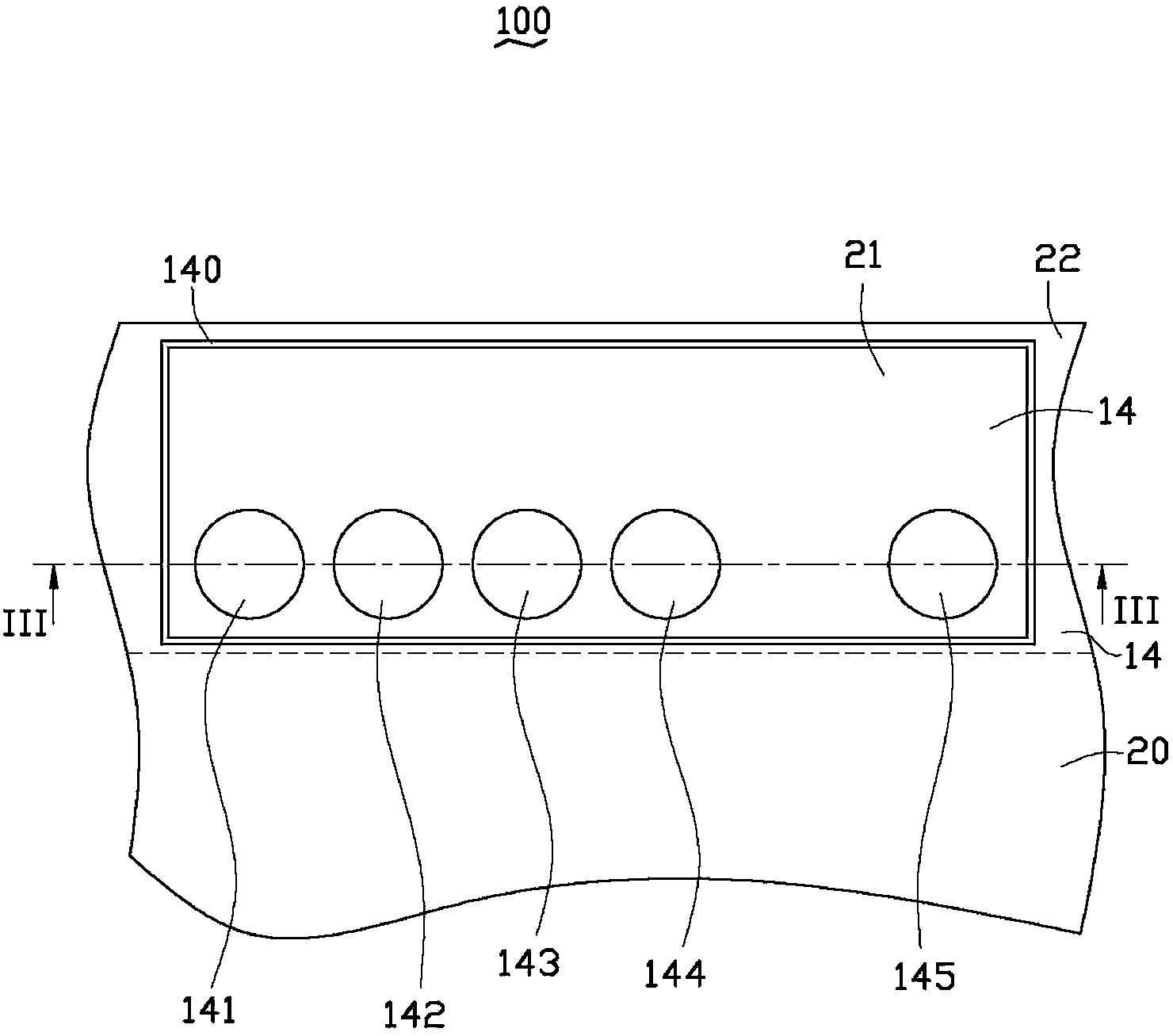

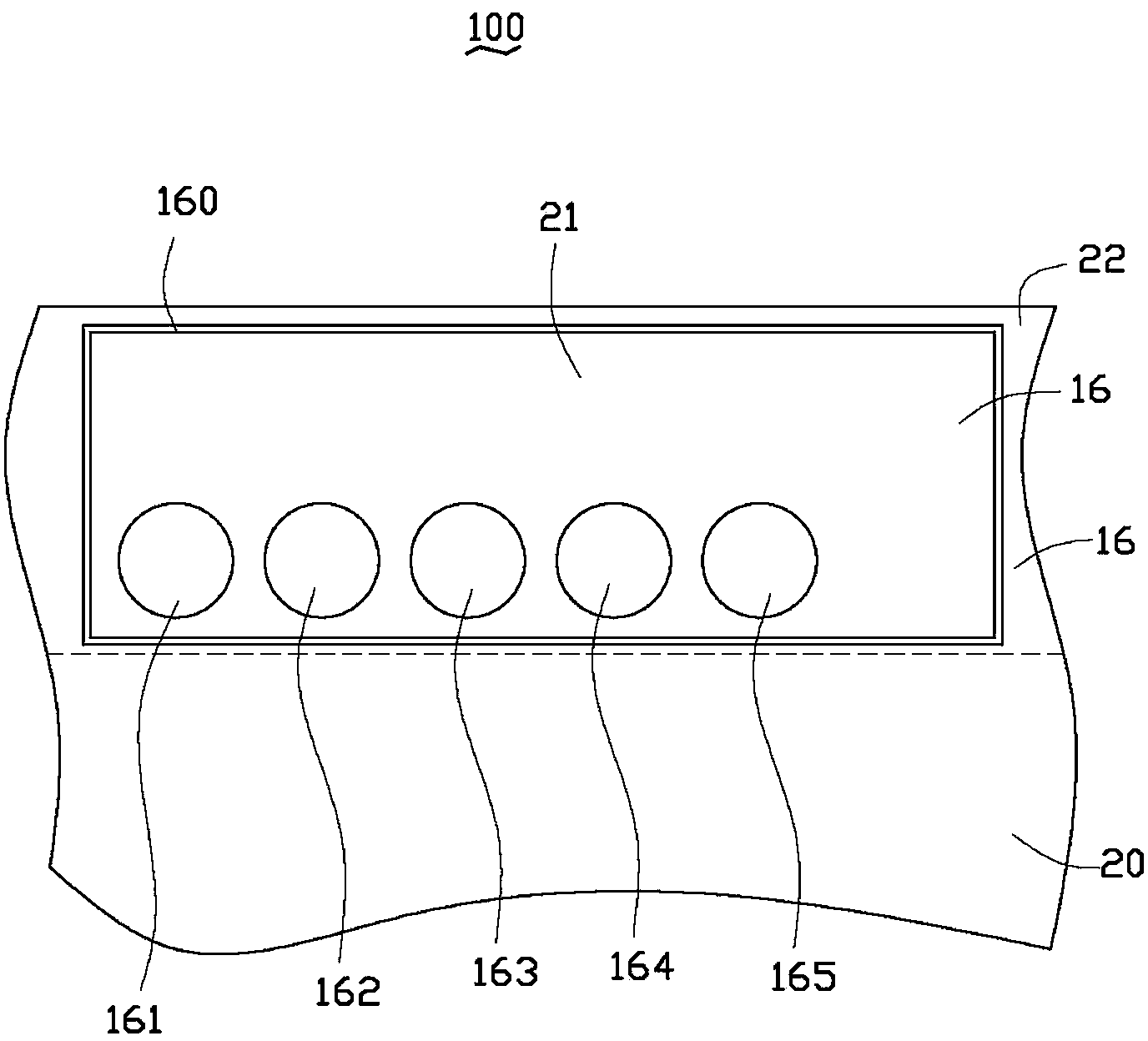

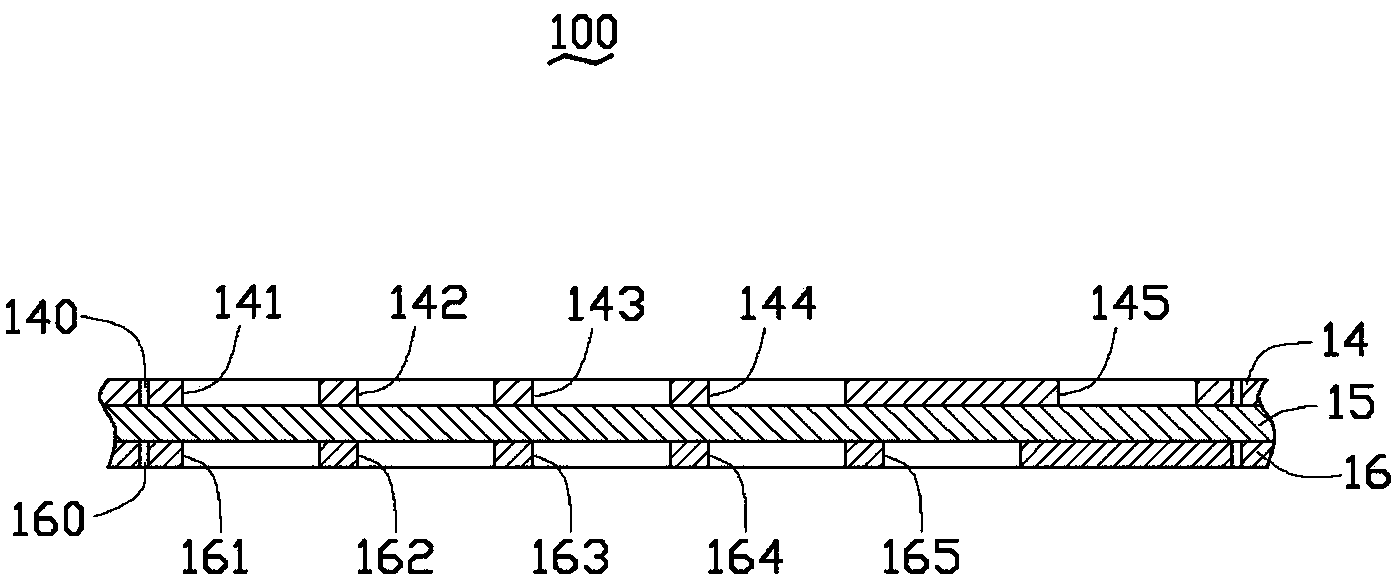

Multilayer circuit board and method for manufacturing same

ActiveCN103796415ASimple test equipmentReduce test cost and detection costElectrical connection printed elementsMultilayer circuit manufactureElectrical and Electronics engineeringEngineering

Owner:LEADING INTERCONNECT SEMICON TECH SHENZHEN CO LTD +2

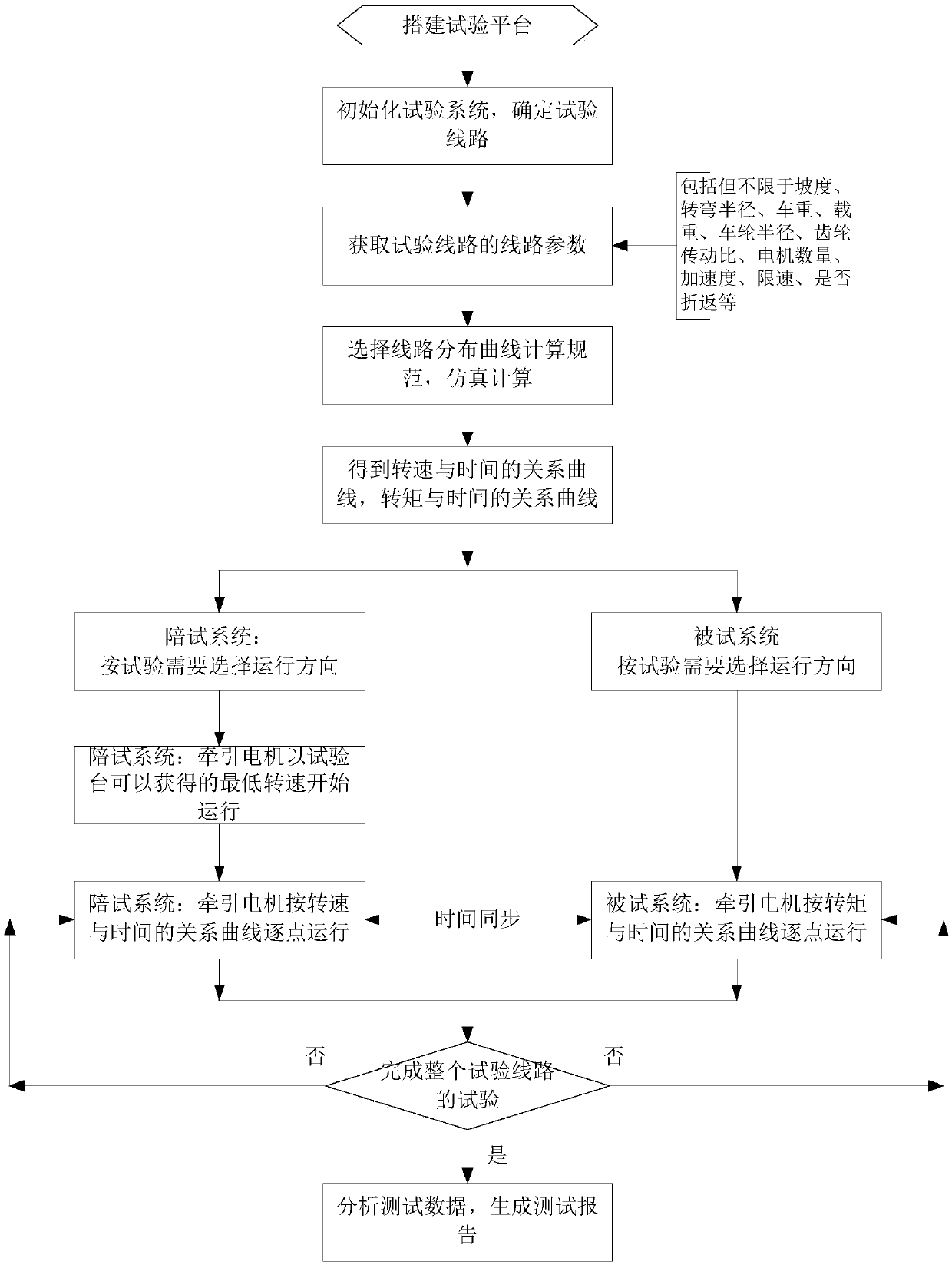

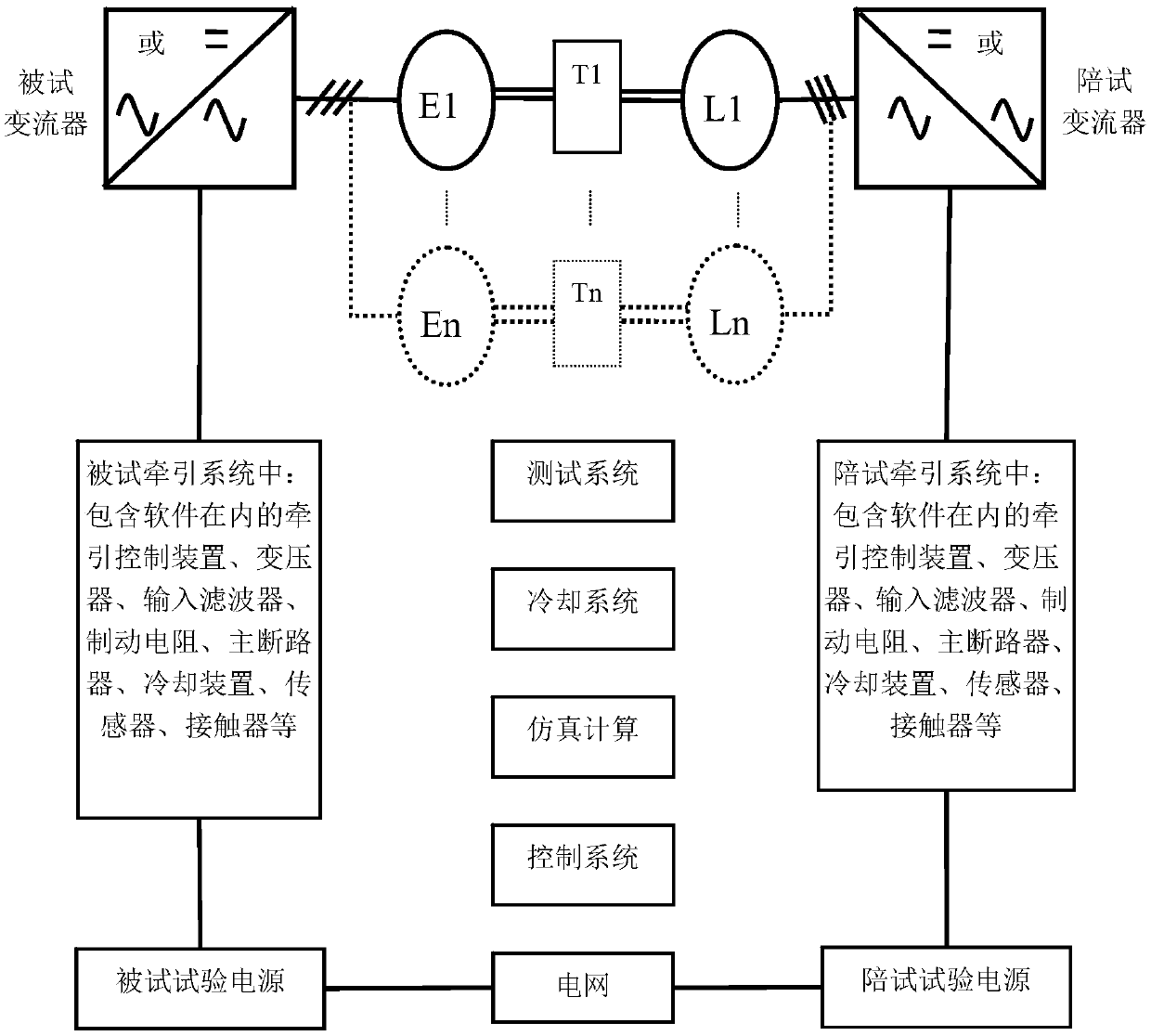

Rail transit traction system test method and system

InactiveCN110320057AHigh simulation fidelityThe test result is accurate and goodRailway vehicle testingTraction motorTraction system

The invention discloses a rail transit traction system test method and system. The method comprises the following steps of: S1. initializing a test system and determining a test line; S2. simulating and determining a first relation curve and a second relation curve when a train runs on the test line, wherein the first relation curve is a relation curve of the rotating speed and the time of a traction motor, and the second relation curve is a relation curve of the torque and the time of the traction motor; S3. operating an accompanying system according to the first relation curve, operating a tested system according to the second relation curve, and detecting and obtaining detection data of each detection sensor of the tested system; and S4. generating a detection report according to the detection data. The rail transit traction system test method and system have the advantages that the test requirements of the traction system in actual line operation can be simulated, various working conditions such as acceleration, the uniform speed, coasting and braking in actual operation are simulated, the test of the traction system on various indexes such as the temperature and the energy consumption is met, the test process and the test device are simple, and the like.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

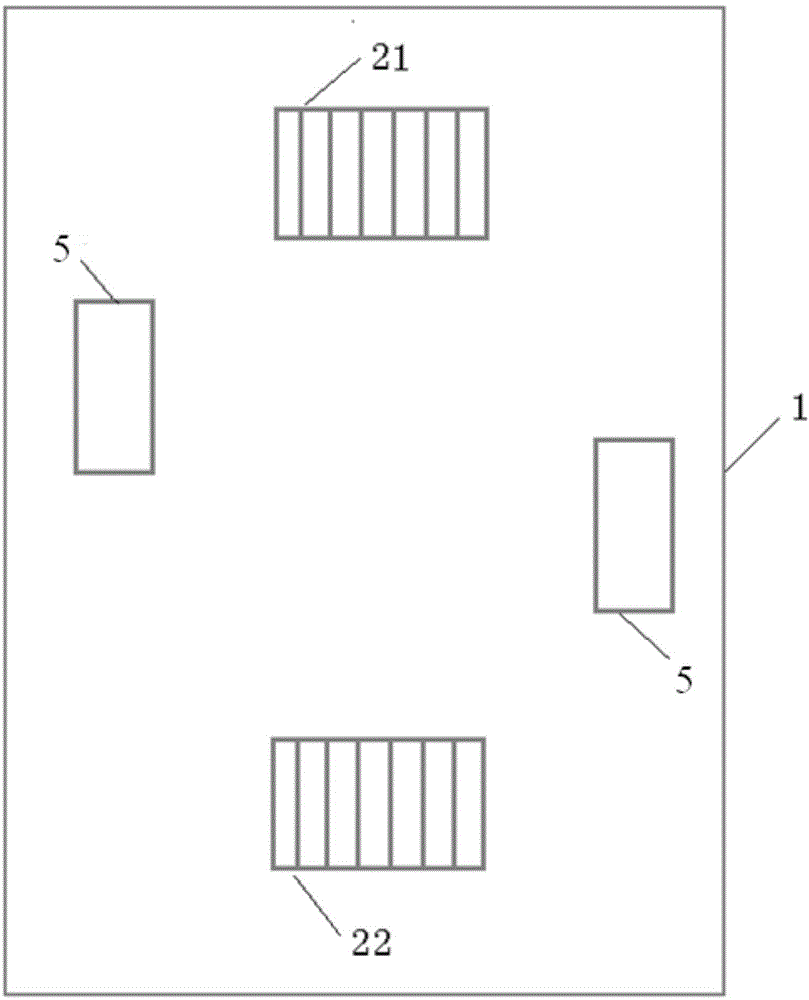

Insulation layer and semiconductor conducting layer aligning error electrical testing structure in micro-electro-mechanical system

InactiveCN101144701ASimple test methodSimple test equipmentSemi-permeable membranesSemiconductor/solid-state device testing/measurementTest structureElectricity

The invention relates to an electricity test structure of an alignment error of an isolation layer graph and a semiconductor conducting layer graph in a microcomputer electrical system part process. The test structure of the alignment error is designed with a metallic layer as a base layer, a semiconductor layer in the structure is a semiconductor that two blocks are separated, the material is same and the graph is different, one block is a ladder type, the other block is a rectangular, the both blocks are parallel; a metallic layer that is touched with the semiconductor layer and forms a connection is two metal strips that are parallel and have an interval, wherein, the upper and lower bottoms of the ladder type and two long edges of the rectangular are vertically covered with one strip, the obtuse angle part of the ladder type and the two long edges of the rectangular are covered with the other strip and truncated in the isolation region between two semiconductors, the part of the metal strip is respectively corresponding to the isolation layer under the semiconductor layer, a strip pin hole is established accordingly, the size of the pin hole is less than the metal strip of a corresponding part and can cover the same part of the ladder type semiconductor and the rectangular semiconductor like the metal strip, a resistance provided with a connecting line is formed in common by two metallic strips and the semiconductor between the two metallic strips, when a relative offset is existent between the isolation layer graph and the semiconductor conducting layer graph, the R2 change is tested, and the alignment error of the isolation layer graph and semiconductor conducting layer graph are obtained.

Owner:SOUTHEAST UNIV

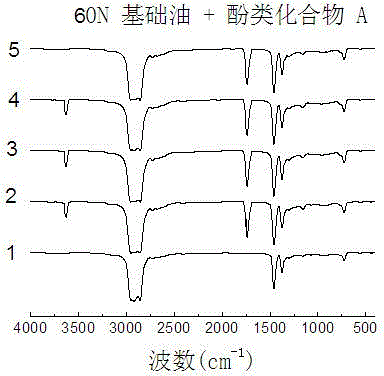

Method for detecting stability of phenolic substance on friction interface

InactiveCN104568817ASimple test equipmentEasy to operateMaterial analysis by optical meansAmount of substanceTest equipment

The invention discloses a method for detecting the stability of a phenolic substance on a friction interface. The method comprises the following steps: adding the phenolic substance into lubricating oil to prepare a phenolic lubricating oil sample for wear experiments; and testing changes of phenolic hydroxyl functional groups of the lubricating oil sample before and after wearing by using an infrared spectrum to determine the stability of the phenolic substance in a wear process. The changes of the functional groups of the sample on a wear interface are tested by virtue of an infrared spectrum method, thereby determining the stability of the phenolic substance on the friction interface; and the test condition is mild (25-75 DEG C and normal pressure), the test equipment is simple, the operation is simple and quick, the time consumption is low, the cost is low, the safety is high, and the accuracy is very high. Experiments show that the stability of the phenolic substance on the friction interface can be effectively identified by observing infrared spectrum changes of the sample before and after wearing.

Owner:SUN YAT SEN UNIV

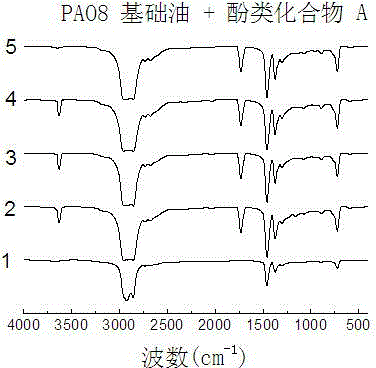

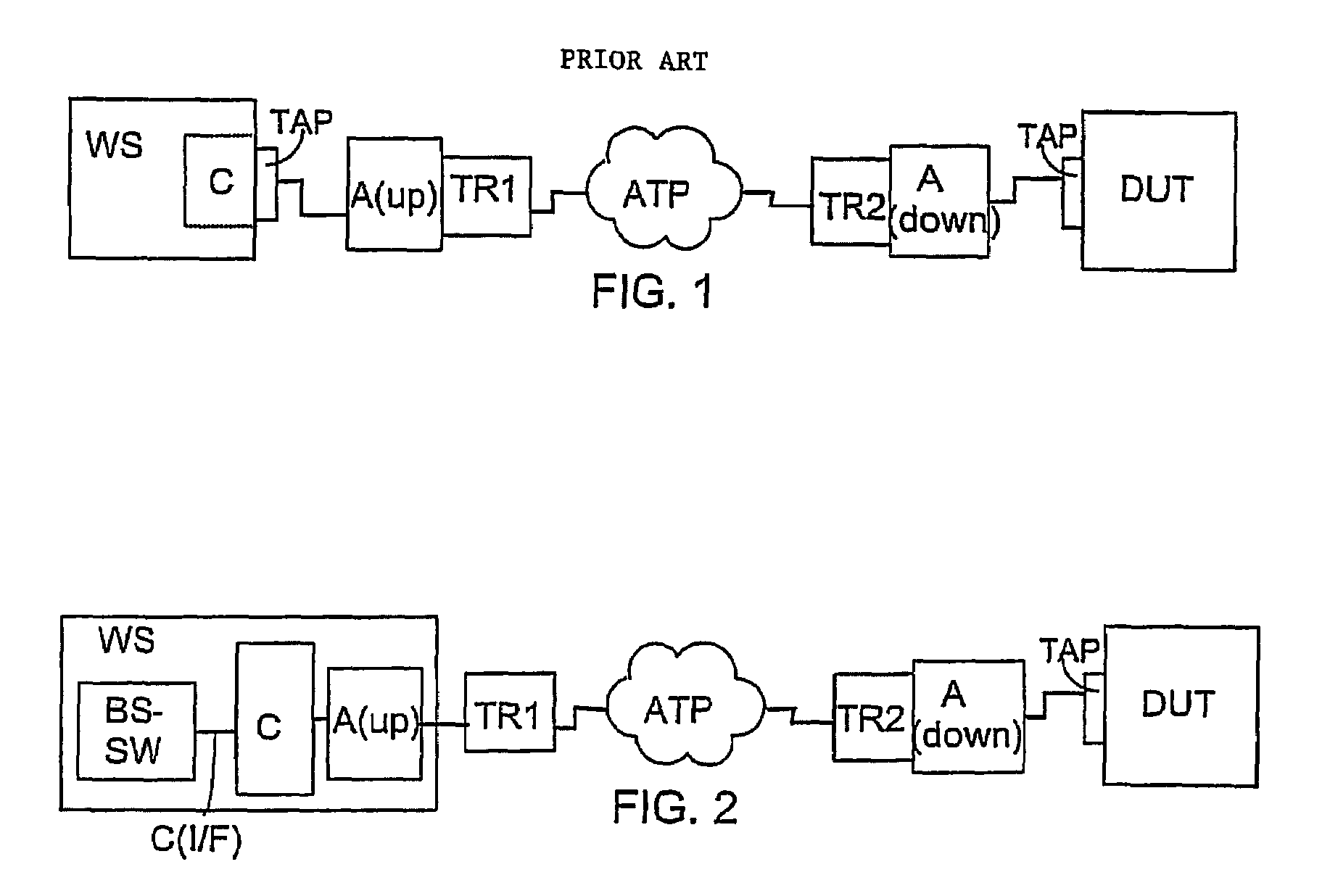

JTAG testing arrangement

ActiveUS7536616B2Reduce in quantitySimple test equipmentElectronic circuit testingStructural/machines measurementTransceiverJoint Test Action Group

JTAG test equipment arranged to establish an asynchronous data transmission connection with a JTAG-compatible device under test for the transmission of test data between test access ports (TAP) in the test equipment and device under test. The test data is synchronized at reception before the test access ports (TAP). The test equipment includes a computer program for adapting a test data sequence arriving in the format defined by the test access port for transmission on an asynchronous transmission path, and a transceiver (TR1) for adapting the test data sequence and transmitting it through the asynchronous data transmission connection to the device under test.

Owner:JTAG TECH

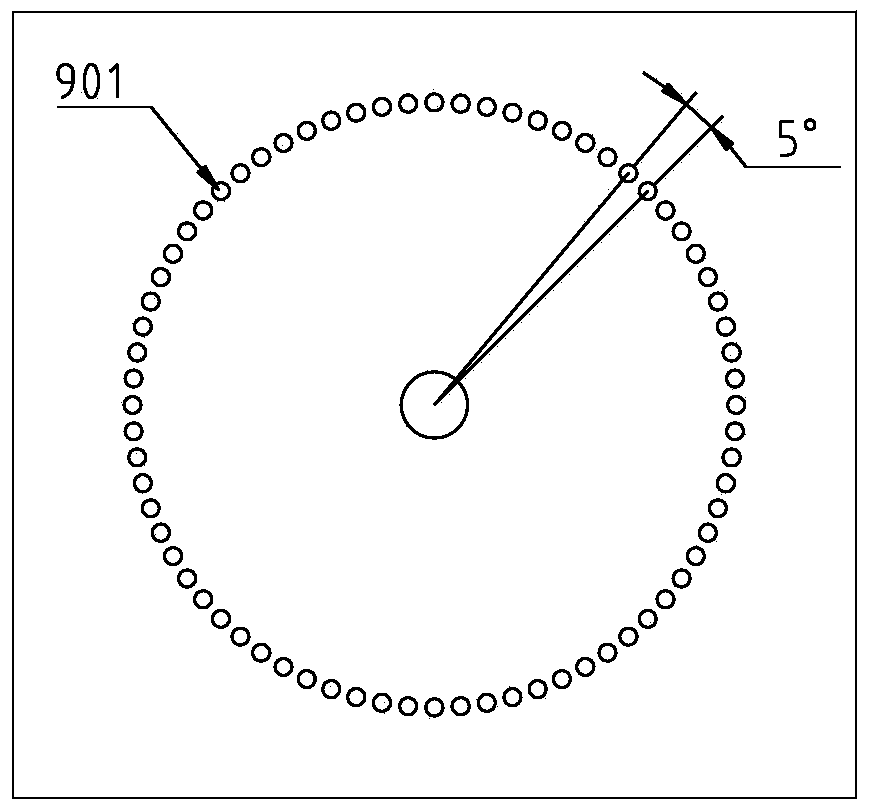

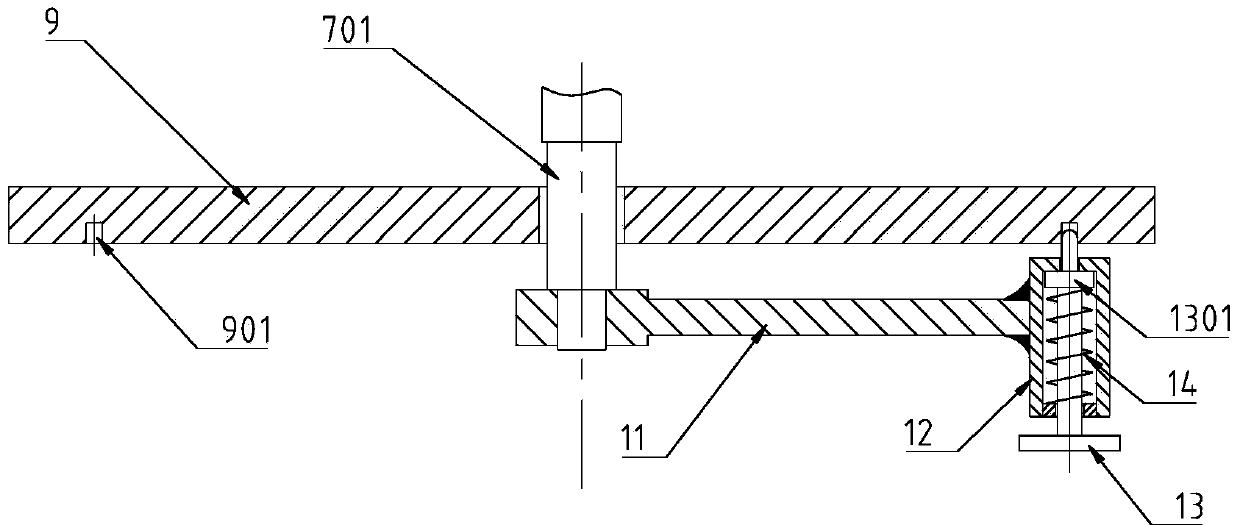

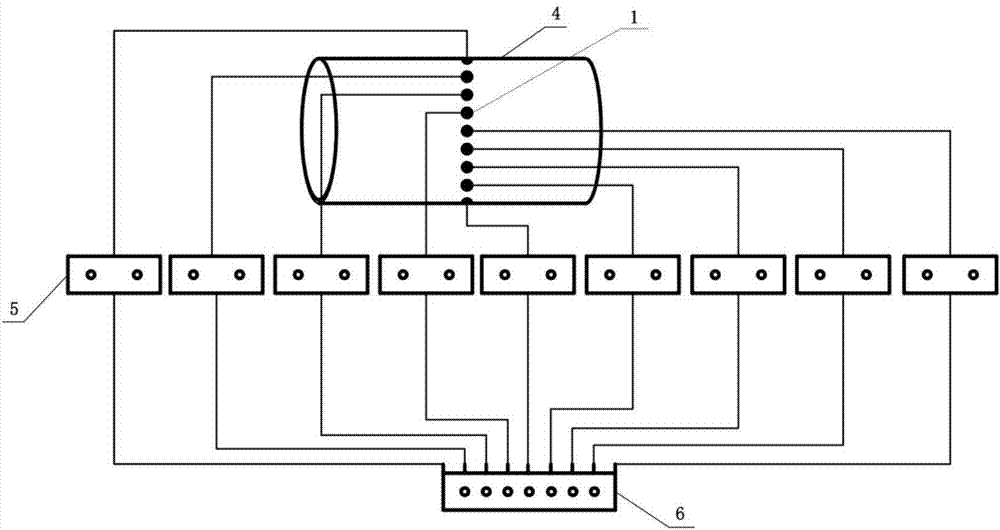

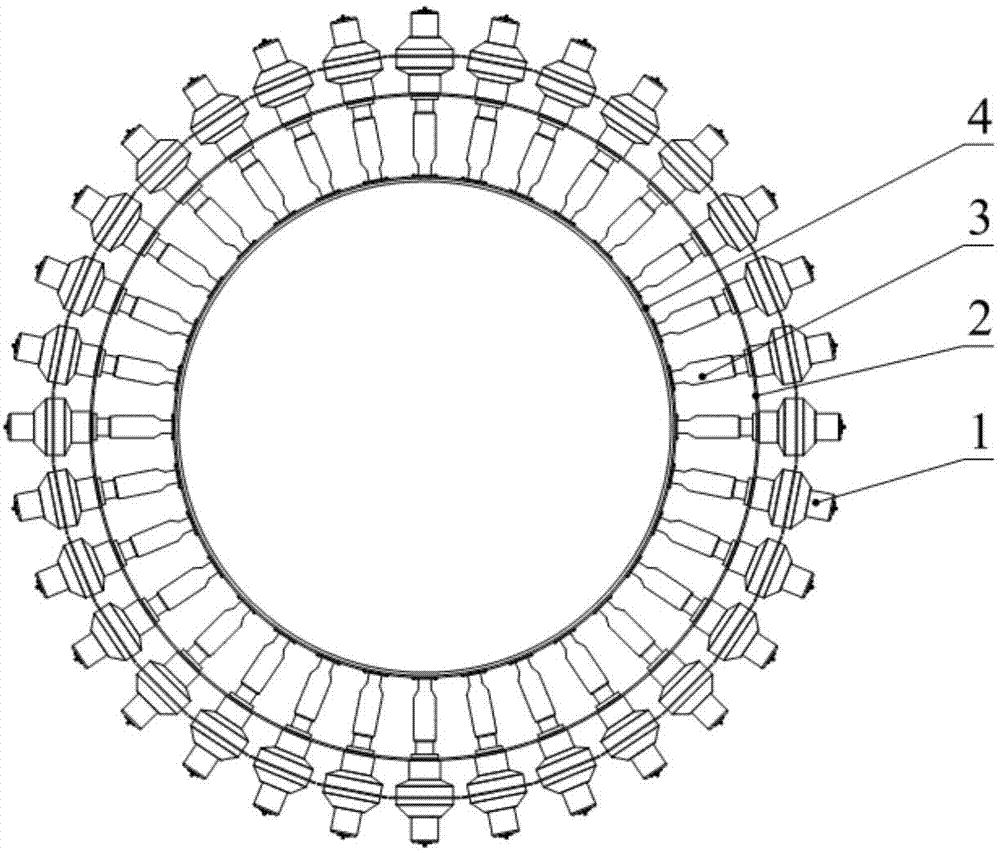

Rotary sound source generating device

The invention relates to a sound source generating device, in particular to a rotary sound source generating device suitable for aeroengine fan noise study. The rotary sound source generating device comprises a multichannel signal generator, a power amplifier and a sounding device which are serially connected through a lead, the multichannel signal generator is provided with two output ports which are in lead connection with the power amplifier, the power amplifier is in lead connection with a loudspeaker and is provided with a loudspeaker clamp to clamp and fix the loudspeaker, the loudspeaker is in threaded connection with one ends of waveguide tubes, the other ends of the waveguide tubes are connected with a simulation pipeline through flanges, the simulation pipeline is of a cylindrical structure, and the waveguide tubes are annularly and uniformly arranged on the simulation pipeline. The rotary sound source generating device can replace fan blades through frequency or replace blades through frequency to harmonize noise of frequency, and is simple in structure, experiment cost can be lowered, and accuracy and efficiency of experiments are improved.

Owner:CHINA AIRPLANT STRENGTH RES INST

Asphalt mixture static modulus testing method

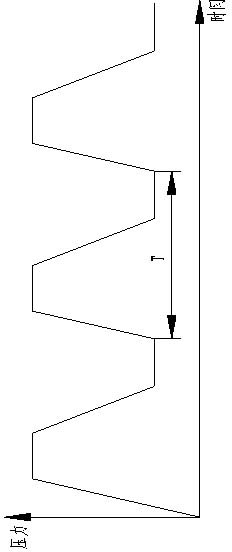

InactiveCN103245561AEasy to operateSimple test equipmentMaterial strength using tensile/compressive forcesPitch blendeAsphalt

The invention discloses an asphalt mixture static modulus testing method comprising the following steps of: (1) preparing a cylindrical test piece of an asphalt mixture, and two steel pressure heads; (2) placing the cylindrical test piece and the two steel pressure heads into a thermostat with target temperature, and preserving heat for more than 5 hours; (3) taking out the cylindrical test piece and the two steel pressure heads, respectively arranging the two steel pressure heads at the centers of two end faces of the cylindrical test piece; (4) loading the cylindrical test piece by means of changing the load speed of the steel pressure head, and simultaneously recording the load-deformation curve of the cylindrical test piece; and (5) calculating the static modulus of the asphalt mixture according to the load-deformation curve and the structure size of the cylindrical test piece. According to the asphalt mixture static modulus testing method provided by the invention, the used local loading test can effectively simulate the side constraint to the asphalt mixture in the actual road surface; and the test devices used in the method are simple and easy to operate, so that the test can be carried out in normal laboratories.

Owner:SOUTHEAST UNIV +1

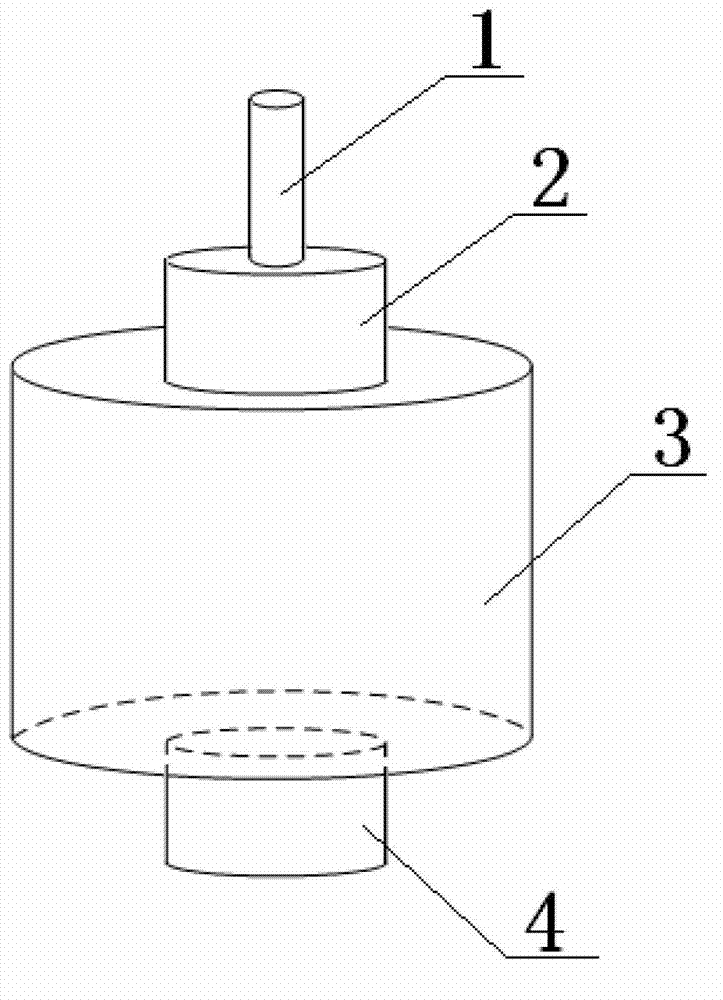

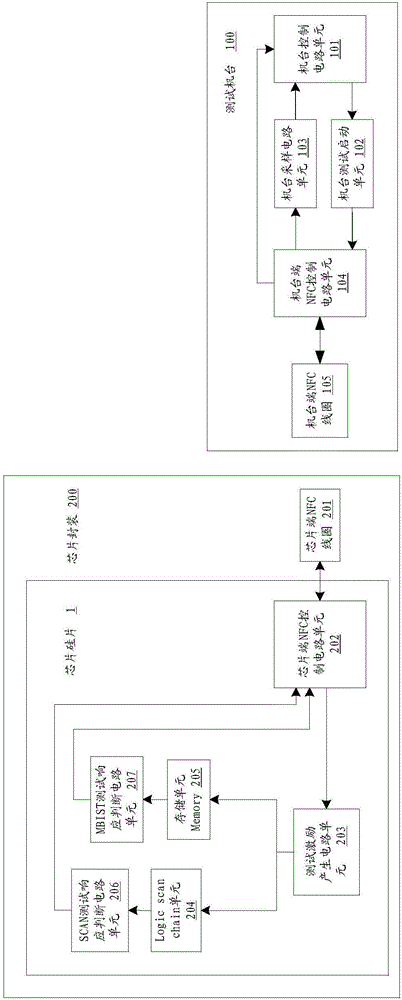

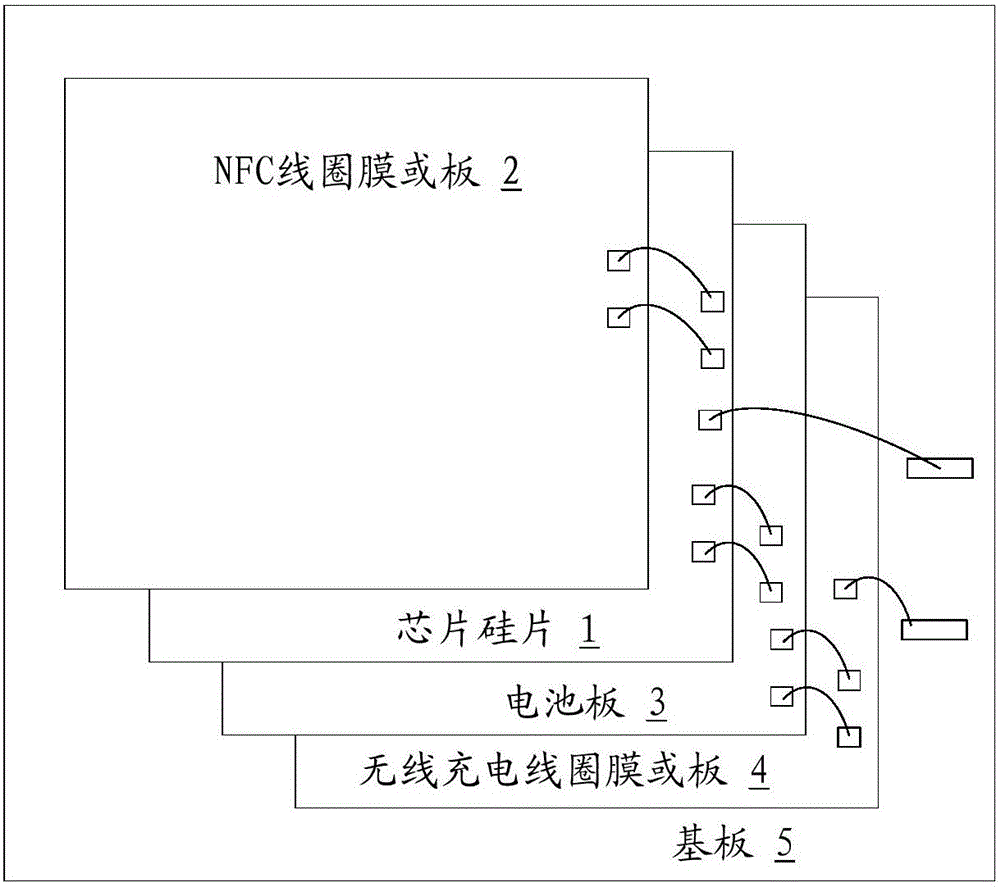

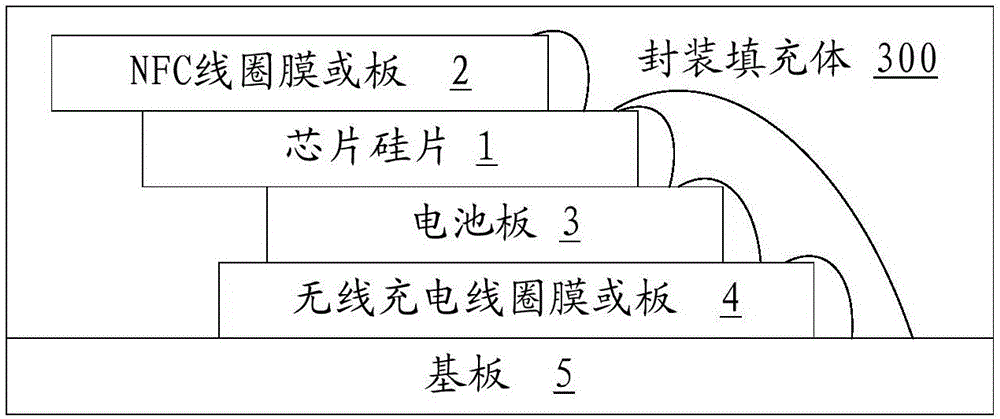

Wireless testing circuit and method for chip

ActiveCN106324485AImprove the production and development processSimple test equipmentElectronic circuit testingSampling circuitsTest response

The invention provides a wireless testing circuit for a chip, and the wireless testing circuit comprises a testing machine circuit and a chip internal circuit. The testing machine circuit comprises a machine control circuit unit, a machine testing start unit, a machine sampling circuit unit, a machine end NFC control circuit, and a machine end NFC coil. The chip internal circuit comprises a chip end NFC coil, a chip end NFC control circuit unit, a testing excitation generation circuit unit, a logistic_scan_chain unit, a storage unit Memory, a scan test response judgment circuit unit, and an MBIST testing response judgment circuit unit. During testing, the testing machine circuit sends a testing start command to the chip internal circuit. The chip internal circuit generates a testing excitation to perform the testing of the chip, wherein the testing comprises the scanning of the logic circuit of the chip and the memory bist testing. A testing result is transmitted to the testing machine circuit in a wireless manner through NFC. The circuit can carry out the verification and testing of the chip under the condition that there is no physical connection.

Owner:FUZHOU ROCKCHIP SEMICON