Data processing circuit with multiplexed memory

A memory circuit and data processing technology, applied in electrical digital data processing, instrumentation, climate sustainability, etc., can solve the problems of limited operation speed and high power consumption of equipment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

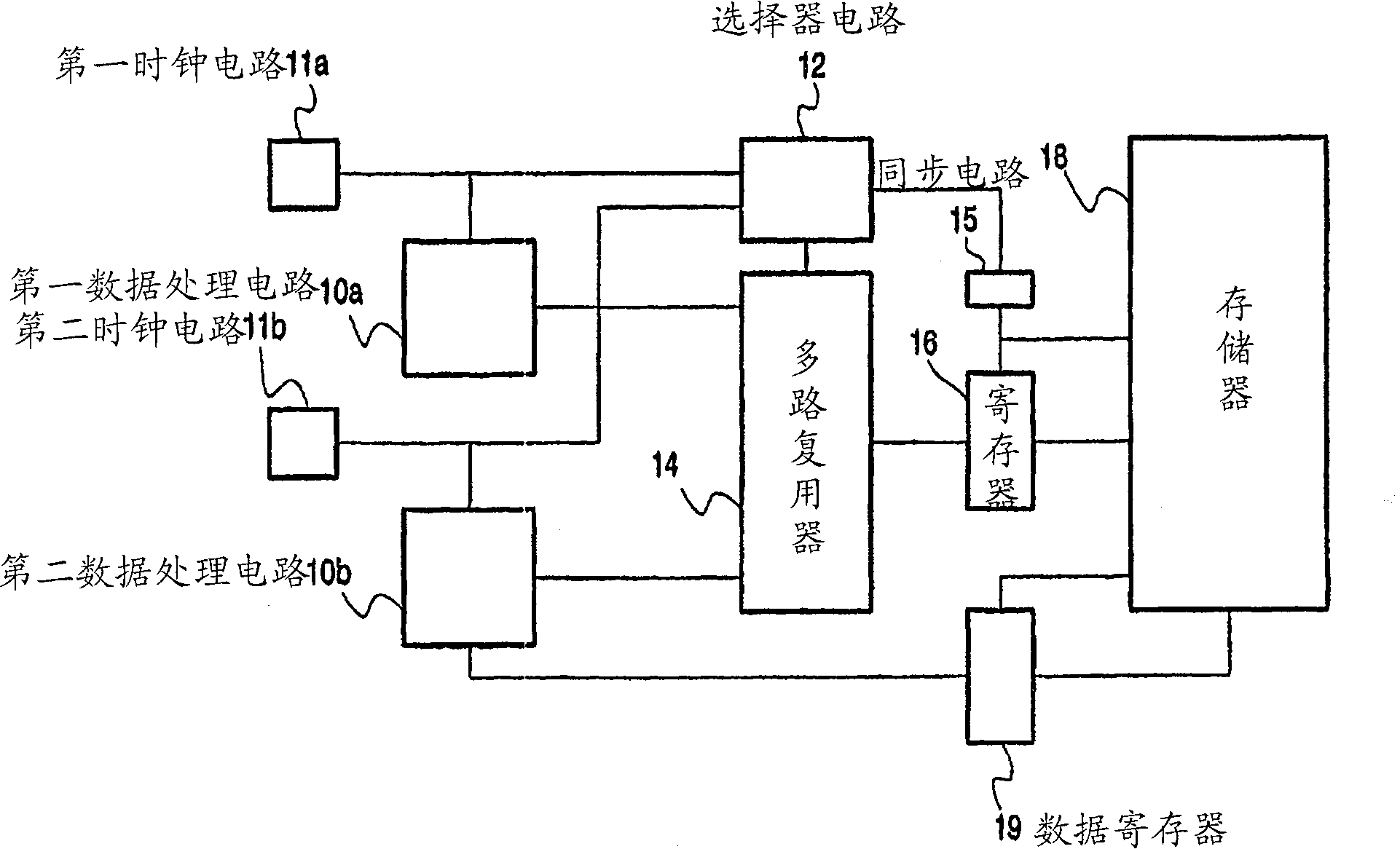

[0030] figure 1 A circuit is shown with a first data processing circuit 10a, a second data processing circuit 10b, a first clock circuit 11a, a second clock circuit 11b, a selector circuit 12, a multiplexer 14, a synchronization circuit 15 , register 16, memory 18 and data register 19. The first clock circuit 11 a is coupled to the first data processing circuit 10 a and the selector circuit 12 . The second clock circuit 11 b is coupled to the second data processing circuit 10 b and the selector circuit 12 . The first and second data processing circuits 10a, b have an access request information output coupled to an input of a multiplexer 14 which in turn has an output coupled to an input of a register 16 . Selector circuit 12 has a select output coupled to the control input of multiplexer 14 and a timing control output coupled to synchronization circuit 15 . Synchronization circuit 15 has a timing output coupled to register 16 and memory 18 . The data register 19 has an inp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More