Semiconductor encapsulation structure and its making method

A packaging structure, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of occupying printed circuit boards, unable to configure passive components, large connection area, etc., to achieve enhanced Electrical function, the effect of improving electrical function and quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

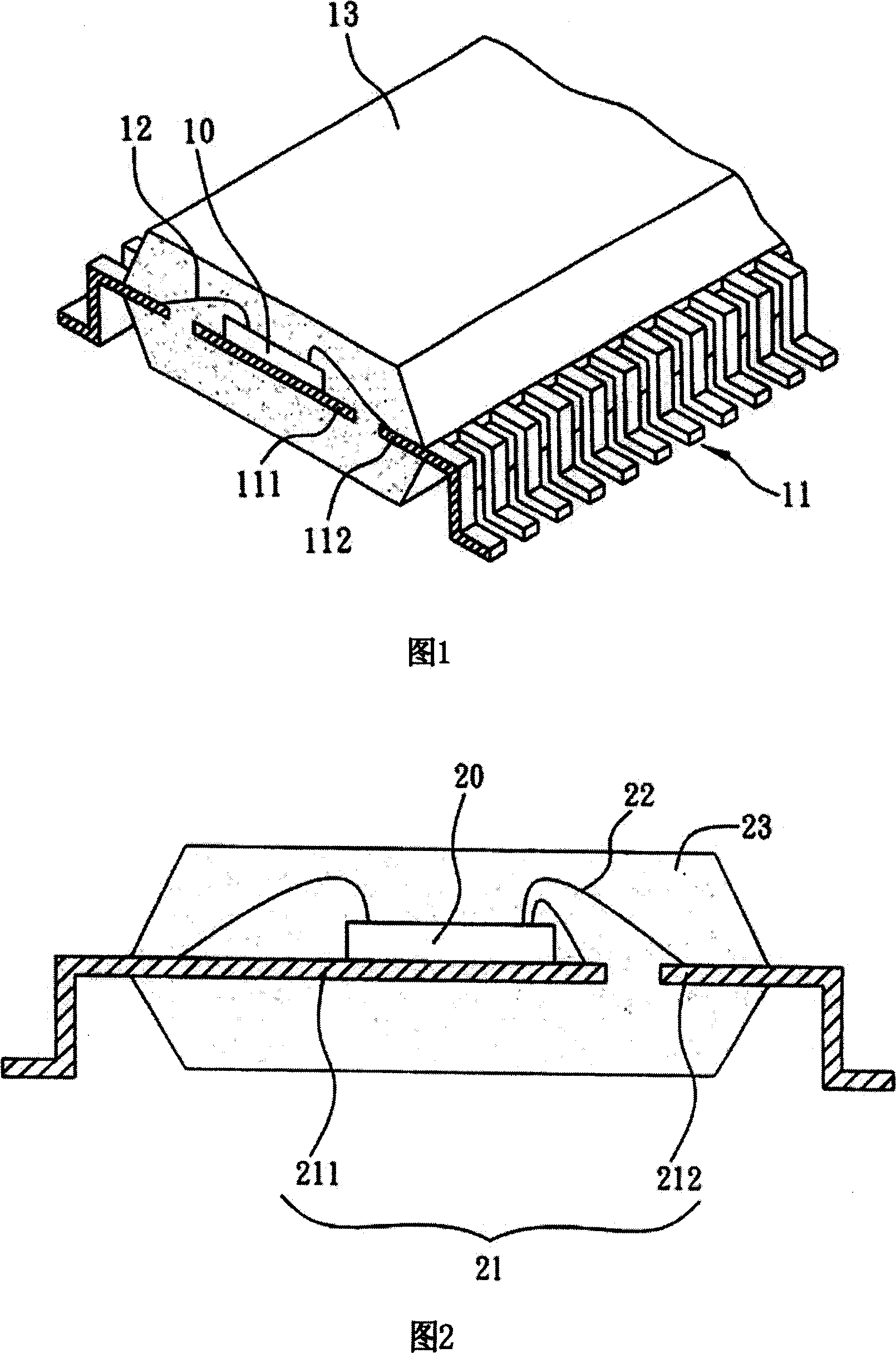

Embodiment 1

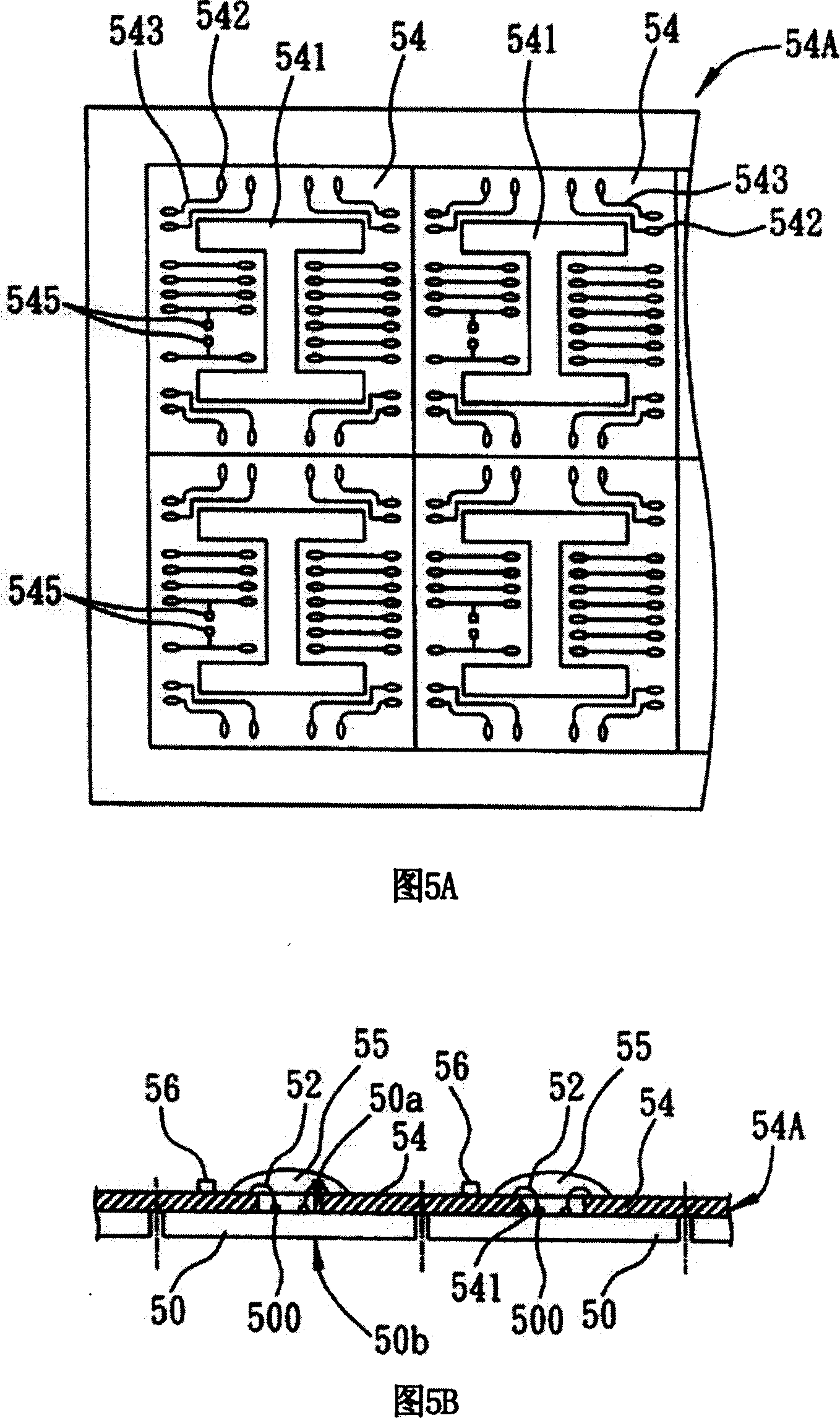

[0040] Please refer to FIG. 5A to FIG. 5E , which are schematic cross-sectional views of Embodiment 1 of the semiconductor package structure and its manufacturing method of the present invention.

[0041] Embodiment 1 of the present invention is mainly described in a batch manner, so as to improve the process efficiency and enable mass production. Of course, it can also be performed in a single wafer manner, and is not limited thereto.

[0042] The manufacturing method of the semiconductor package structure of the present invention includes the following steps. As shown in FIG. 5A, it provides a substrate module sheet 54A with a plurality of substrates 54, and each of the substrates 54 is formed with at least one opening 541, and the form of the opening 541 is corresponding to the semiconductor chip to be packaged subsequently. The layout arrangement of the pads on the active surface. In this embodiment, the bonding pads on the active surface of the semiconductor chip to be p...

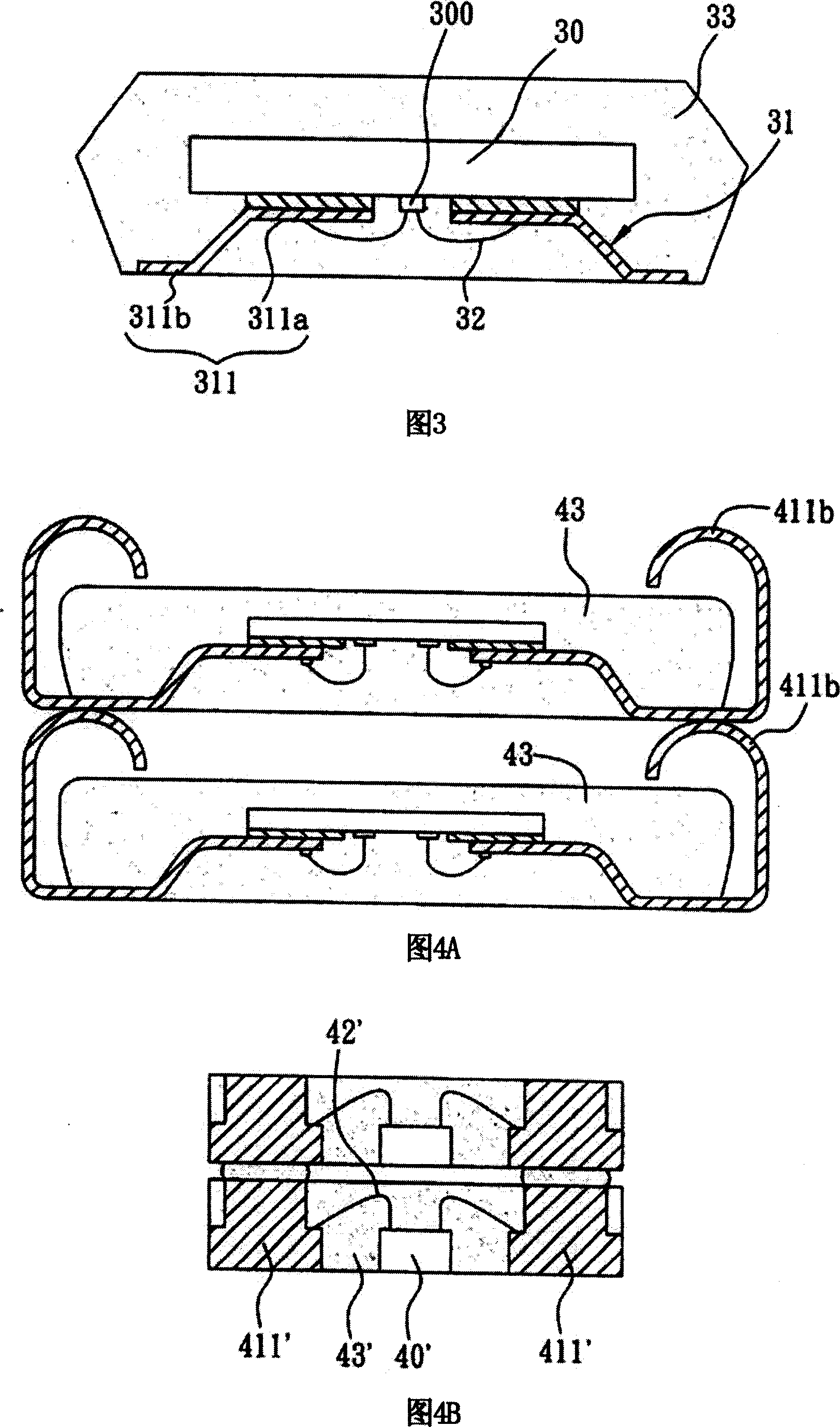

Embodiment 2

[0050] Please also refer to FIG. 6A to FIG. 6D , which are schematic cross-sectional views of Embodiment 2 of the semiconductor package structure and its manufacturing method of the present invention.

[0051] The manufacturing method of the semiconductor package of the present invention includes: as shown in FIG. 6A , providing a lead frame 51 with a plurality of pins 511, and each of the pins 511 has an inner edge 511a and an outer edge 511b that form a gap. The height of the outer edge 511b of the pin is greater than the height of the inner edge 511a, and the semiconductor chip 50 is placed on the inner edge 511a of the pin. The semiconductor chip 50 has an active surface 50a and an opposite non-active surface 50b, and the semiconductor chip 50 is connected to the inner edge 511a of the pin with its non-active surface 50b, and the active surface 50a of the semiconductor chip is provided with a welding pad 500 .

[0052] As shown in Figure 6B, a substrate 54 is placed on th...

Embodiment 3

[0057] Please also refer to FIG. 7 , which is a schematic cross-sectional view of Embodiment 3 of the semiconductor package structure of the present invention.

[0058] Embodiment 3 of the present invention is substantially the same as Embodiment 1 above, the main difference is that the size of the substrate 54 is larger than the size of the semiconductor chip 50, for the semiconductor chip 50 to be placed on the inner edge 511a of the pin 511, and to be connected to the semiconductor chip. The substrate 54 on the lead frame 50 is electrically connected to the pin inner edge 511 a of the lead frame 51 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More