Thin film transistor and pixel structure and its manufacture method

A technology of pixel structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., and can solve problems such as complex process, inability to reduce production cost and output rate, and inability to meet users

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to enable your reviewer to have a further understanding and understanding of the structural features and the achieved effects of the present invention, a preferred embodiment and matching icons are provided for illustration.

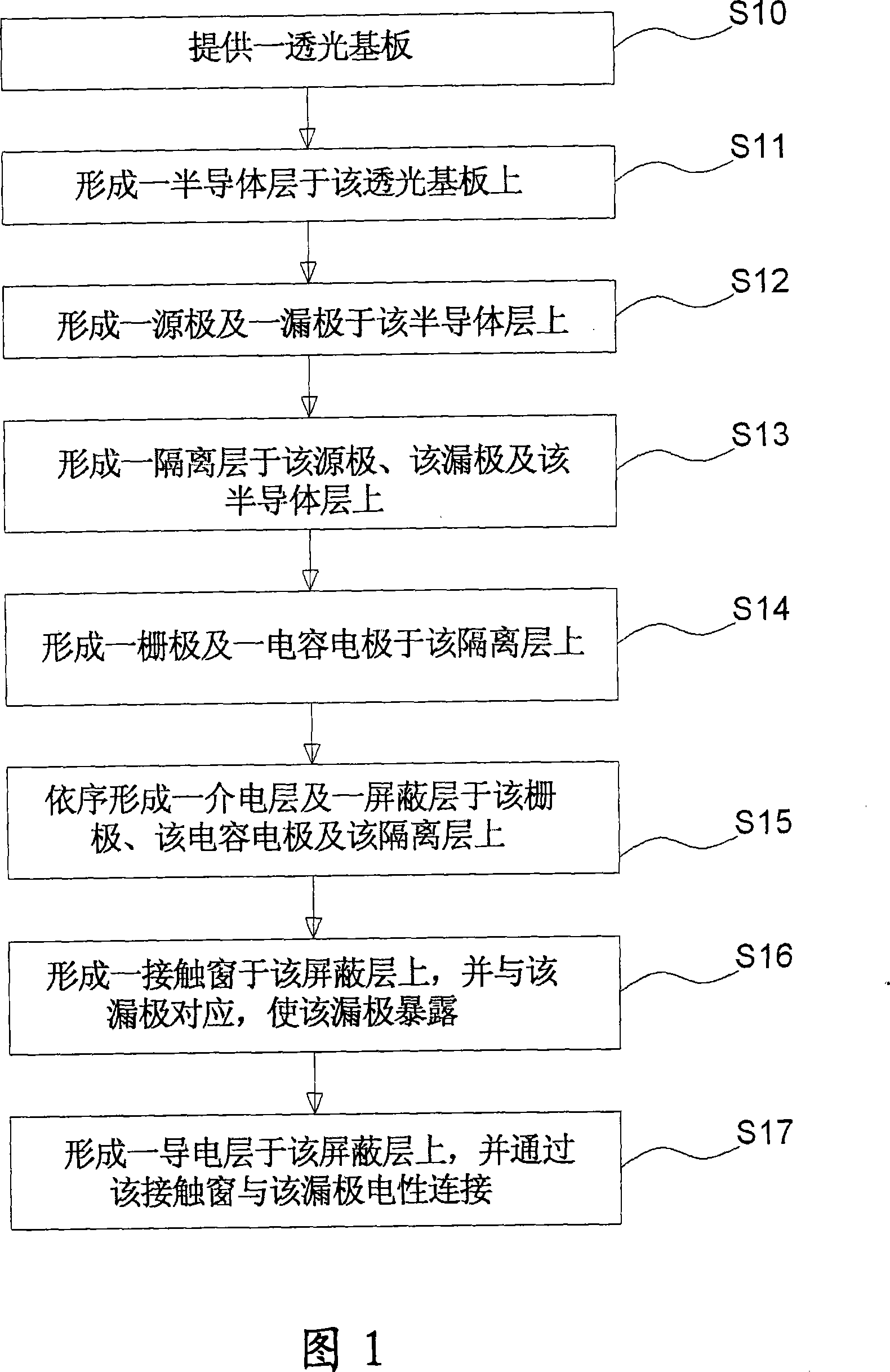

[0044] Please refer to FIG. 1, FIG. 2A and FIG. 2B, which are respectively a schematic diagram of the manufacturing process of the pixel structure of the present invention, a schematic cross-sectional structure diagram of step S10 of the present invention, and a top view structure diagram of step S10 of the present invention. As shown in the figure: the present invention provides a thin film transistor and a pixel structure and a manufacturing method thereof. The manufacturing method of the pixel structure is to first perform step S10 to provide a light-transmitting substrate 10, and the material of the light-transmitting substrate 10 includes glass, quartz Or plastic, but depending on the design requirements, the transparent substrate 10 can...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More