And/not gate type non-volatility memory and manufacturing method and operation method therefor

A non-volatile, manufacturing method technology, applied in the direction of static memory, read-only memory, semiconductor/solid-state device manufacturing, etc., can solve the problems of reading interference and taking a long time, and achieve the effect of reducing coupling interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

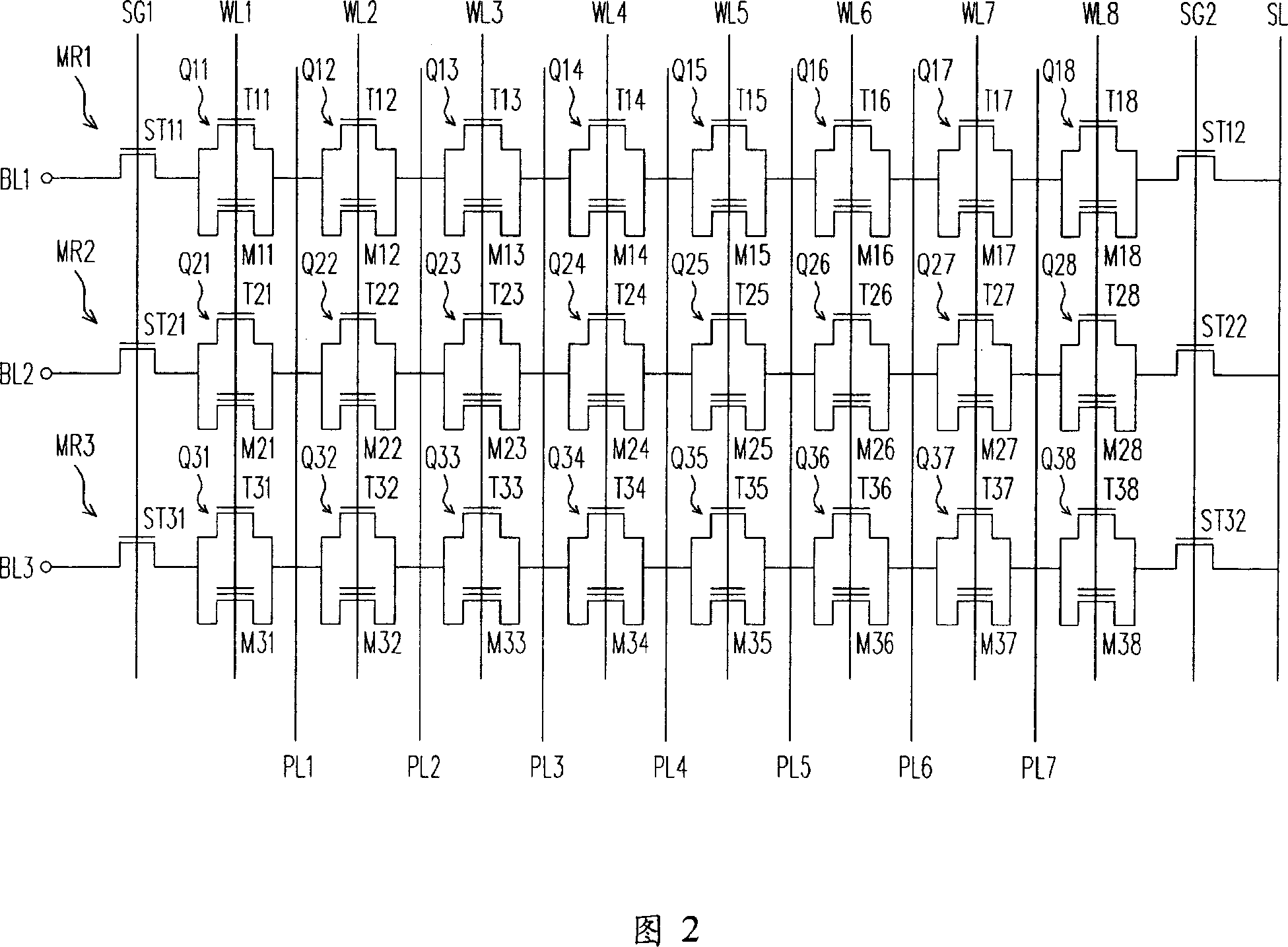

[0100] FIG. 2 is a schematic circuit diagram showing a NAND (NAND) type non-volatile memory array of the present invention. In this embodiment, a row of 8 memory cells and a total of three rows of NAND memory cells are taken as an example for illustration.

[0101] Please refer to FIG. 2, the NAND (NAND gate) type non-volatile memory array includes a plurality of selection transistors ST11-ST31 and ST12-ST32, a plurality of memory cells Q11-Q38, a plurality of word lines WL1-WL8, and selection gate lines SG1 and SG2 , bit lines BL1 - BL3 and pass gate lines PL1 - PL7 .

[0102] Memory cells Q11 to Q18 are connected in series between selection transistor ST11 and selection transistor ST12 to form a memory cell row MR1 in the row direction. The memory cells Q21 to Q28 are connected in series between the selection transistor ST21 and the selection transistor ST22 to form a memory cell row MR2 in the row direction. The memory cells Q31 to Q38 are connected in series between the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More