Method for solving damage of metal oxide semiconductor (MOS) caused by highly rapid load change of voltage regulator (VR)

A technology for changing loads and switching chips, which is applied in the direction of output power conversion devices, measuring devices, electrical components, etc. It can solve problems such as abnormal chip feedback voltage, large coupling interference, and MOS damage, and achieve operational data processing and safe data processing. , Reduce the effect of coupling interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

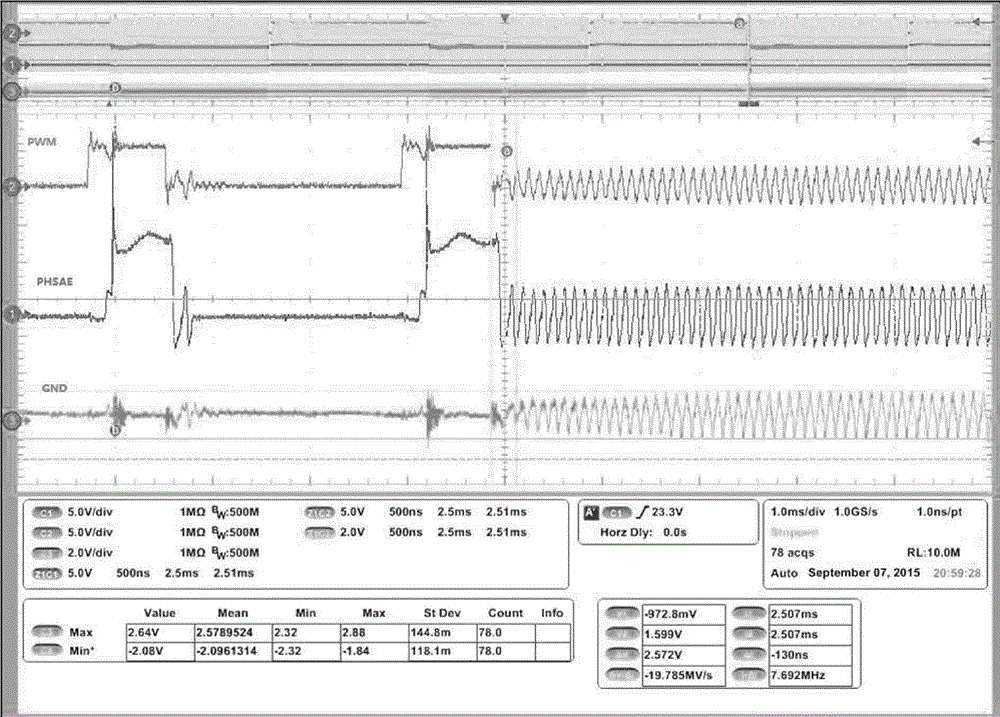

Image

Examples

Embodiment Construction

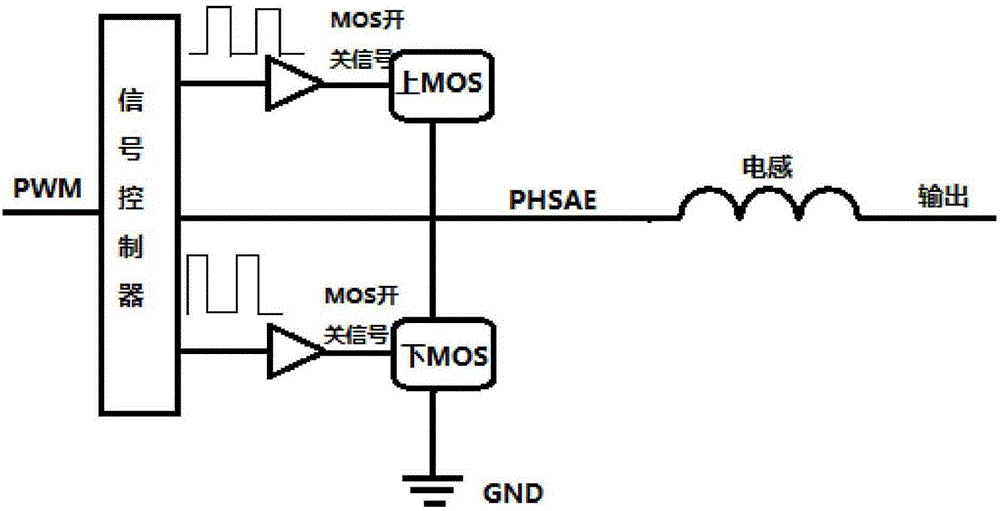

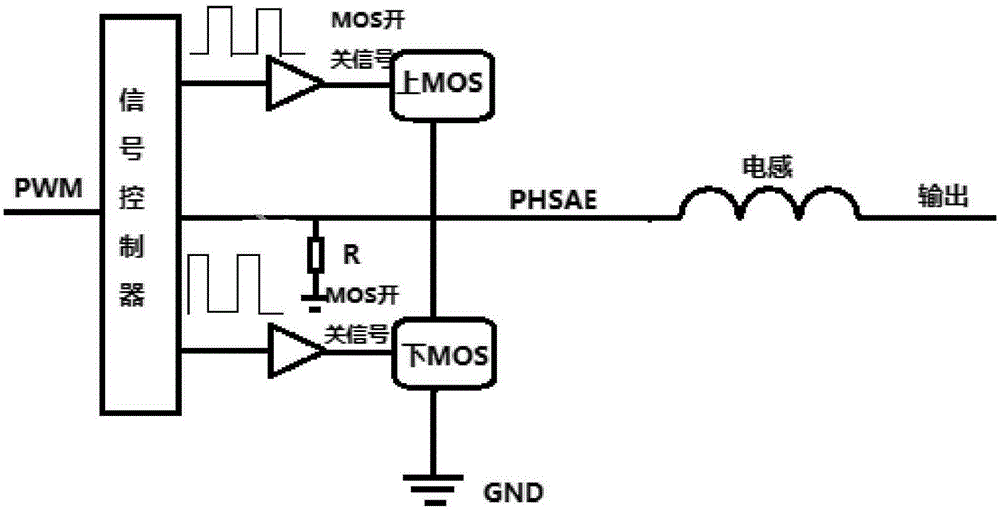

[0020] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0021] The present invention provides a method for solving the problem of MOS damage caused by too fast VR load changes, breaks the fixed configuration of the original server collocation, and more widely supports the design concept of larger data processing volume and faster load change rate. And adopt a new idea: no matter what type of network card, hard disk, etc. the server motherboard is equipped with, the server motherboard can support it, and it will no longer be affected by the excessively fast load change rate during the processing of large amounts of data, resulting in crashes. In this way, the application of server motherboards is wider (lower requirements than server motherboards with fixed configurations), and it can meet the application needs of different users to a greater extent.

[0022] Its specific implementation process is: ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More