Layout structure of electrostatic discharge protecting circuit and its manufacturing method

A technology of electrostatic discharge protection and layout structure, which is applied in the direction of circuits, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as space utilization, and achieve the effects of improving efficiency, saving area, and reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

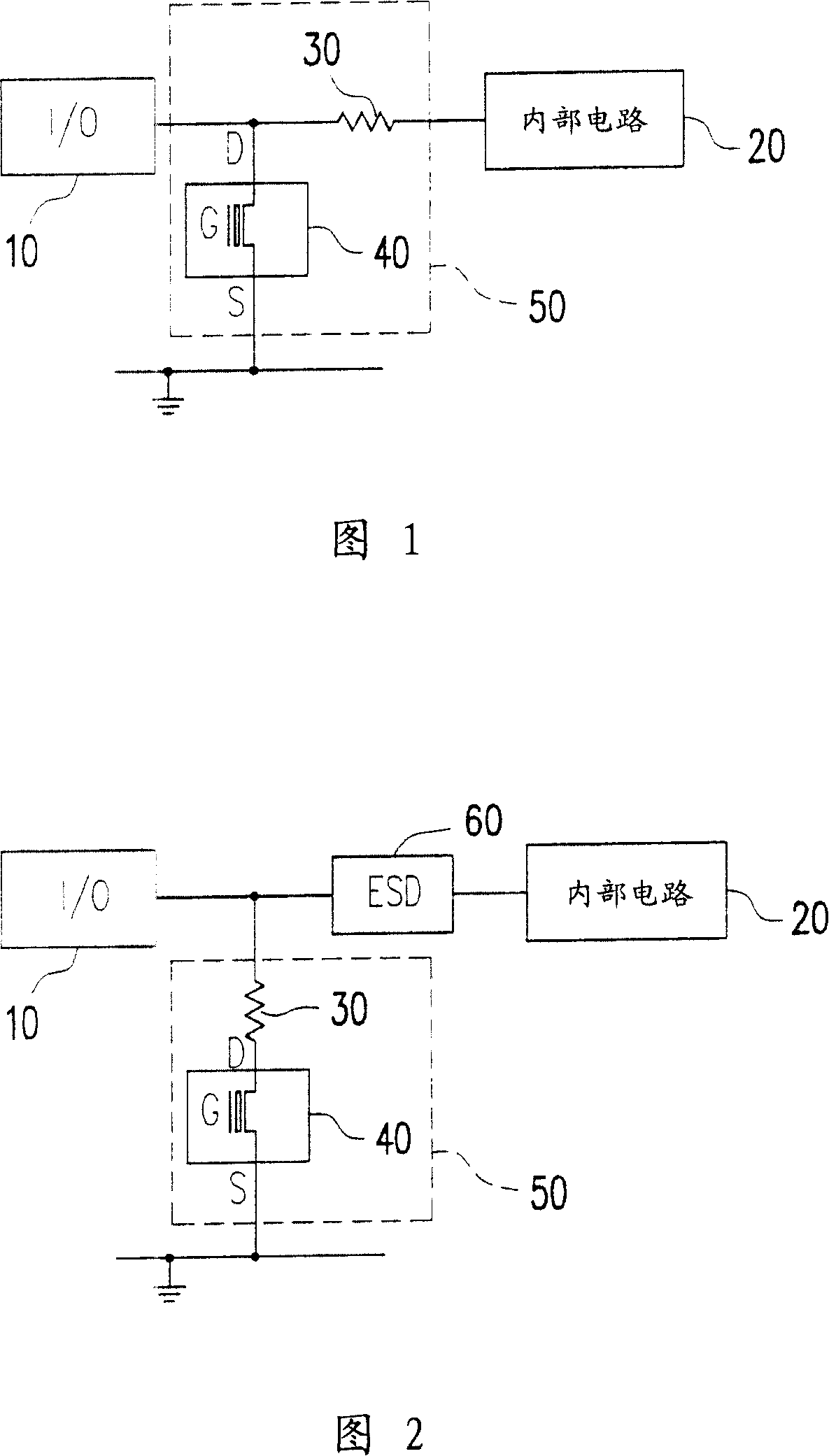

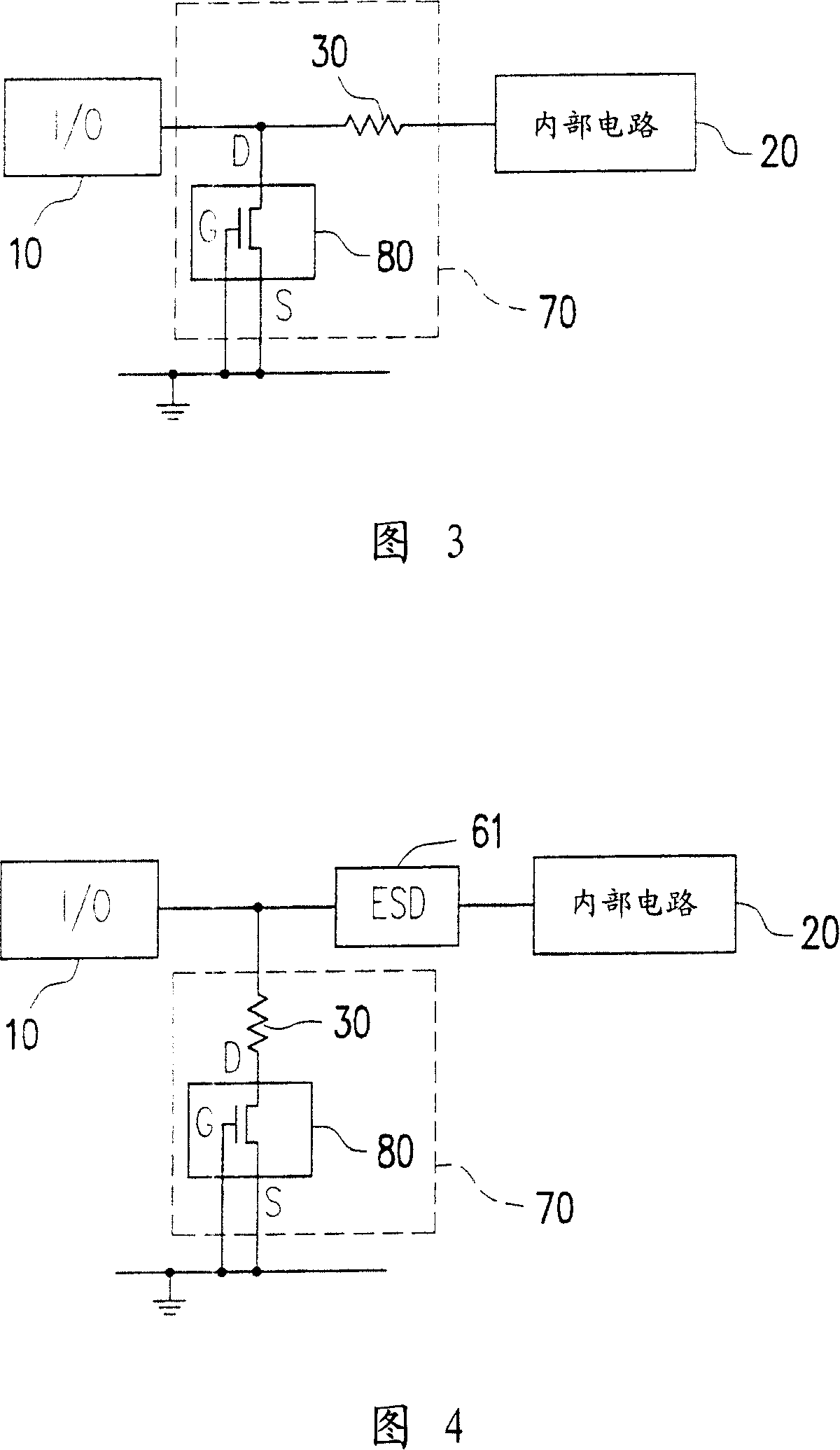

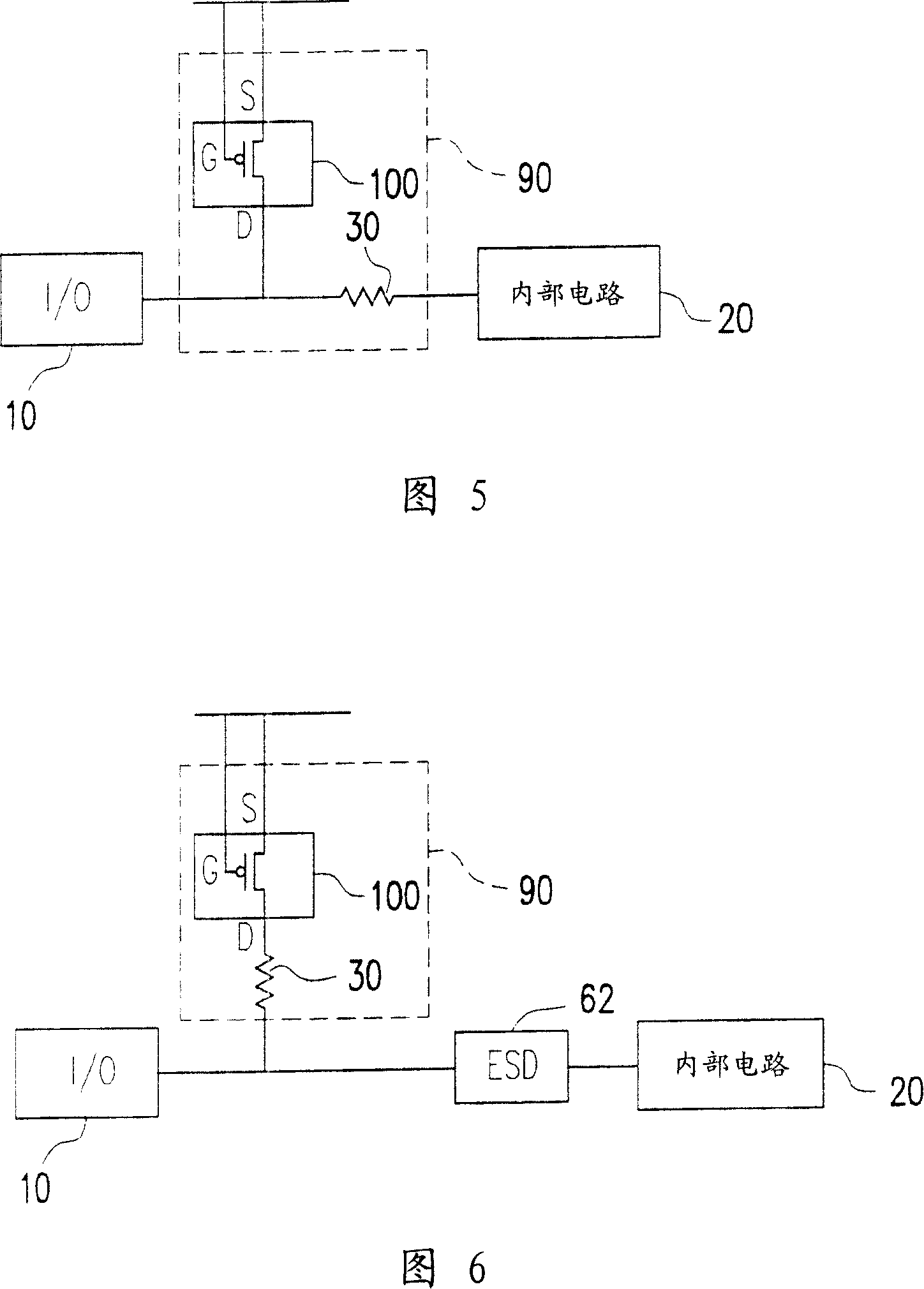

[0045] 1 and 2 are circuit diagrams of an electrostatic discharge protection circuit. Here, a field oxide device (FOD transistor for short) 40 is used as a protection component of the ESD protection circuit 50 . As shown in FIG. 1, in the electrostatic discharge protection circuit 50, a resistor 30 is coupled between the input / output pad (I / O pad) 10 and the internal circuit 20, wherein the resistor 30 is a current limiting resistor, which is used for The electrostatic discharge current is prevented from flowing into the internal circuit 20 through the bonding pad 10 . The drain D of the FOD transistor 40 is coupled between the bonding pad 10 and the resistor 30 , the source S of the FOD transistor 40 is grounded, and the gate G is in a floating state. Therefore, when electrostatic discharge occurs, the electrostatic discharge protection circuit 50 provides an electrostatic discharge current path from the bonding pad 10 to the ground, thereby preventing the internal circuit 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More