Patents

Literature

50results about How to "Reduce the value of parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

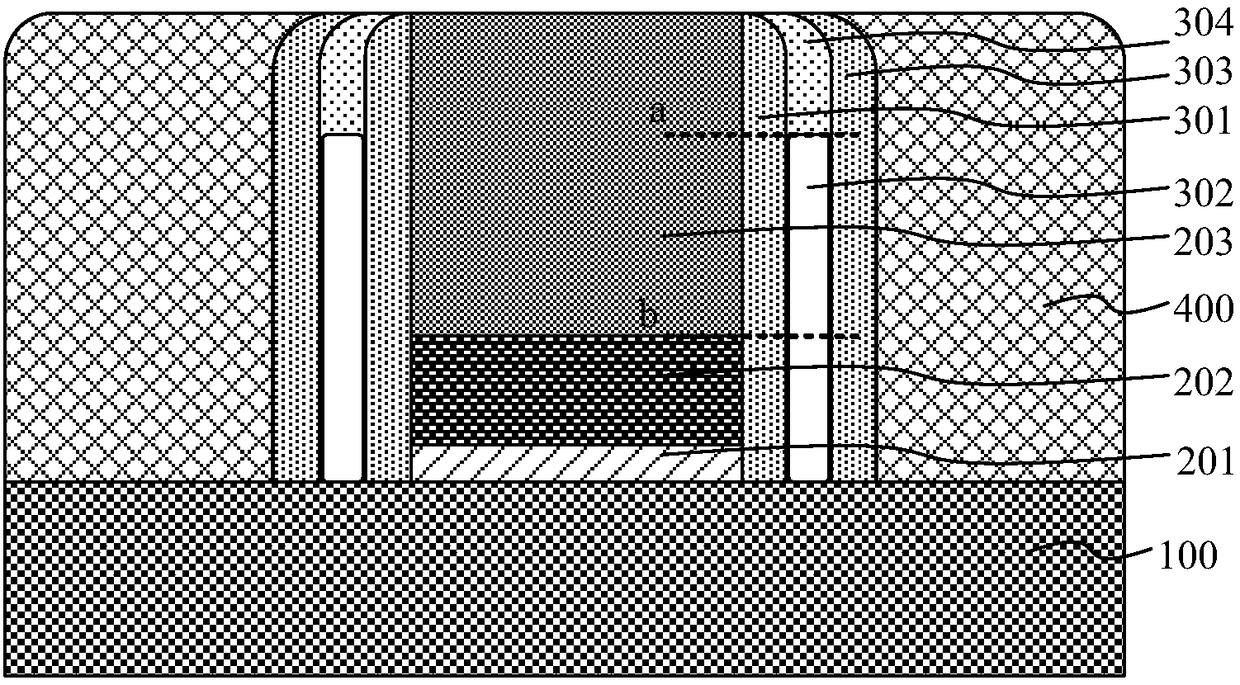

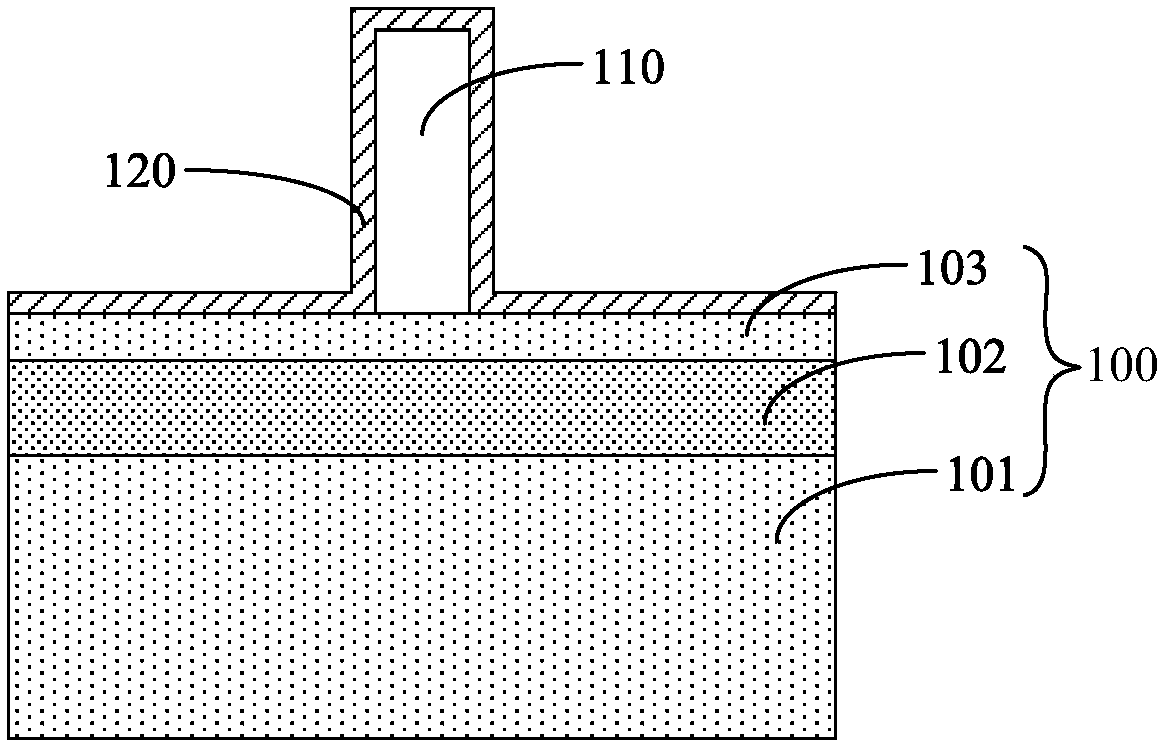

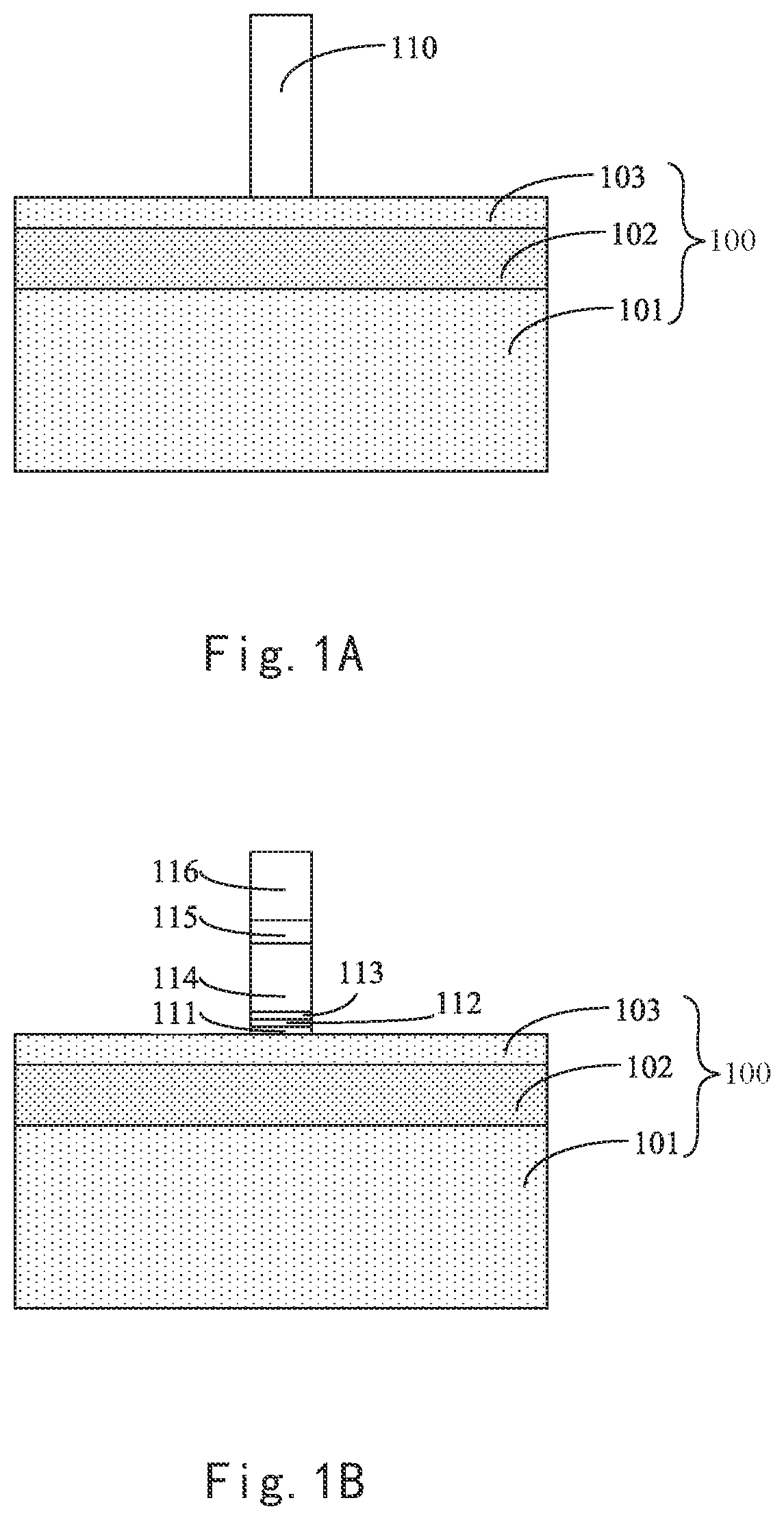

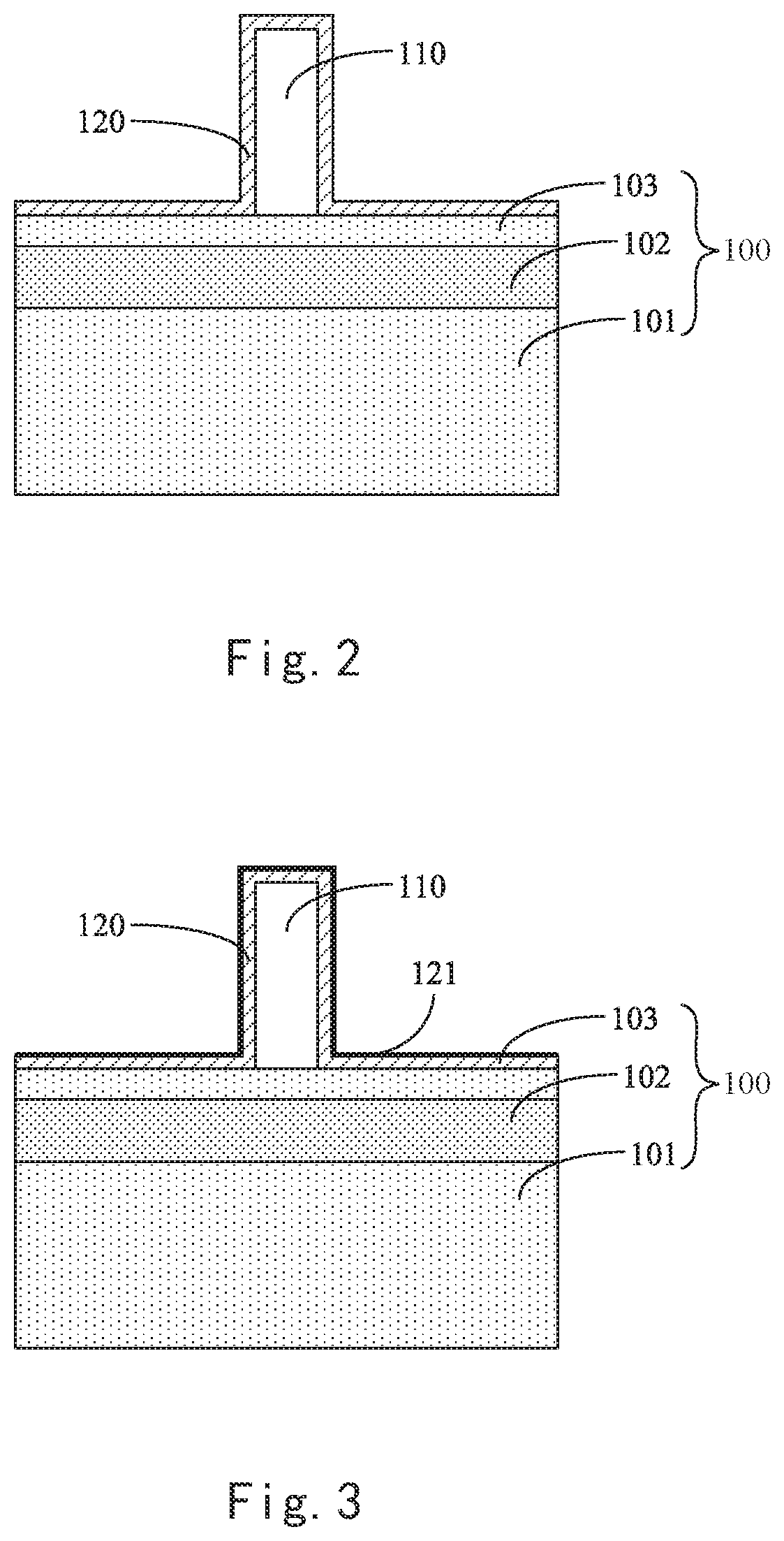

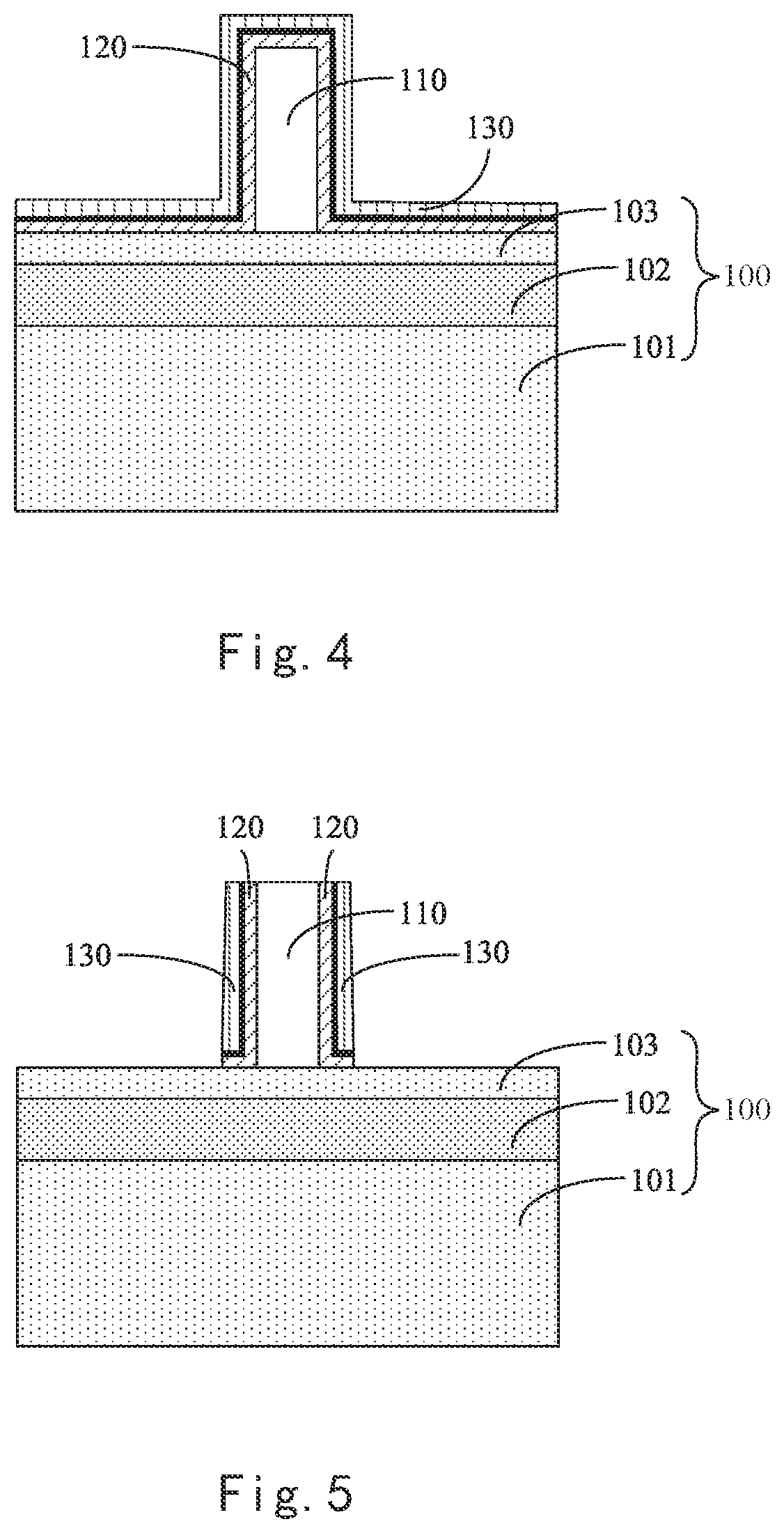

Semiconductor FET and Method for Manufacturing the Same

InactiveUS20130221414A1Decrease overall value of dielectric constantReduce value of parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrical and Electronics engineering

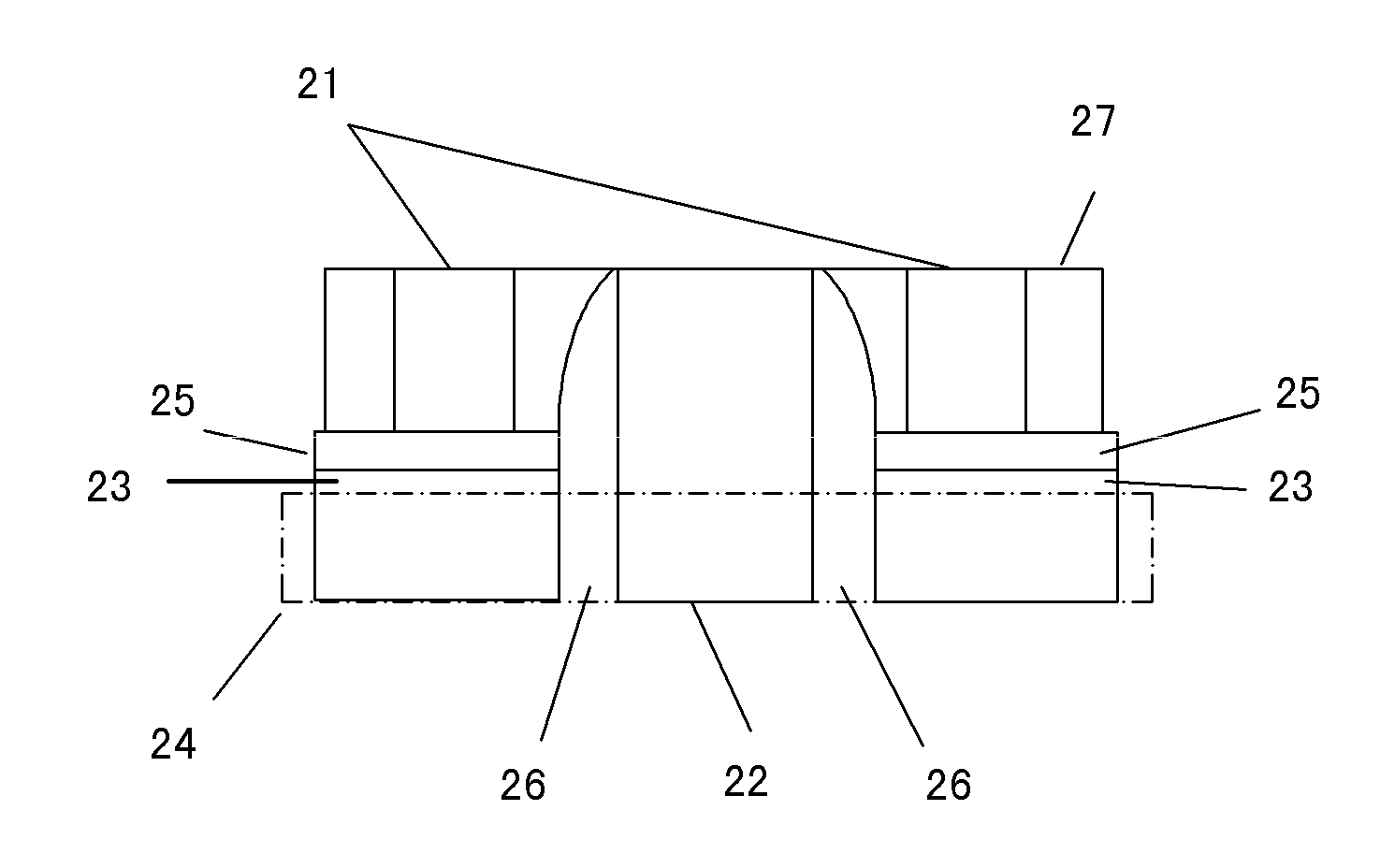

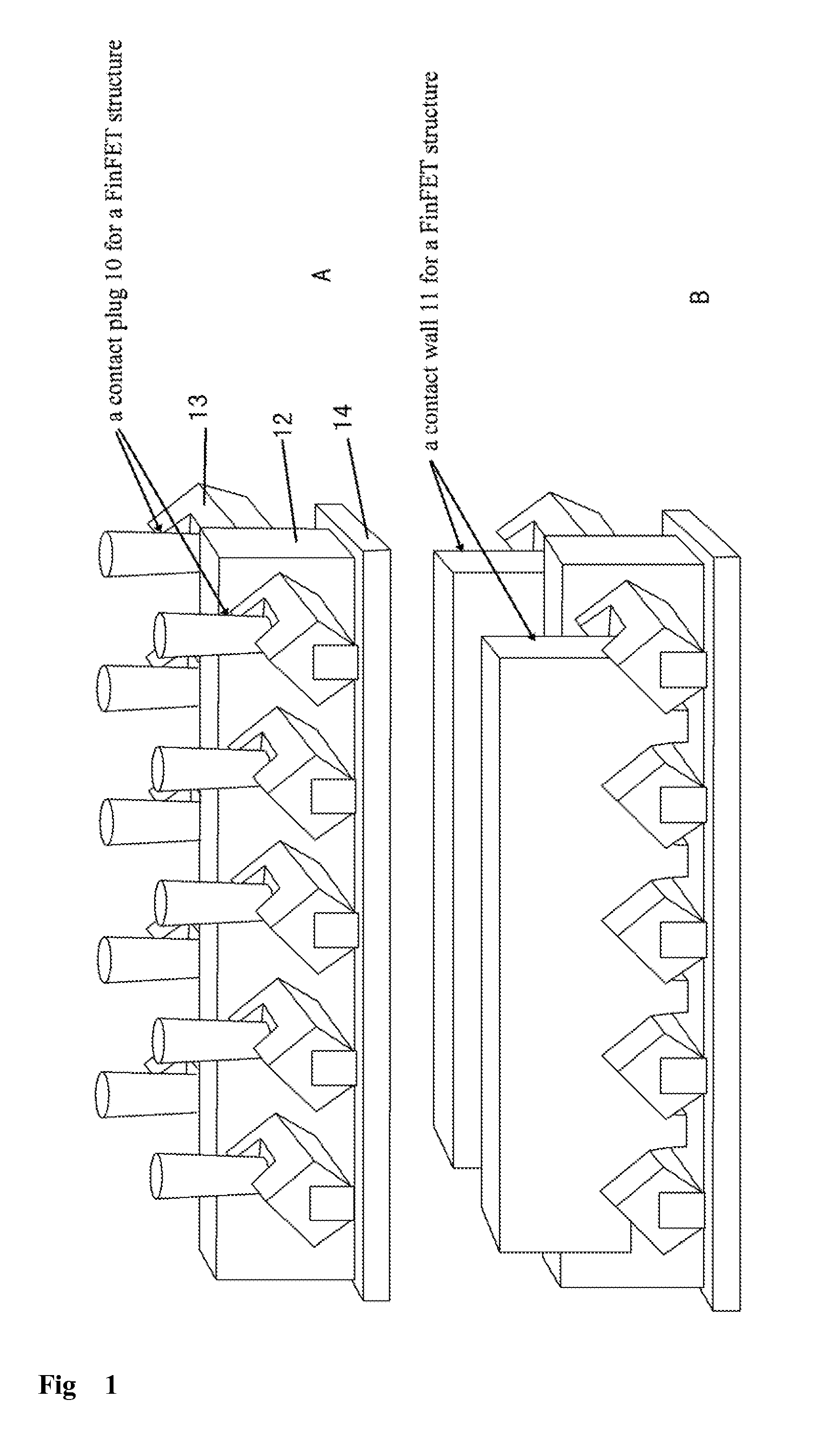

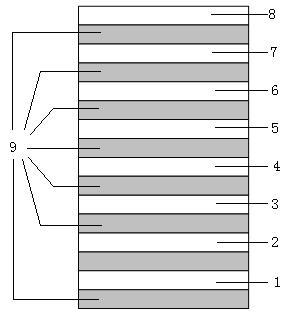

The present invention provides a semiconductor FET and a method for manufacturing the same. The semiconductor FET may comprise: a gate wall; a fin outside the gate wall, both ends of the fin being connected with the source / drain regions on both ends of the fin; and a contact wall on both sides of the gate wall, the contact wall being connected with the source / drain regions via the underlying silicide layer, wherein an airgap is provided around the gate wall. Since an airgap is formed around the gate wall, and particularly the airgap is formed between the gate wall and the contact wall, it is possible to decrease the parasitic capacitance between the gate wall and the contact wall. As a result, the problem of excessive parasitic capacitance resulting from use of the contact wall can be effectively alleviated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

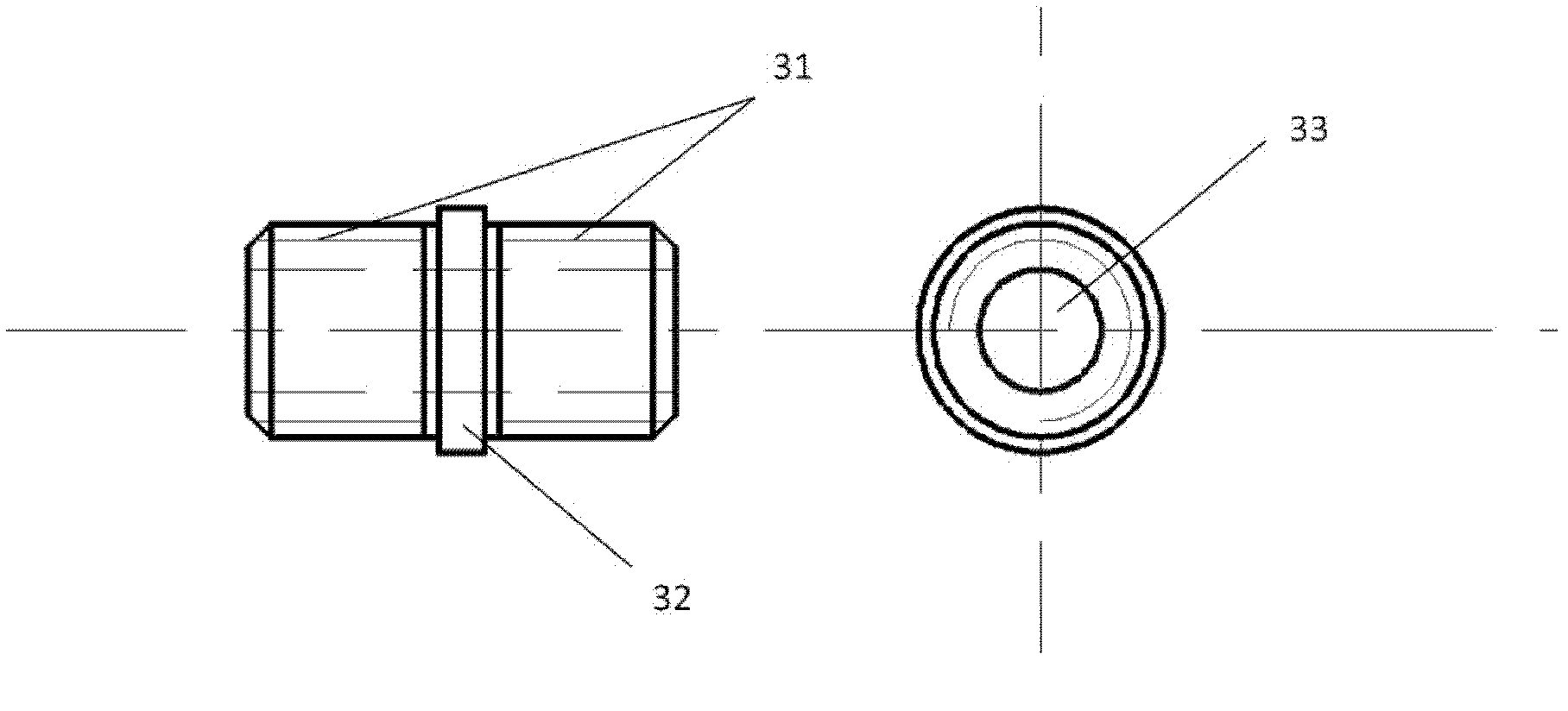

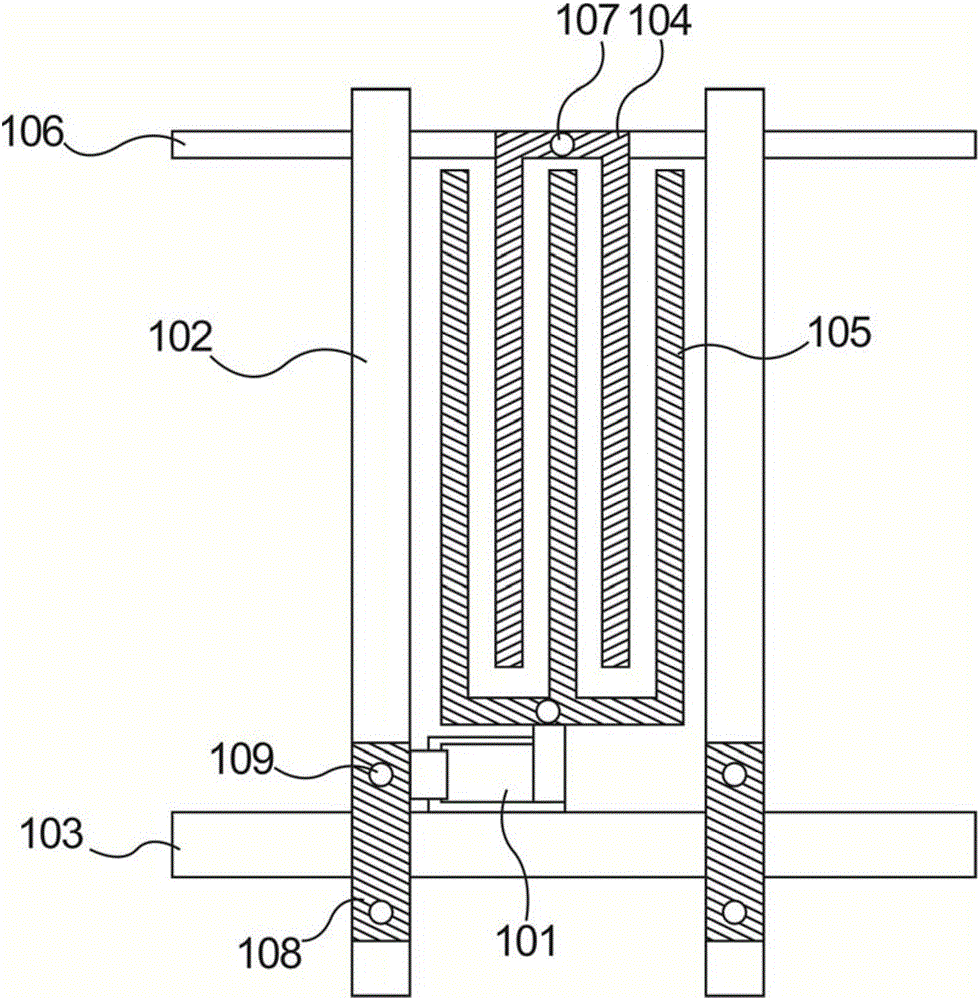

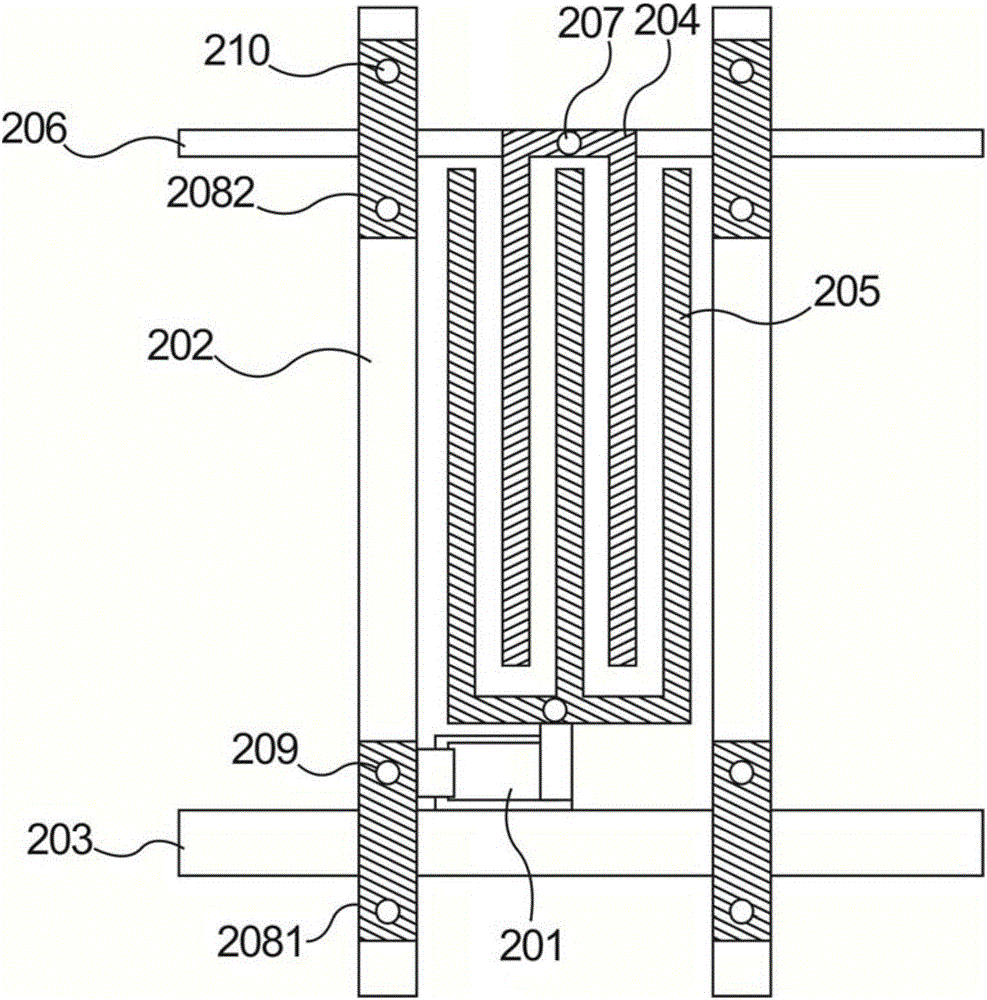

Capacitance sensor

InactiveCN102607668AHigh precisionGuaranteed linearityLevel indicators by physical variable measurementElectricityEngineering

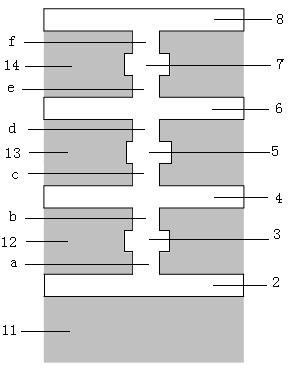

The invention discloses a capacitance sensor, comprising a sensor gauge head, inner electrodes and an outer electrode, wherein the inner electrode is composed of a plurality of independent electrodes; the inner electrodes are the same in inner and outer diameters and are coaxially arrayed; the inner electrodes respectively comprise a top compensation electrode, a multi-section measurement electrode and a bottom compensation electrode from top to bottom; each two sections of electrodes are connected through a connecting piece which is made of an insulating material; the outer electrode is sleeved at the outer parts of the inner electrodes through screw threads, is coaxially mounted with the inner electrodes and is commonly shared by each section of the electrode in the inner electrodes; and the sensor gauge head is connected with the outer electrode. According to the capacitance sensor disclosed by the invention, the influences on liquid level measurement of temperature, pressure, mediums and the like are eliminated and the precision of the liquid level measurement is improved; and furthermore, an electricity leakage phenomenon can be effectively avoided and the linearity of the sensor is guaranteed.

Owner:BEIHANG UNIV

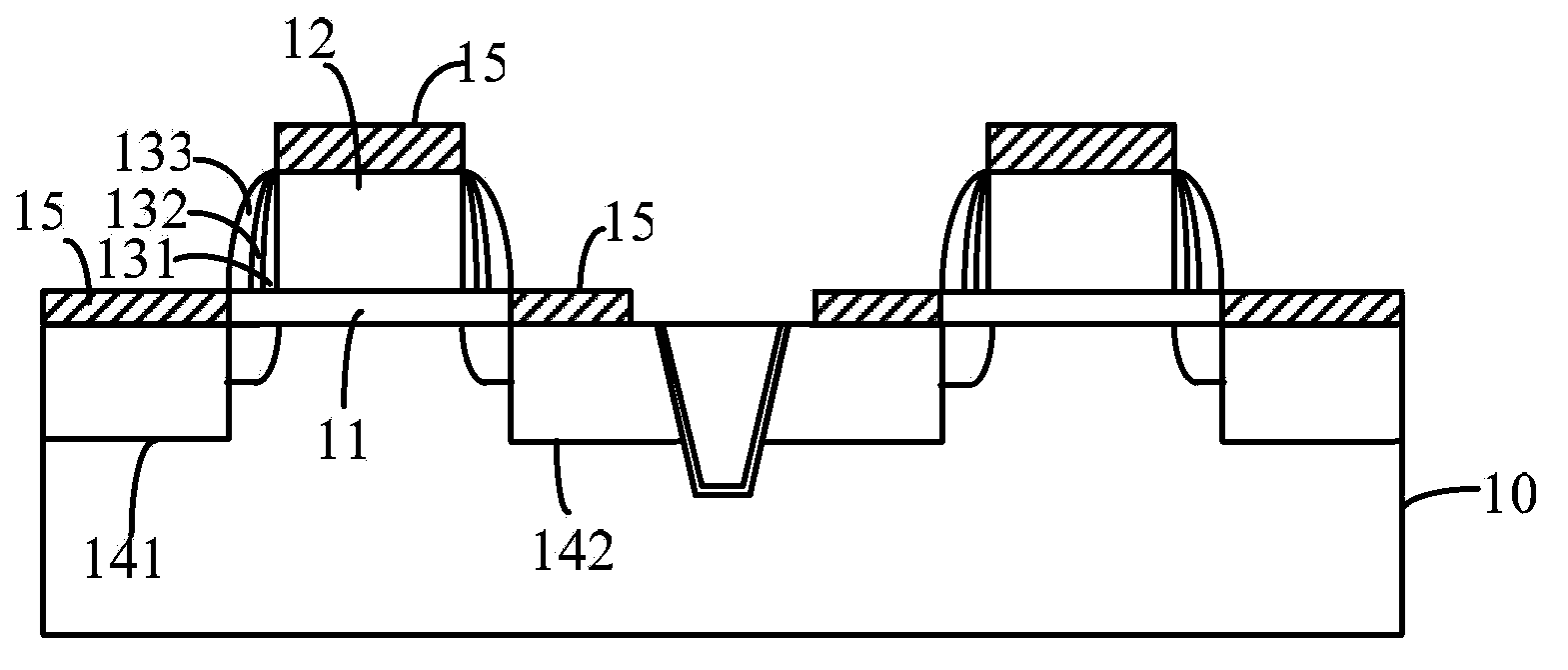

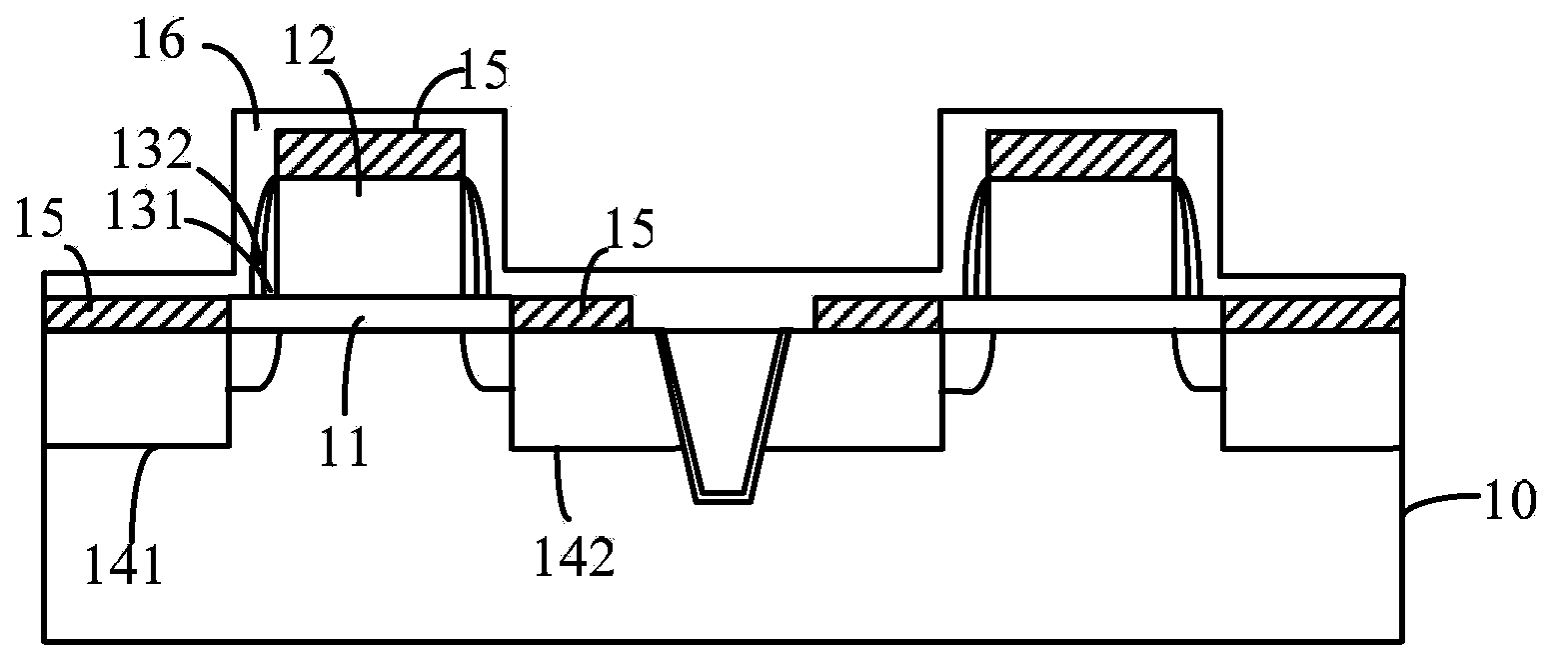

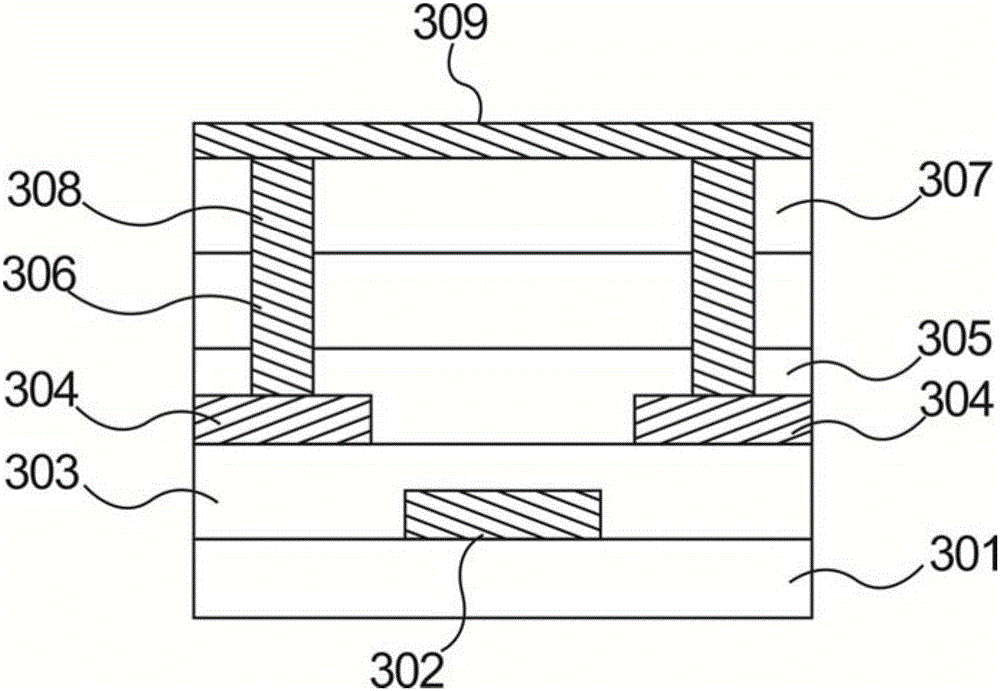

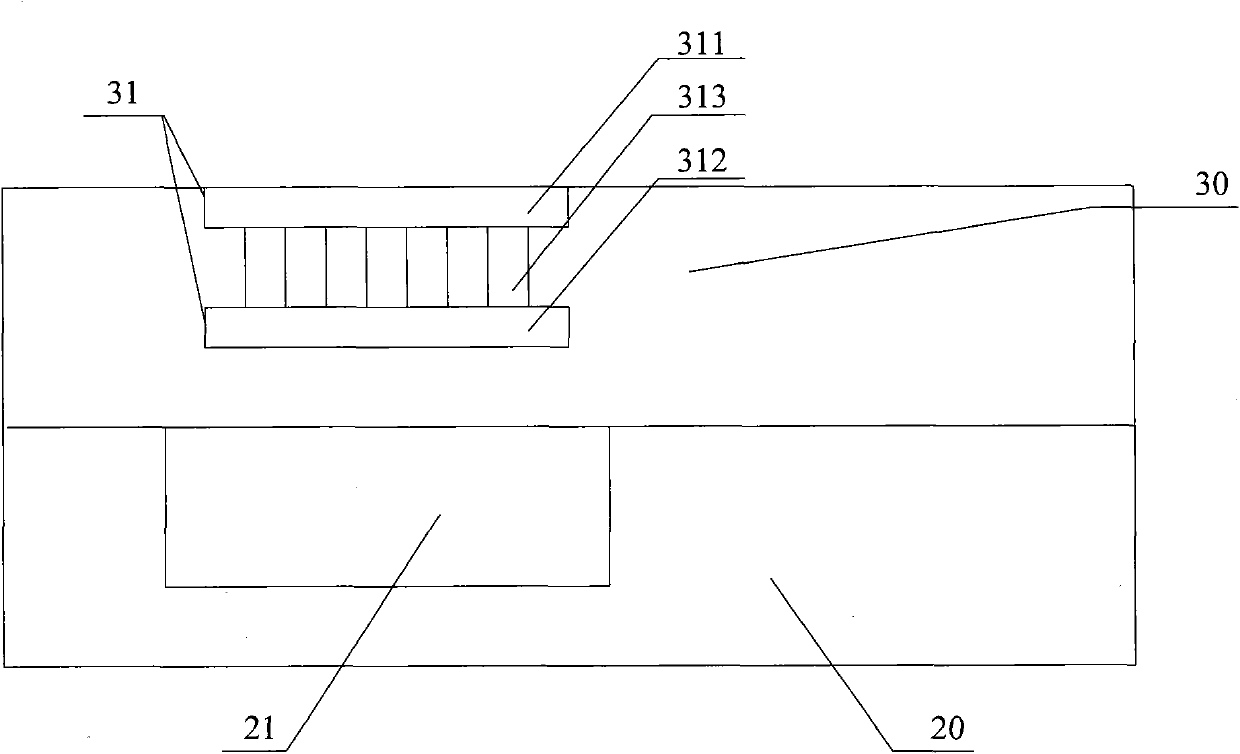

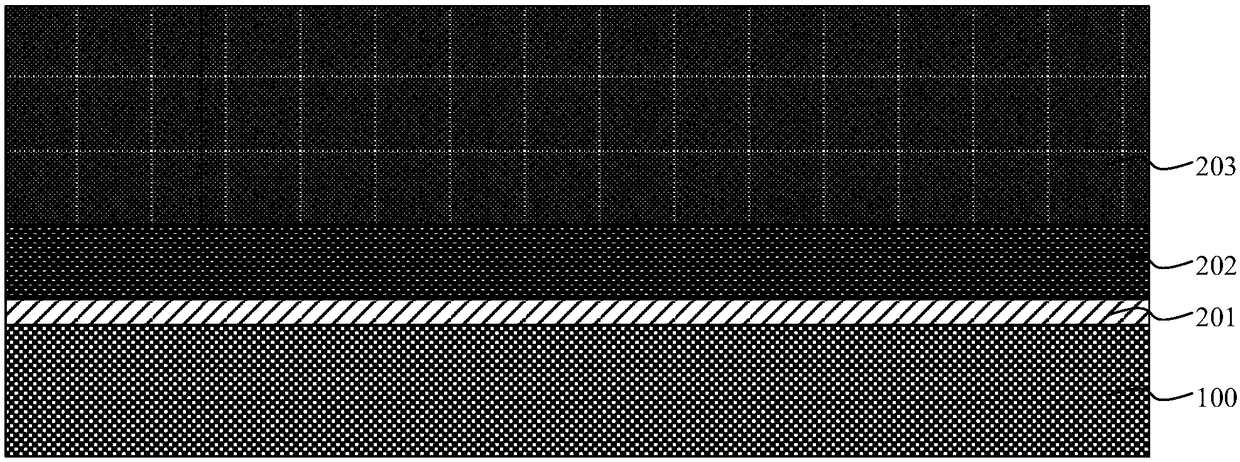

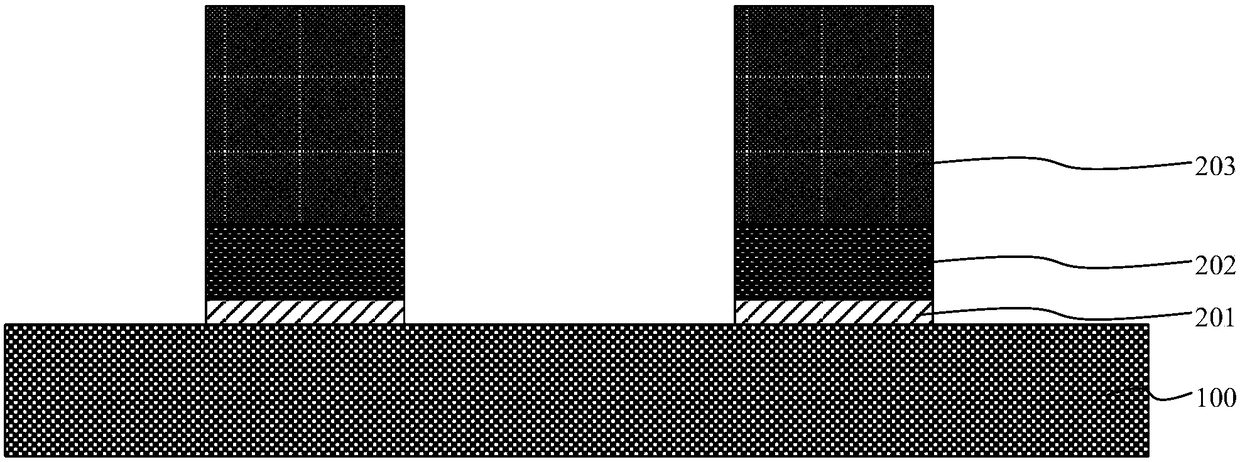

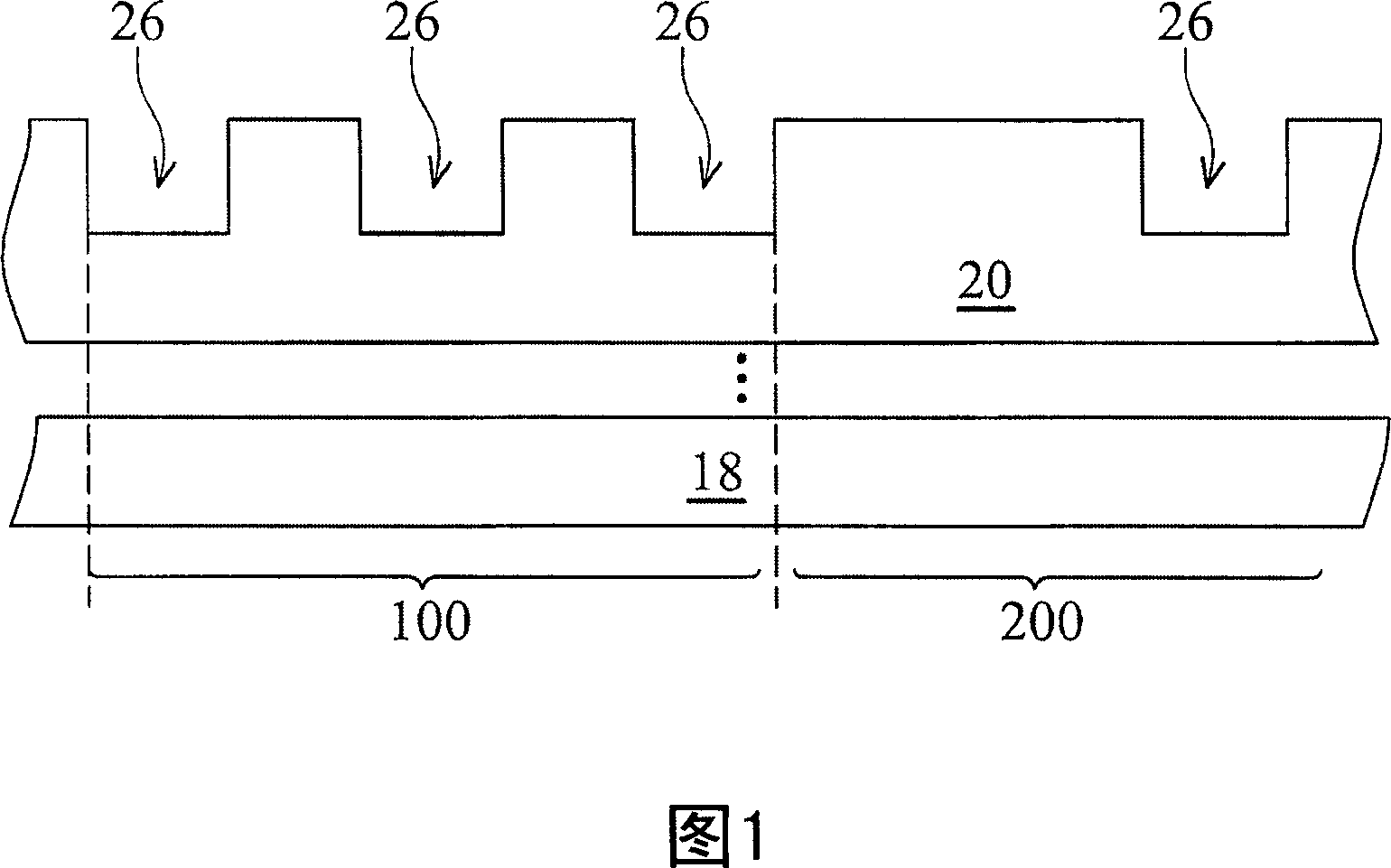

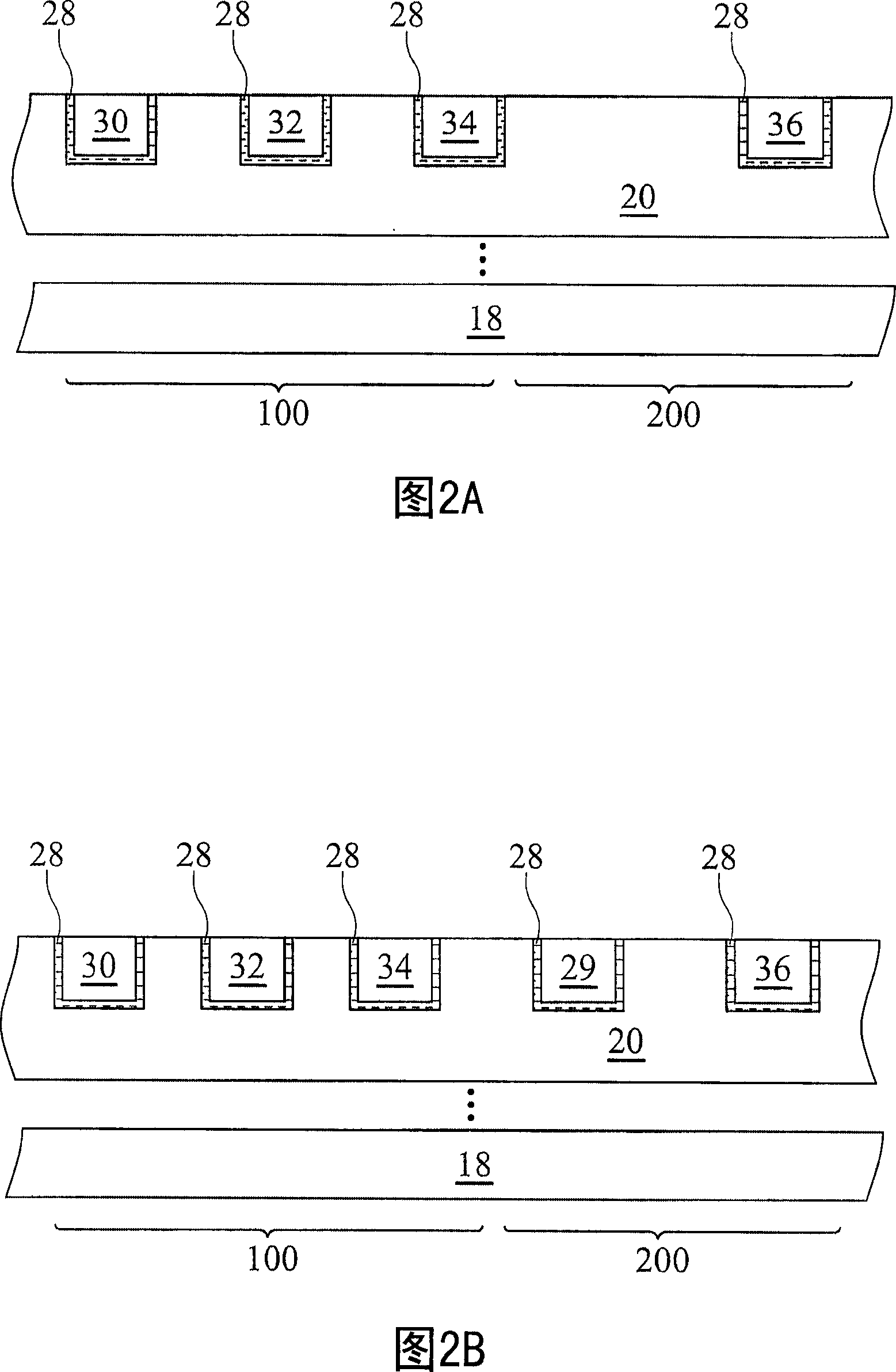

Transistor and forming method thereof

ActiveCN103915341AIncrease the magnitude of the stressLow dielectric constantTransistorSemiconductor/solid-state device manufacturingGate dielectricMetal silicide

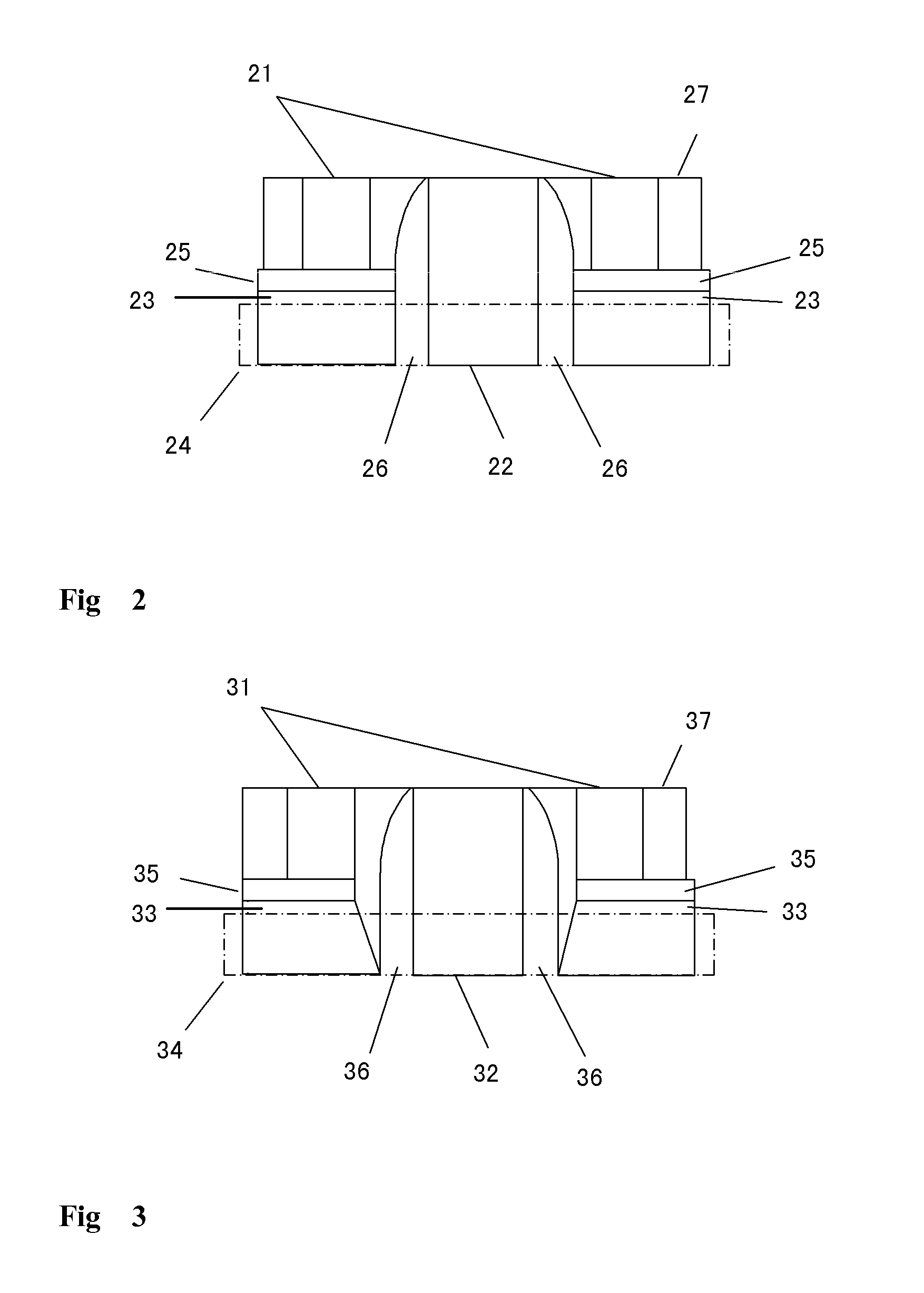

The invention provides a transistor and a forming method of the transistor. The forming method of the transistor comprises the steps that a semiconductor substrate is provided, wherein an isolation structure is arranged in the semiconductor substrate, gate structures are arranged on the surfaces of the portions, on the two sides of the isolation structure, of the semiconductor substrate, and each gate structure comprises a gate dielectric layer on the surface of the semiconductor substrate and a gate electrode located on the surface of the gate dielectric layer; first side walls are formed on the two sides of the gate structure, wherein the first side walls are doped silicon nitride layers; second side walls are formed on the surfaces of the first side walls, and the etching rate of each second side wall is larger than the etching rate of each first side wall; a source electrode and a drain electrode are formed in the portions, located on the two sides of the gate structures, of the semiconductor substrate; metal silicide layers are formed on the surface of the source electrode and on the surface of the drain electrode; the second side walls are eliminated; a stress layer is formed on the surface of the semiconductor substrate. By the adoption of the forming method of the transistor, the stray capacitance on the two sides of the gate structures of the transistor can be reduced, and the stress borne by the trench area of the transistor is increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP

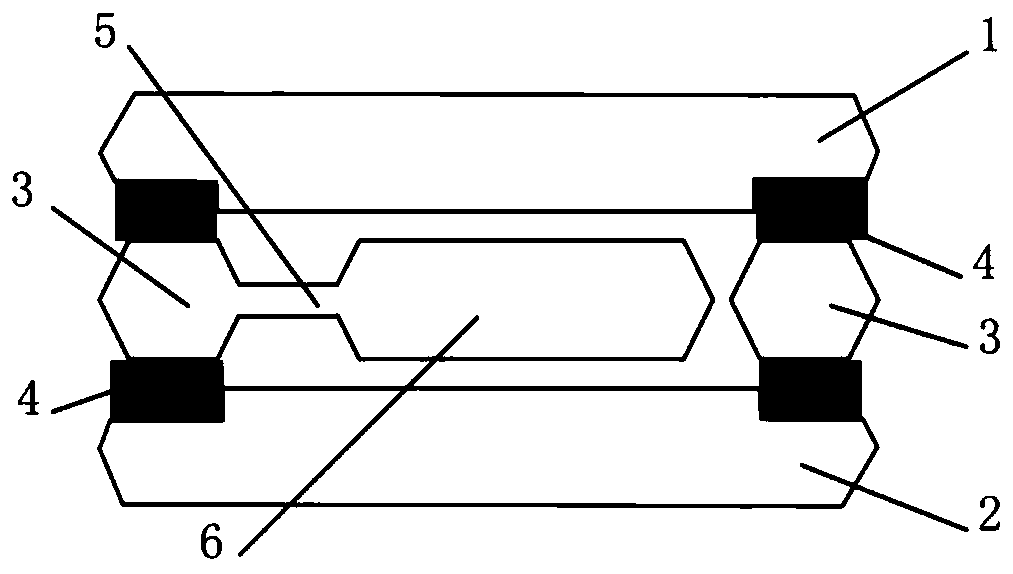

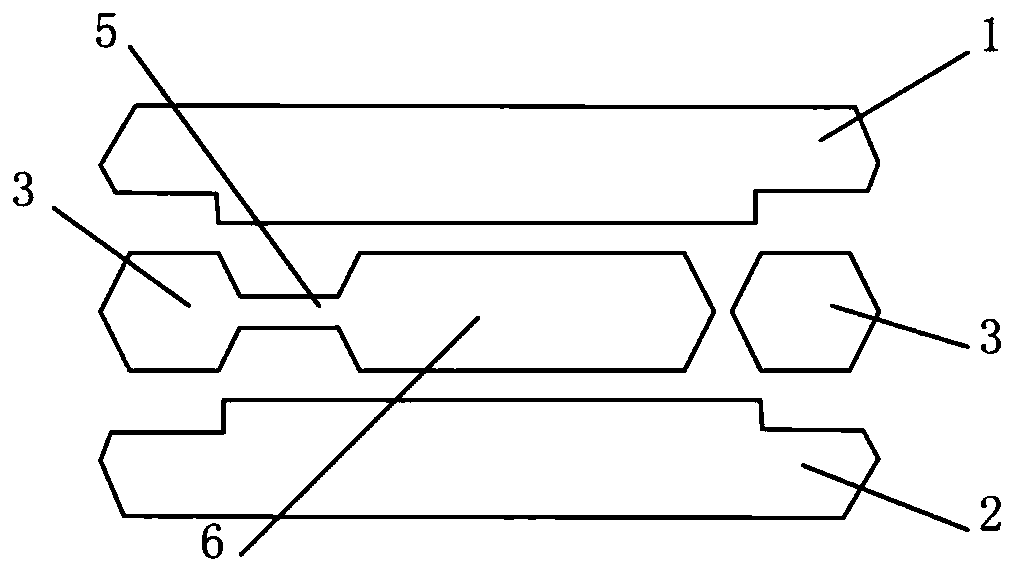

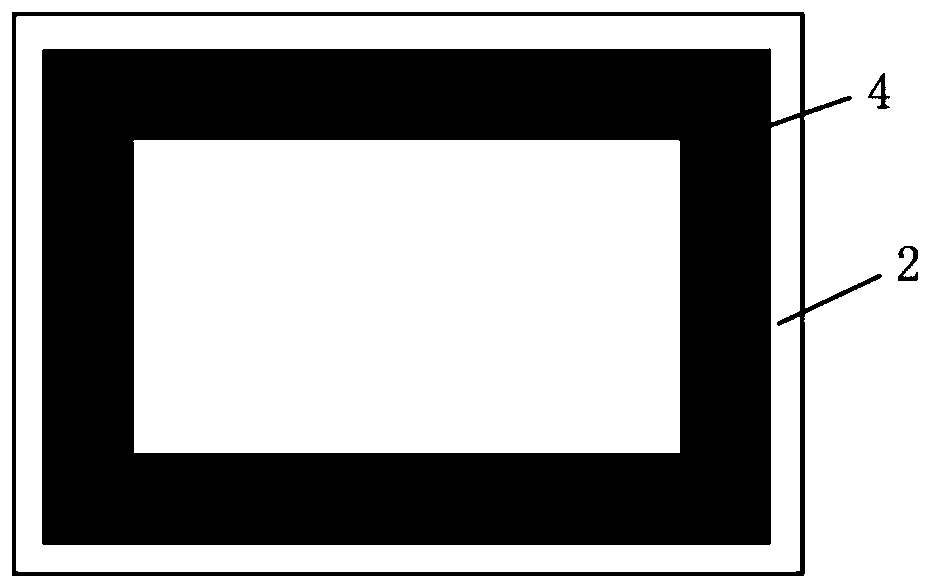

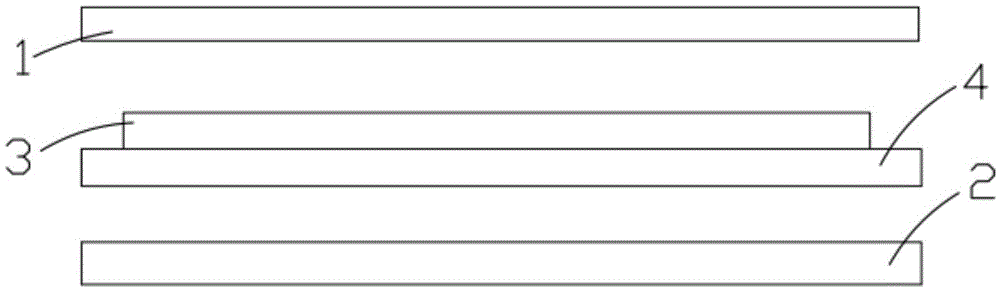

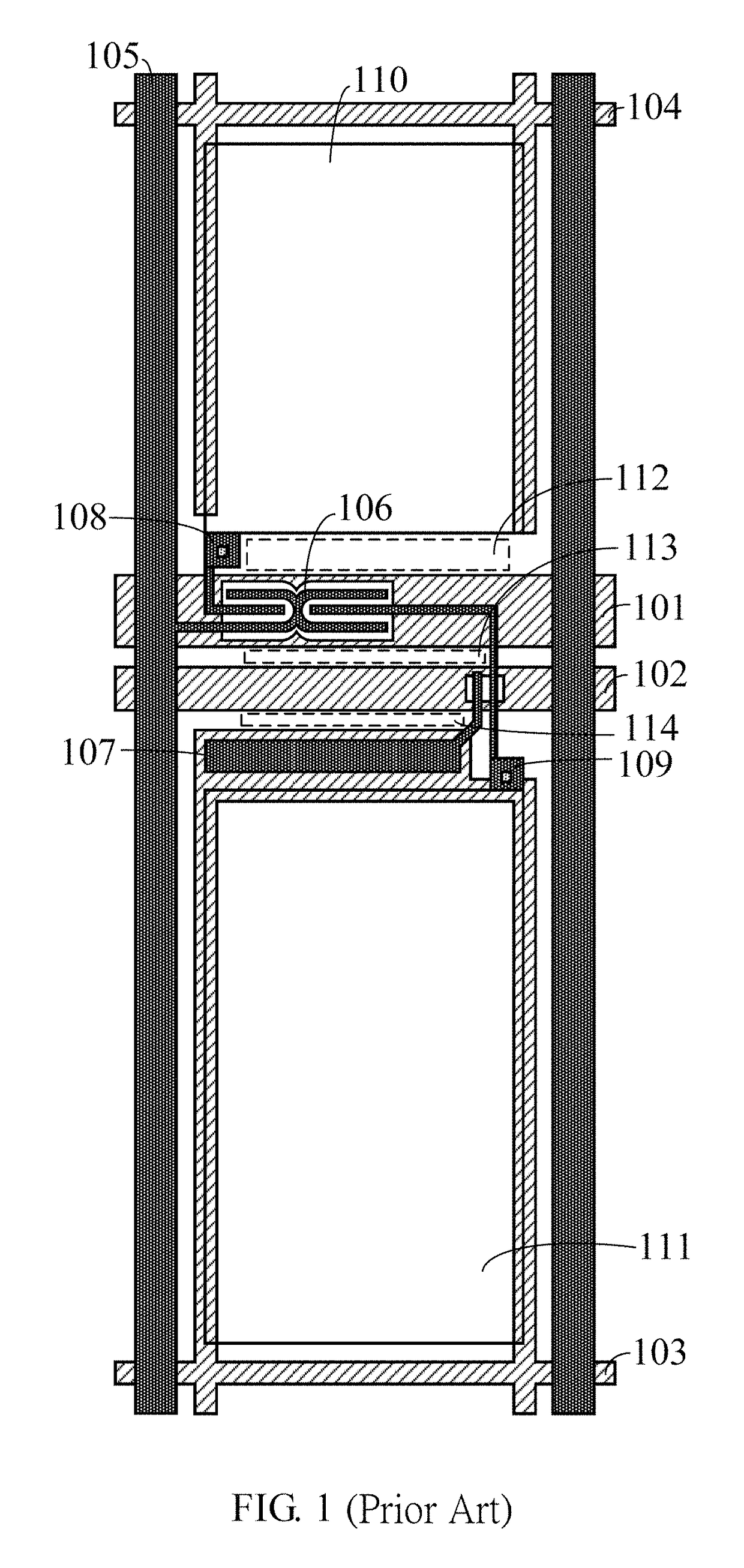

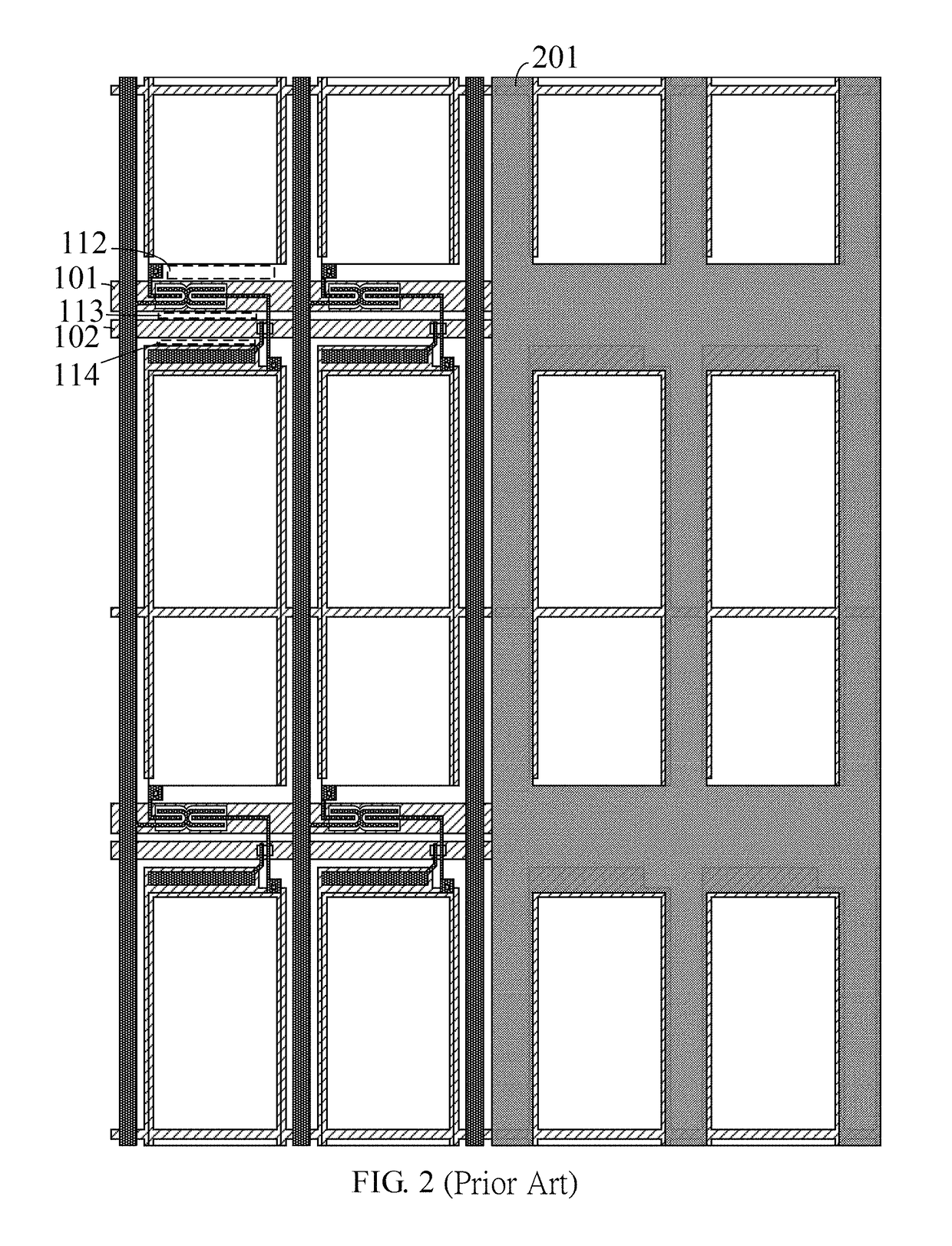

COA (color filter on array) substrate and liquid crystal display panel

ActiveCN106842741AIncreasing the thicknessReduce the value of parasitic capacitanceNon-linear opticsLiquid-crystal displayParasitic capacitance

The invention provides a COA (color filter on array) substrate, comprising a thin-film transistor array, data lines, scanning lines, pixel electrodes and common electrodes; the data lines and the scanning lines interact to define pixel units, the intersections of the data lines above the scanning lines form gaps which cross the scanning lines, two ends of each gap are connected through a jumper, and the jumpers are communicated with the data lines through second via holes. The COA substrate has the advantages that the parts of the data lines overlapping the scanning lines form the gaps, the jumps are added to the top of the substrate to connect the gaps of the data lines, the thickness of the jumpers from the film layer of the scanning lines is increased, parasitic capacitance of overlap portions is reduced, signal delay is decreased, effective charge time of the pixels is extended, and accordingly the display effect of a liquid crystal display panel is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

On-chip integrated inductor

InactiveCN102169868AHigh quality factorIncrease frequency bandwidthSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceIsolation layer

The invention provides an on-chip integrated inductor, comprising inductive coil, metal layer, isolation layer; A metal layer is provide between two adjacent inductive coils; An isolation layer is arranged between the inductive coil and the metal layer; Looking the adjacent two inductive coils in a down direction, The two coils are offset to each other and not superposed; The inductive coil and the metal layer are connected through perforations. The invention provided on-chip inductors reduces parasitic capacitance between perforation wires, Which improving quality factors, And expanding frequency bandwidth of inductance, Without increasing the chip area.

Owner:EAST CHINA NORMAL UNIVERSITY +1

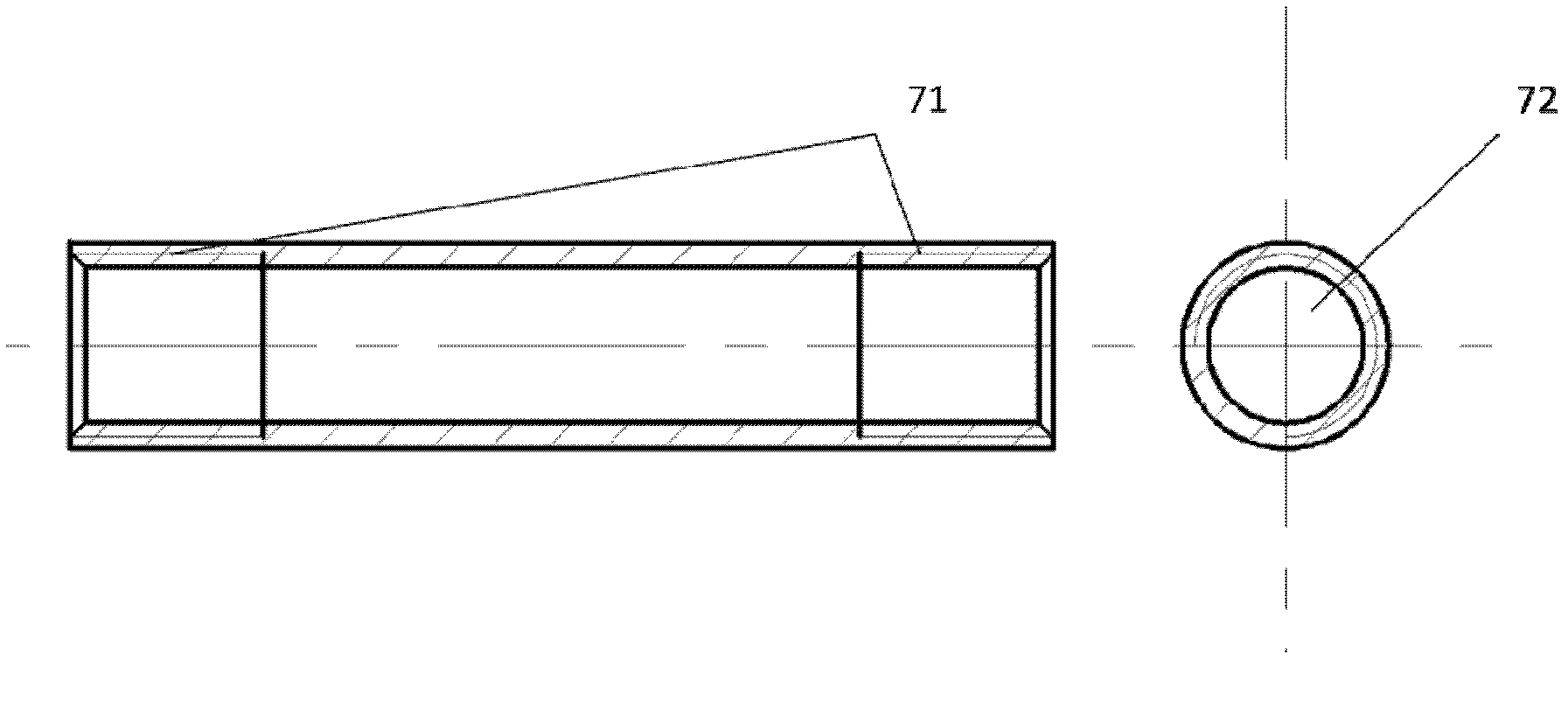

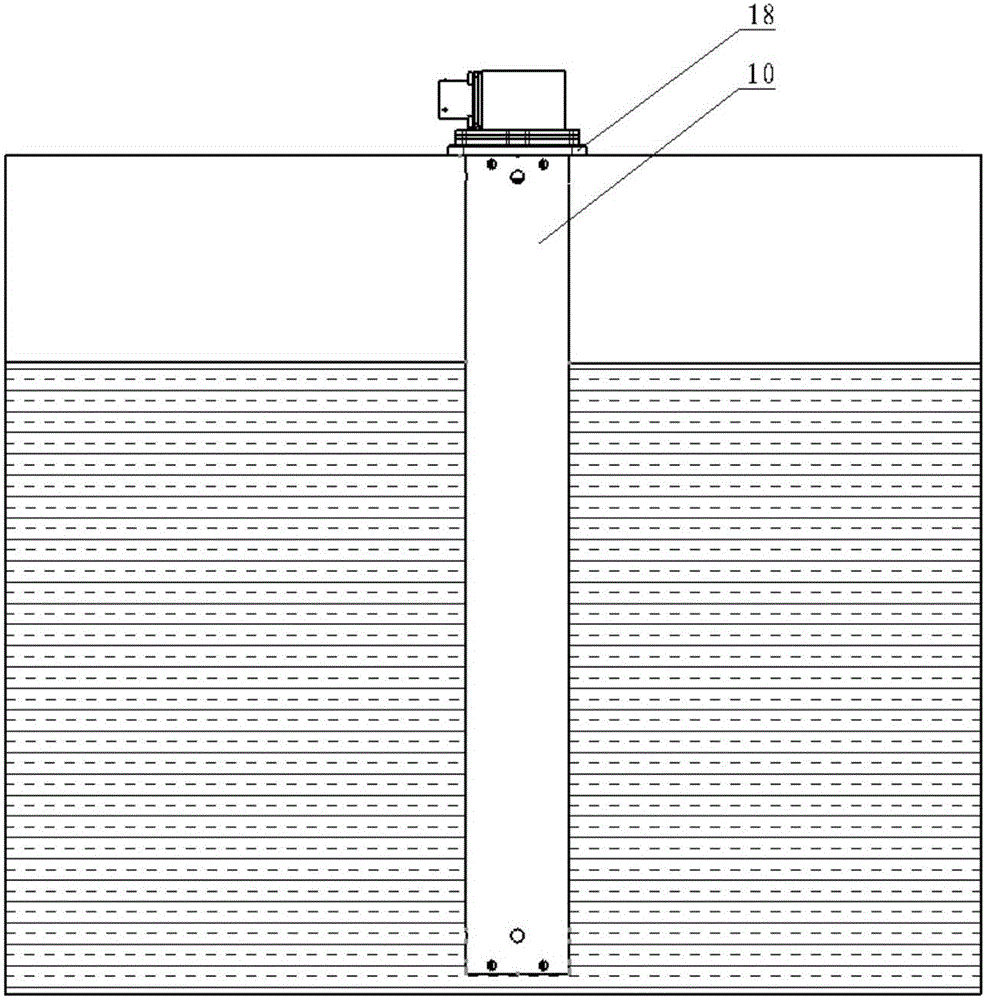

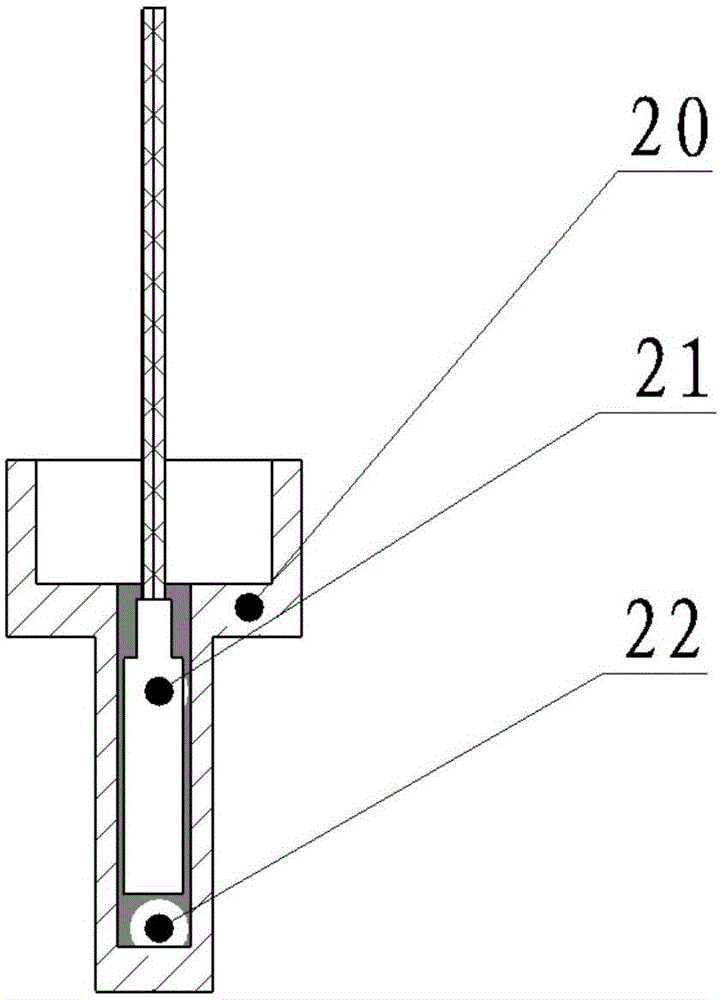

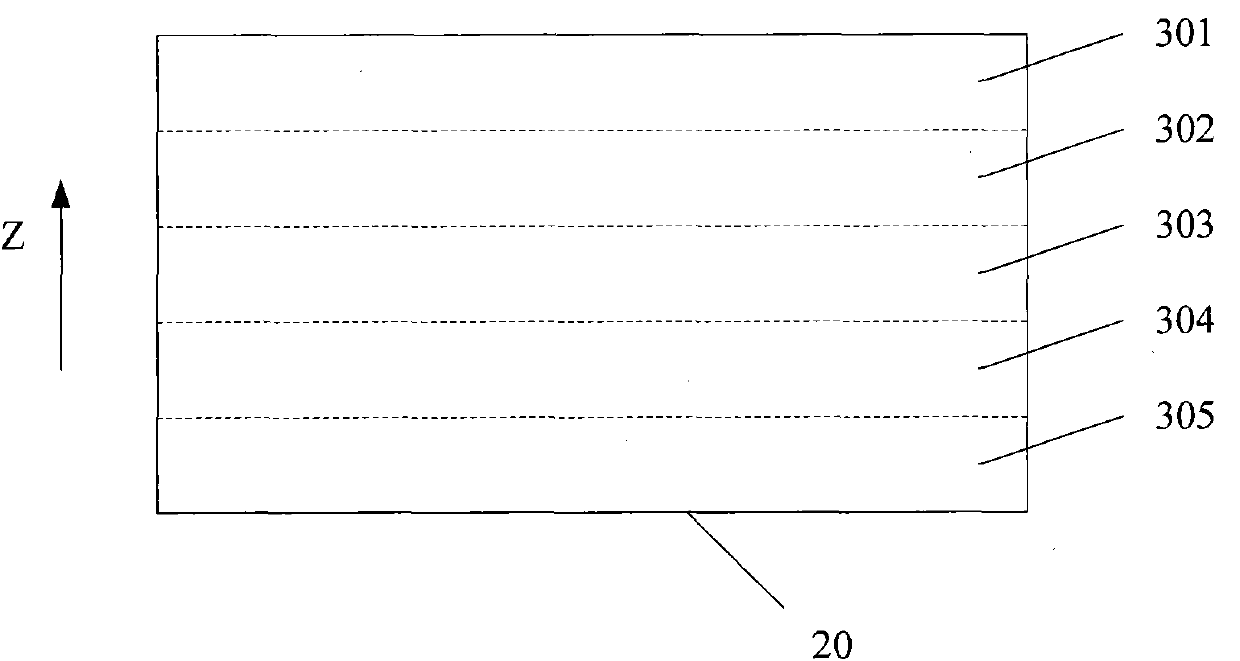

Capacitance type temperature compensation oil level measurement sensor

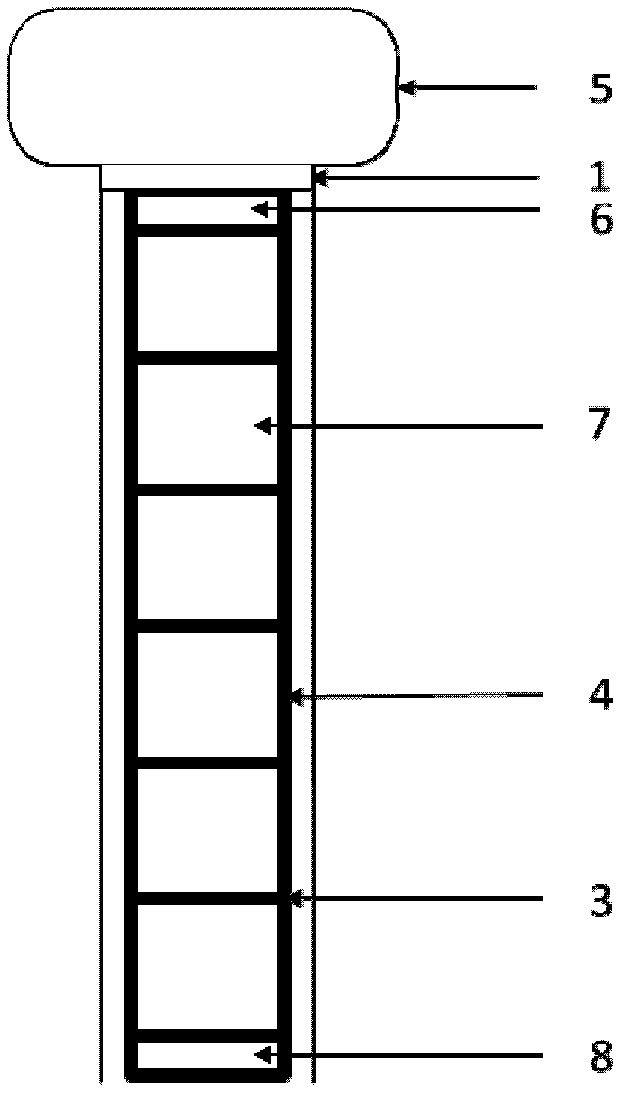

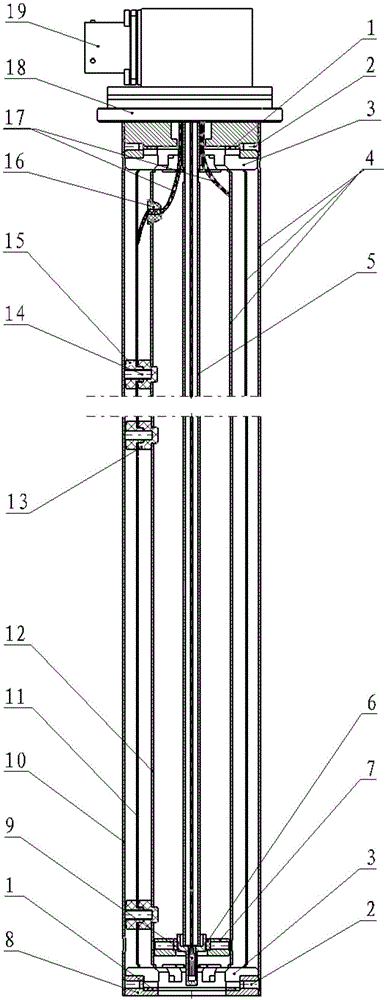

ActiveCN106225876AHigh concentric positioning accuracyHigh positioning accuracyTesting/calibration apparatusInternal combustion piston enginesLiquid mediumElectrical conductor

The invention discloses a capacitance type temperature compensation oil level measurement sensor which has high positioning accuracy and can achieve the effects of reducing the parasitic capacitance in the dry capacitance and compensating for the fuel oil level measuring errors caused by temperature variation. The capacitance type temperature compensation oil level measurement sensor is characterized in that an oil level measurement module comprises three coaxial metal tubes; the oil level and the oil mass are obtained depending on variation of liquid media in the tubes; the oil level signal capacitance C in proportion to the oil immersion height is output; a temperature compensation module is fixed at the bottom ends of the metal tubes via a conductor tray and a guide rod, is formed by a temperature sensing module assembled in a protective cover tube, automatically corrects errors caused by temperature difference via the guide rod in the tubes, outputs resistance R and capacitance C of the oil level measurement module, converts the resistance R and the capacitance C to current signals IC and IR forming proportional relations with the capacitance C and the resistance R and transmits the current signals IC and IR to a fuel measurement control system via a socket connected with shielded conductors.

Owner:四川泛华航空仪表电器有限公司

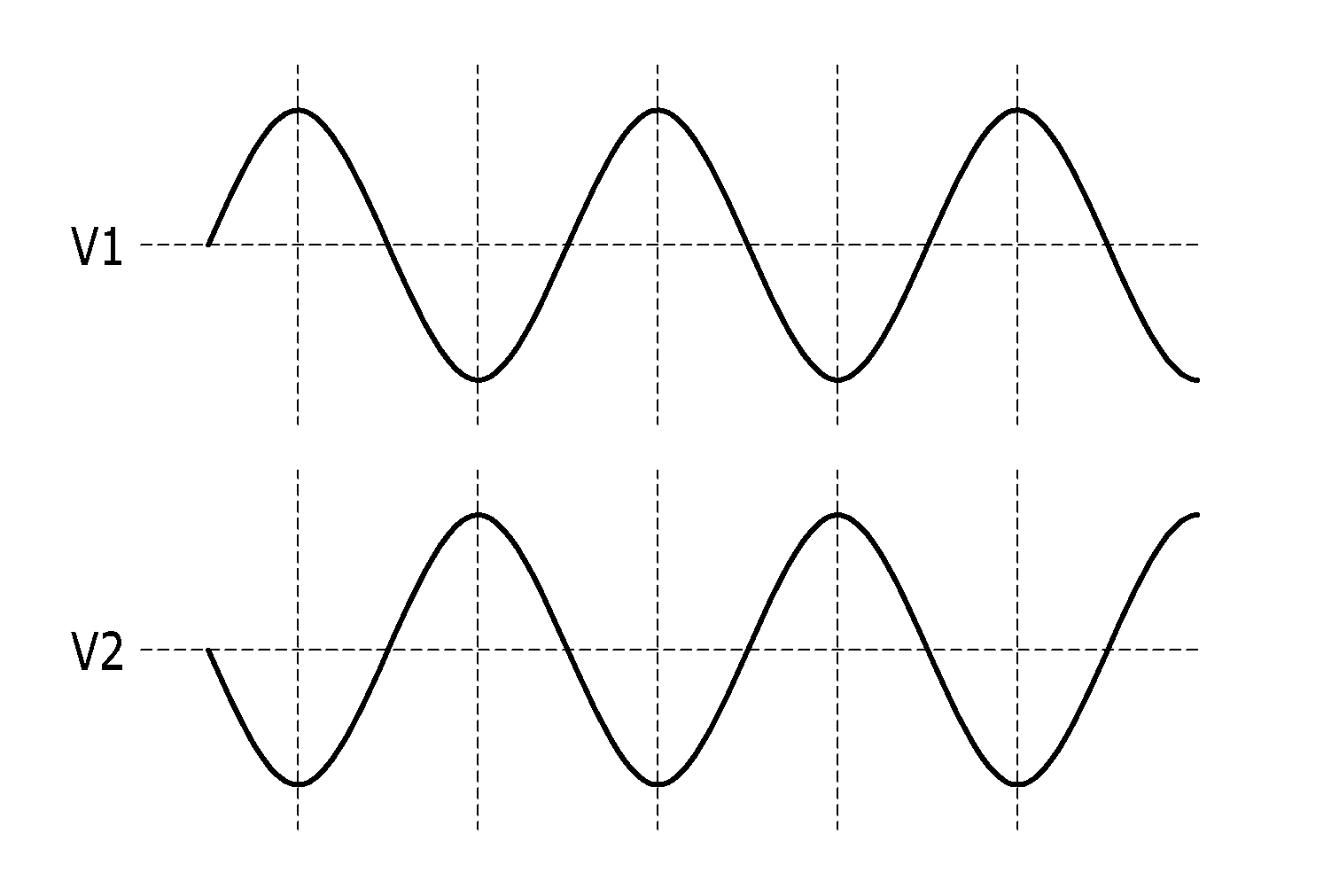

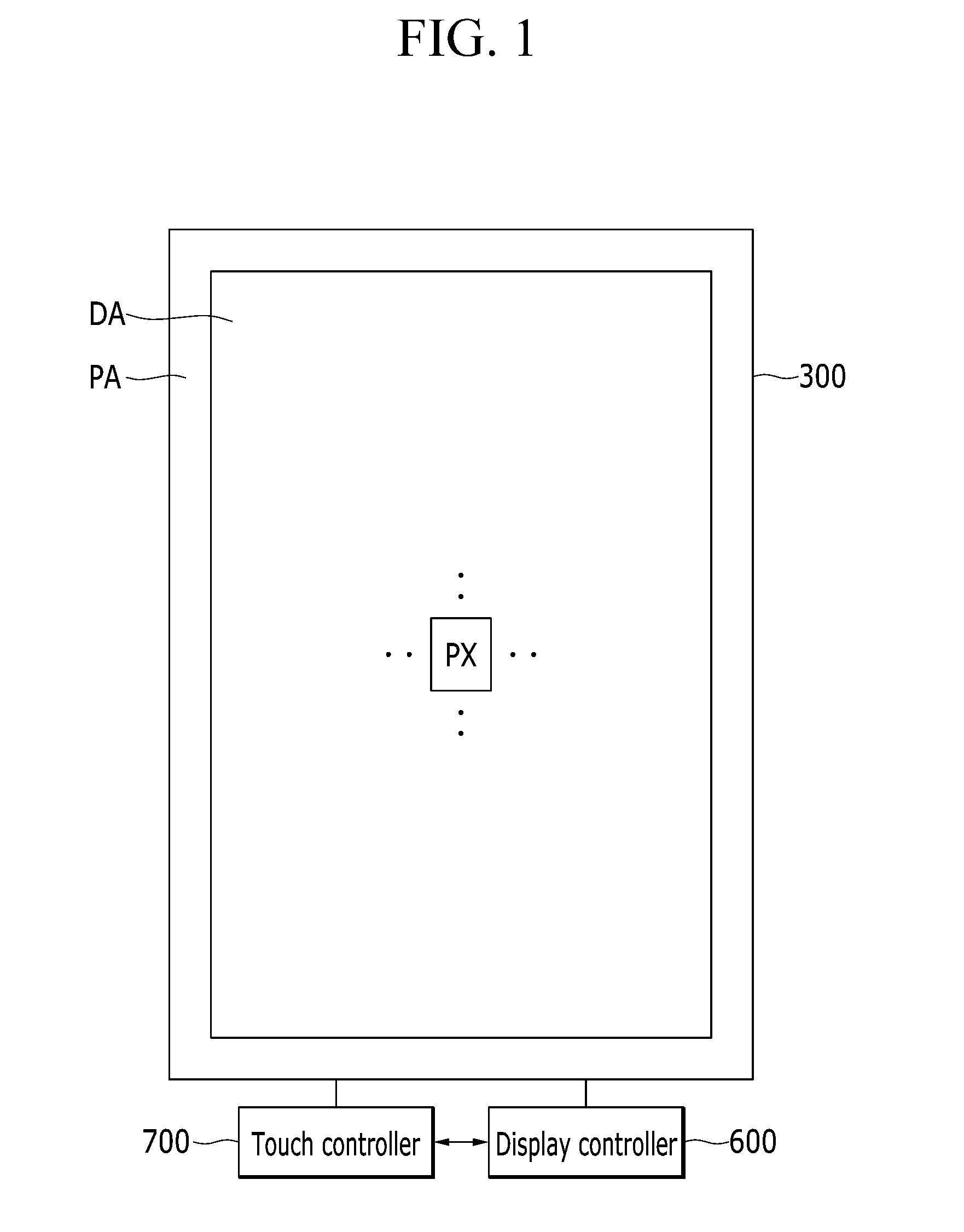

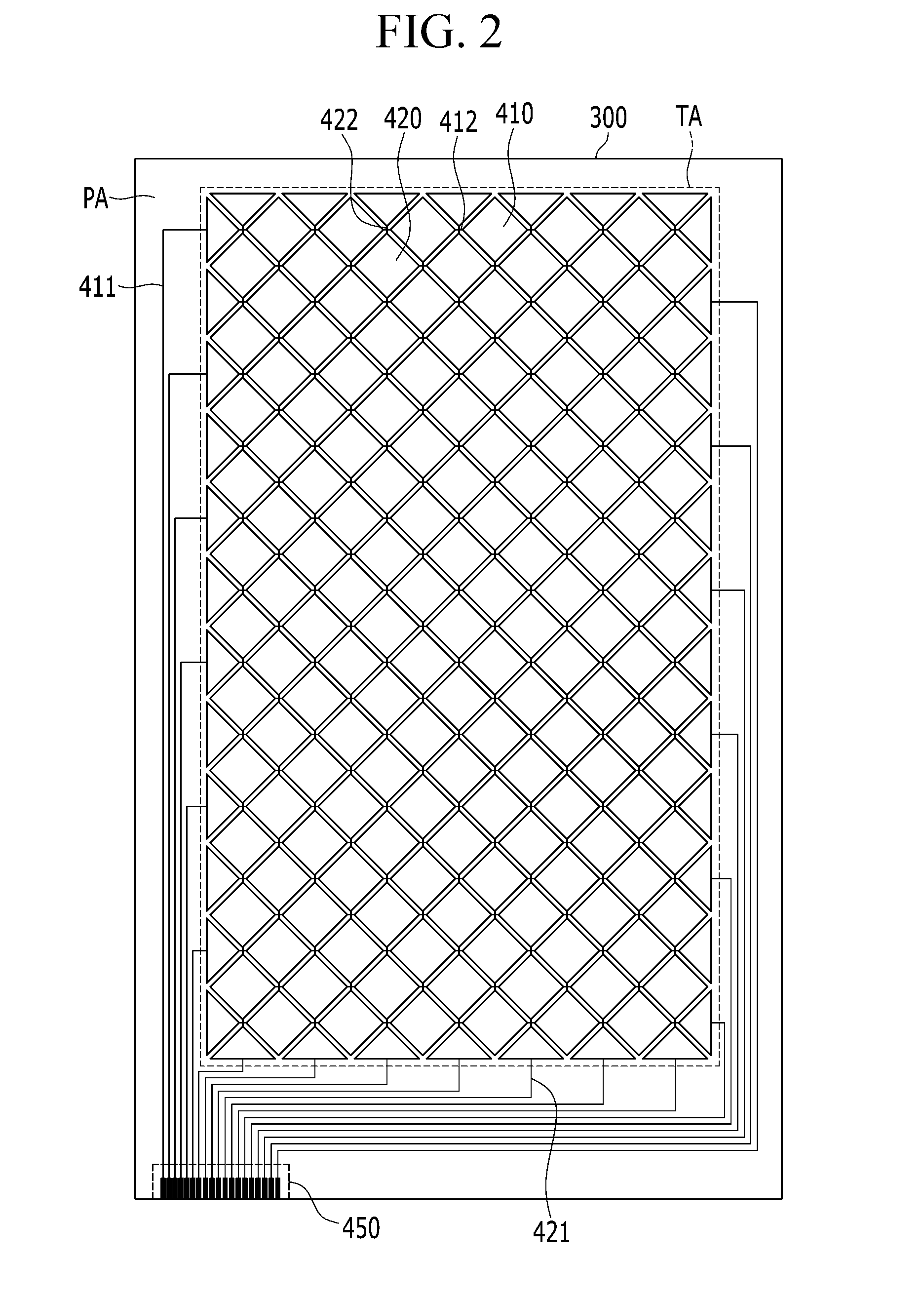

Touch screen panel, display device including the same, and driving method thereof

InactiveUS20160299597A1Reduce parasitic capacitanceReduce the value of parasitic capacitanceInput/output processes for data processingTouch SensesDisplay device

A display device including a display panel configured to display an image, a touch sensing layer disposed above the display panel and the touch sensing layer including a touch substrate, a touch electrode disposed on the touch substrate, and a common touch electrode disposed under the touch substrate, a first driver configured to apply a sensing input voltage having a first phase to the touch electrode, and a second driver configured to apply a common input voltage having a second phase to the common touch electrode. The second phase of the common input voltage is different from the first phase the sensing input voltage.

Owner:SAMSUNG DISPLAY CO LTD

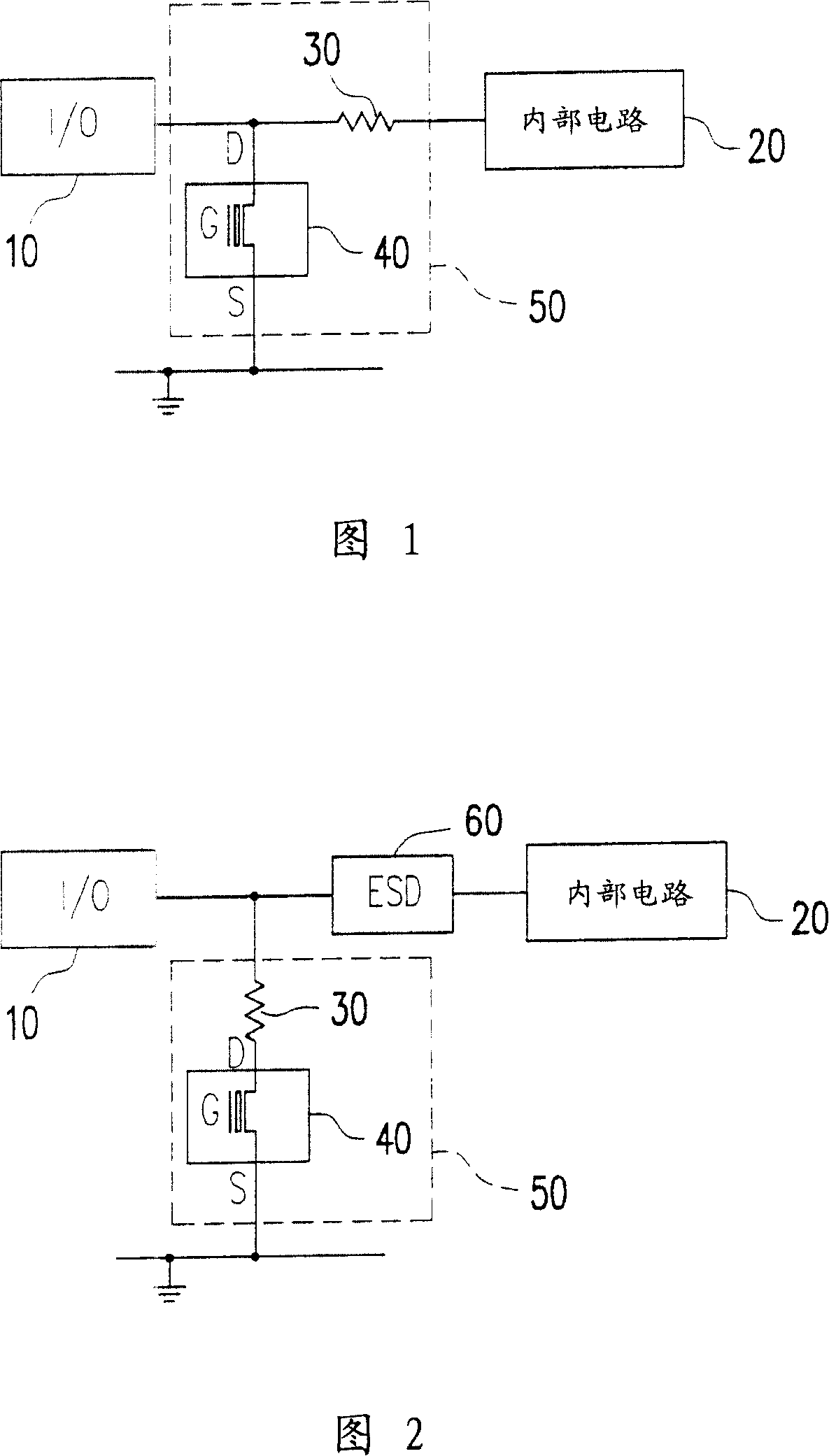

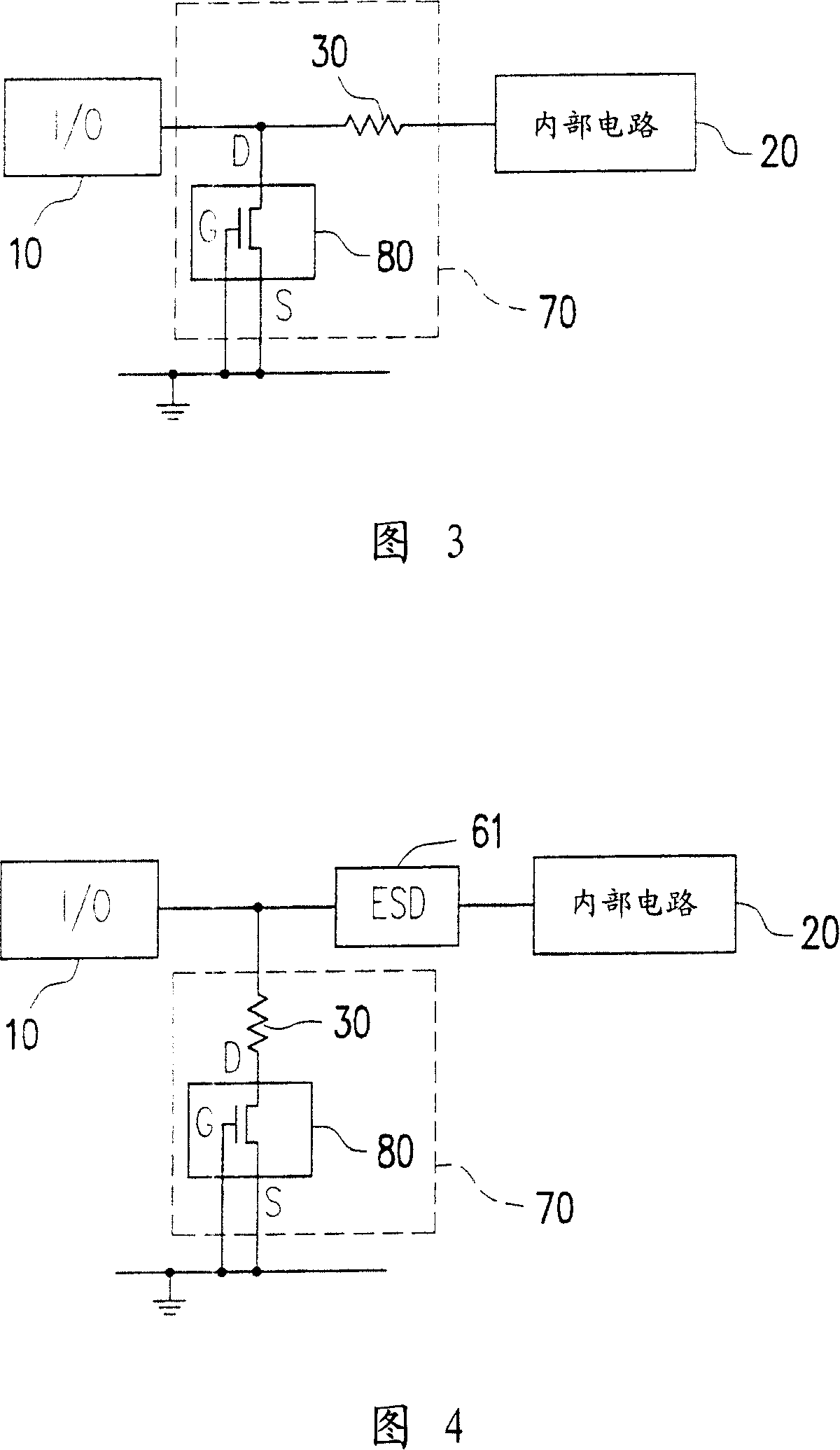

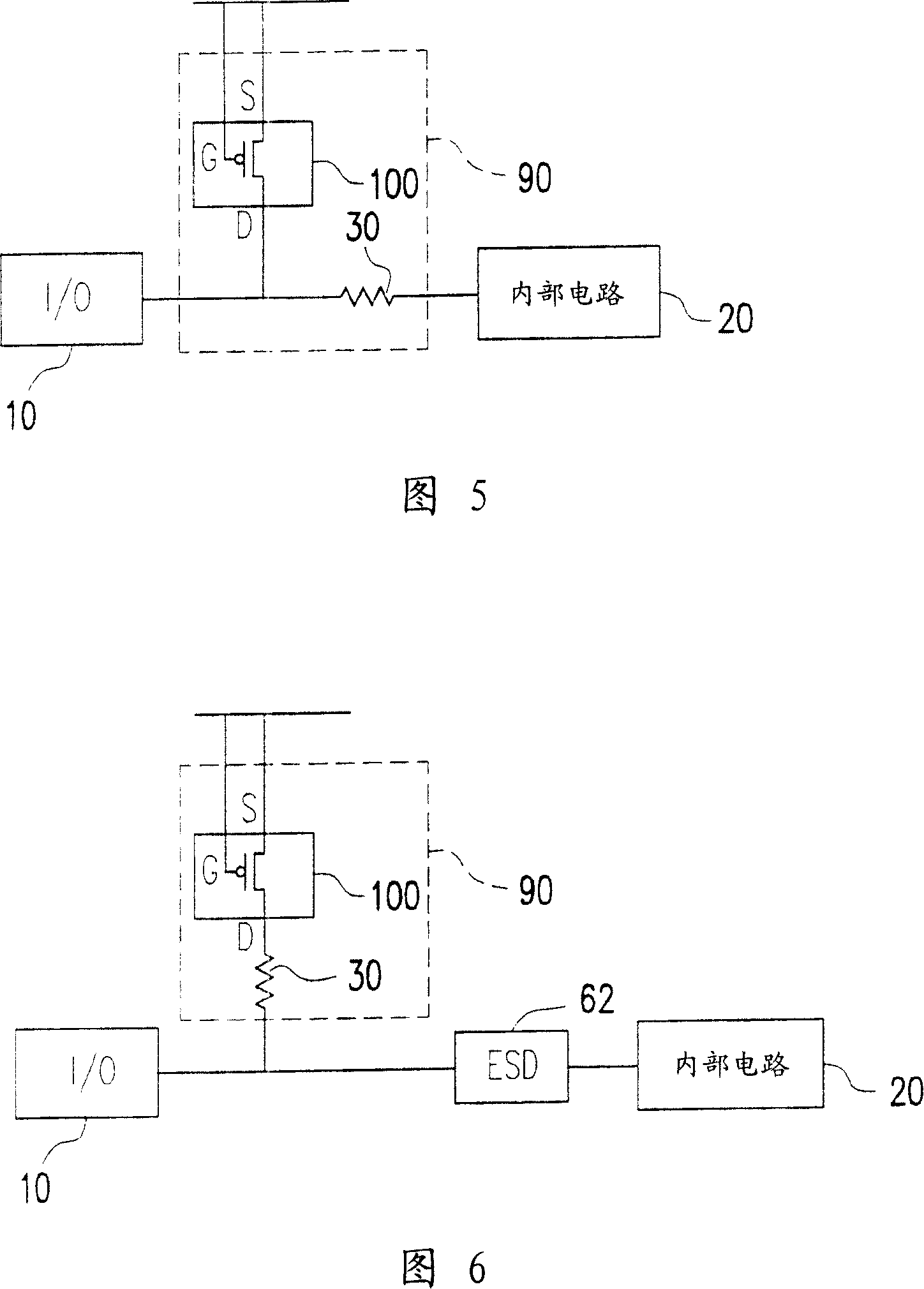

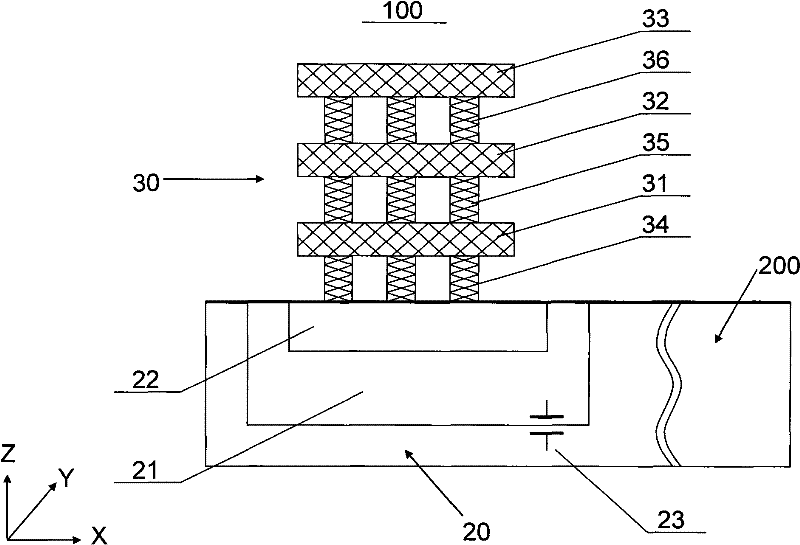

Electrostatic discharge protecter and its producing method

InactiveCN1481022AImprove performanceReduce the value of parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrostatic discharge protection

The method includes following steps: providing a substrate, forming a trap area; a doping area is formed in the trap area, and a grid electrode is formed above the grid electrode; a source electrode area and a drain electrode area adjacent to the doping area are formed in the trap on two sides of the grid electrode.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

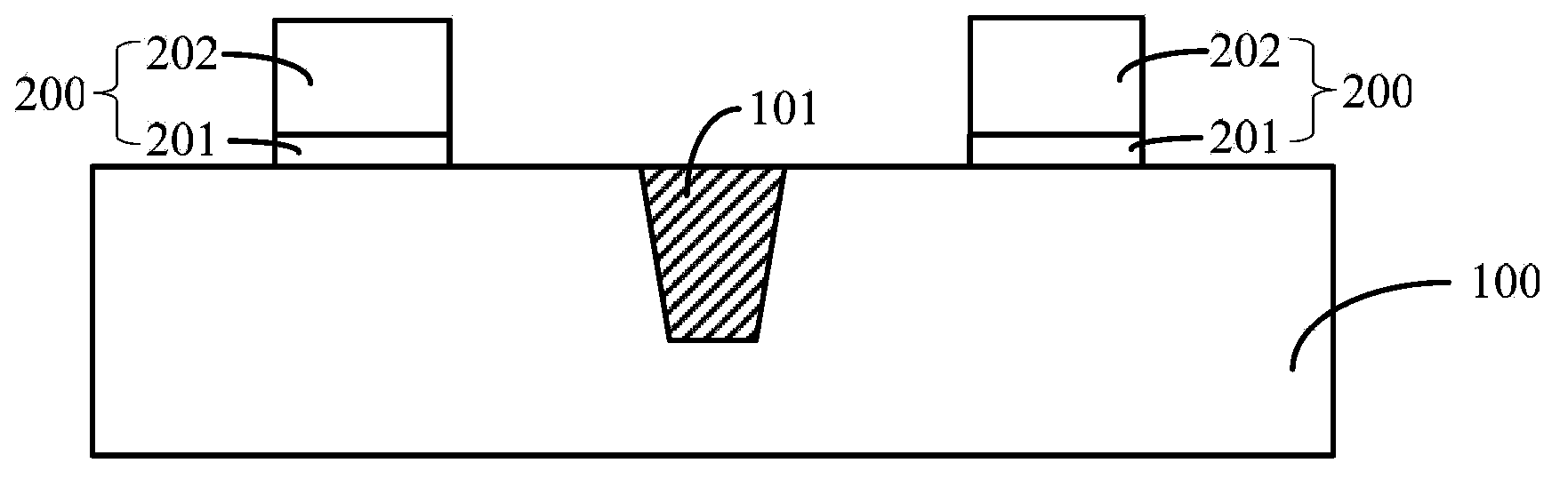

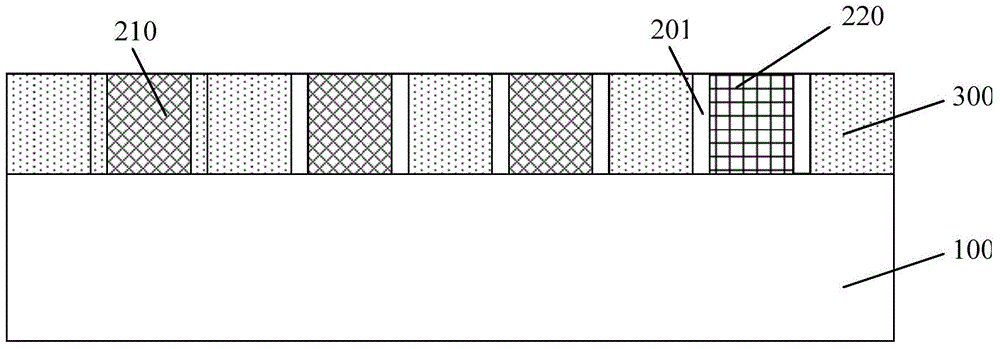

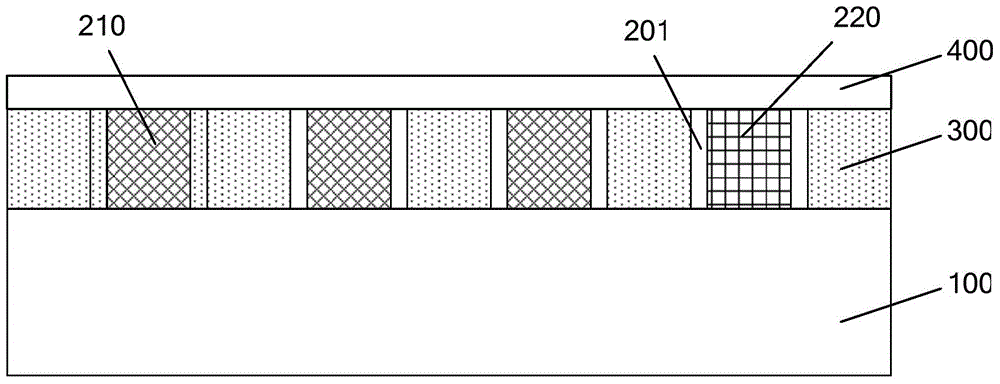

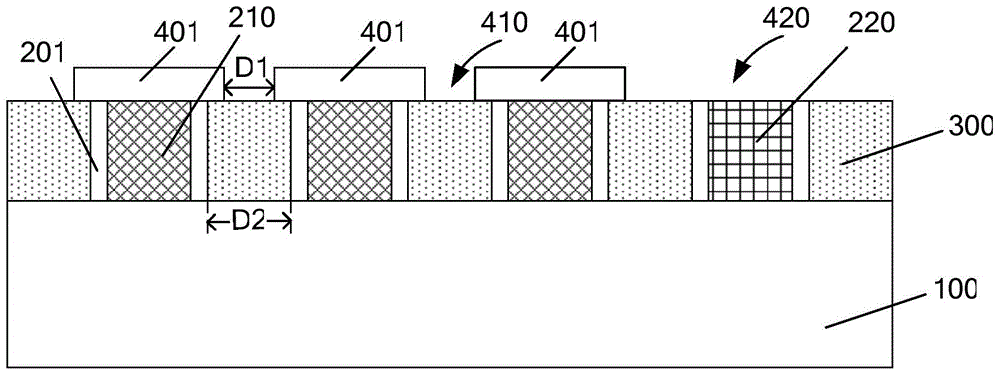

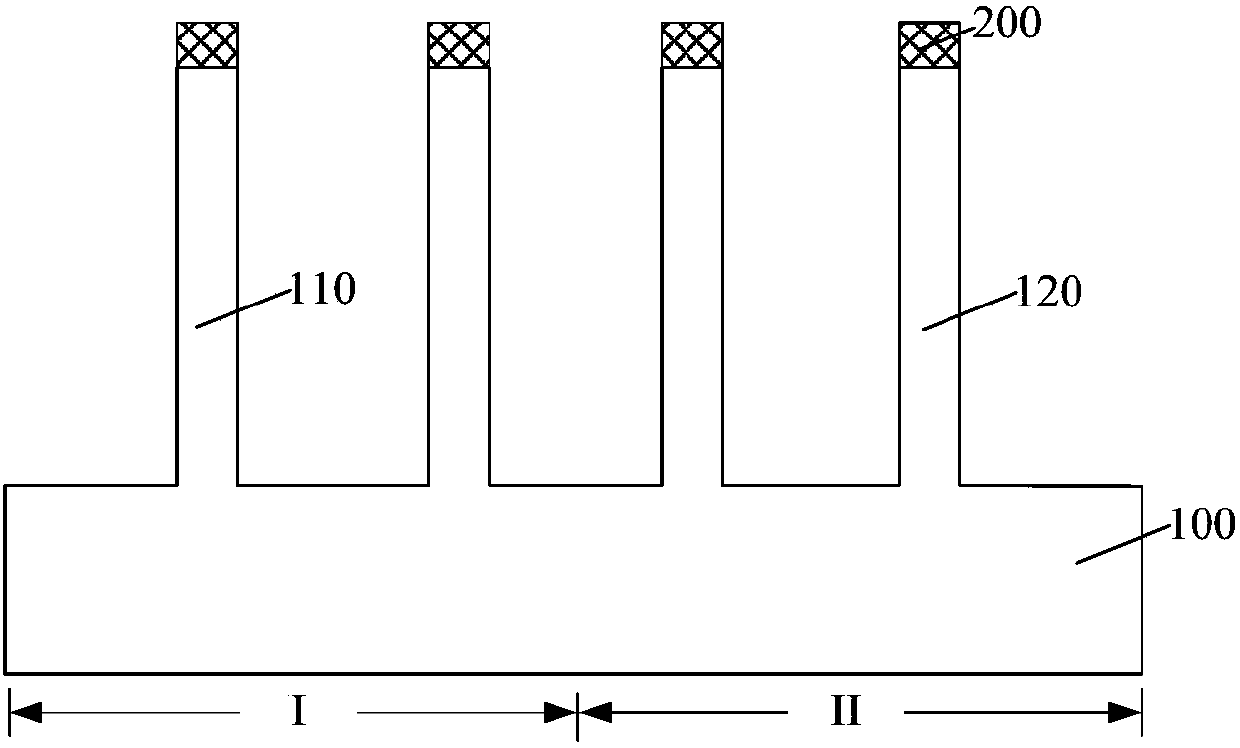

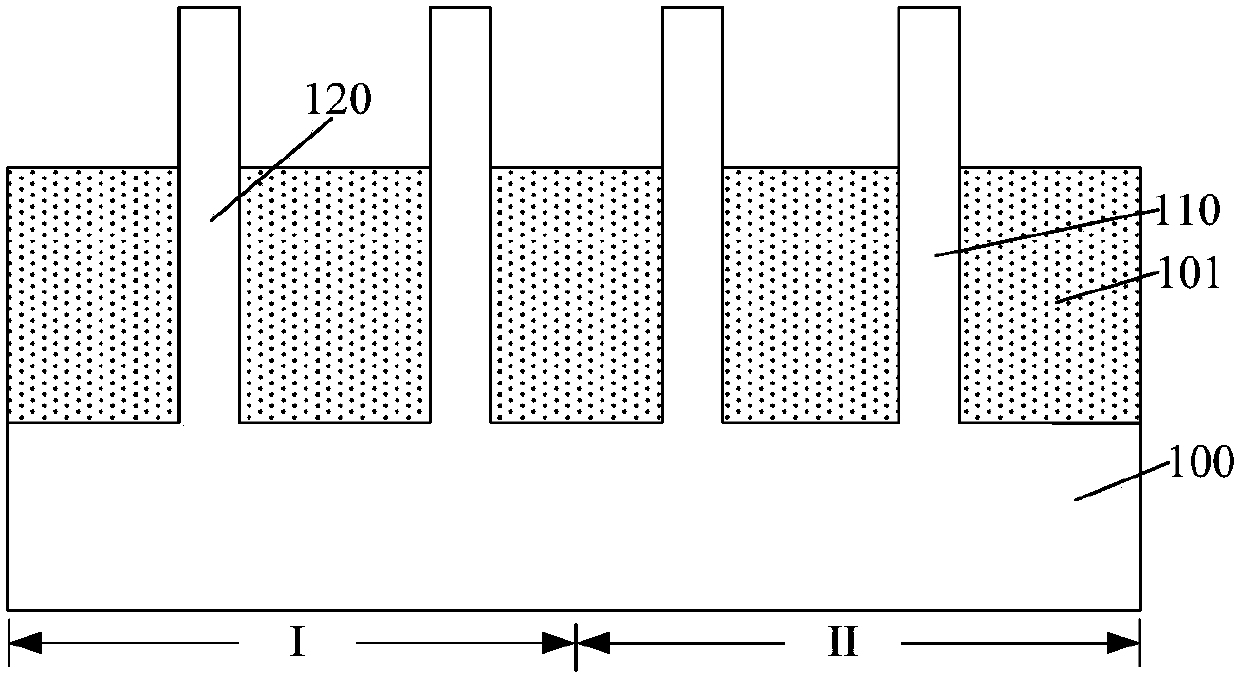

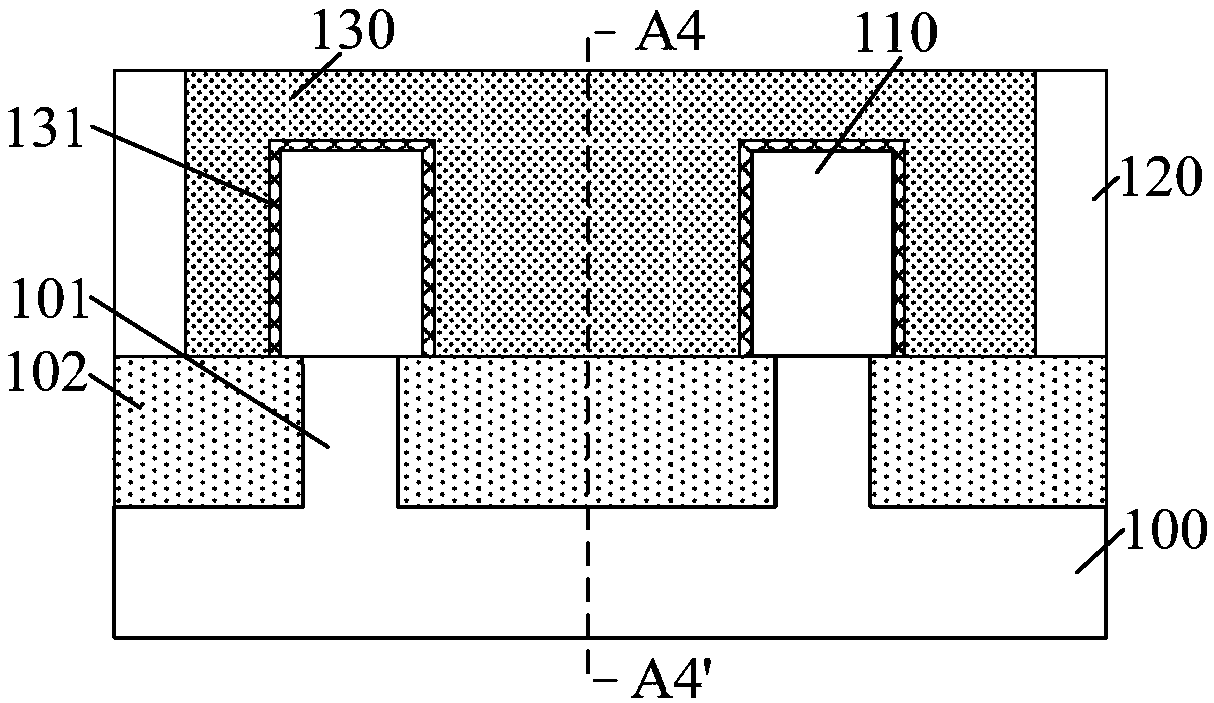

Semiconductor structure and forming method thereof

ActiveCN104617093AImprove performanceReduce the value of parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureParasitic capacitance

The invention provides a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the steps of providing a semiconductor substrate, forming an insulating layer for covering a sacrificial layer and a plurality of first gate structures, etching the insulating layer, and forming a first opening in the surface of the sacrificial layer between the adjacent first gate structures to expose partial surface of the sacrificial layer between the adjacent first gate structures, removing the sacrificial layer, and forming a dielectric layer on the surface of the semiconductor substrate, wherein the plurality of first gate structures, and the sacrificial layer located on the surface of the semiconductor substrate and flush with the surface of the first gate structure are formed on the surface of the semiconductor substrate; the surface of the dielectric layer is higher than that of the insulating layer, and an air gap is formed in the dielectric layer between the adjacent first gate structures. According to the semiconductor device formed by the method, the parasitic capacitance between the adjacent gate structures can be reduced and the performance of a semiconductor device can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Contact pad

ActiveCN102024774AGood isolationIncrease distanceSemiconductor/solid-state device detailsSolid-state devicesContact padIntegrated circuit

A contact pad belongs to protection circuit design field of semiconductor integrated circuit. The contact pad provided by the present invention comprises a pad metal layer, and further comprises a totally depleted layer area formed by simultaneously neutralizing and doping a first type trap and a second type trap for an active region; the totally depleted layer area is located under the pad metal layer and formed at an upper surface layer of a semiconductor substrate. Compared with the prior art, the totally depleted layer area increases a distance between an upper electrode and a lower electrode of the parasitic capacitance of the contact pad, reduces the value of the parasitic capacitance; simultaneously, the preparation of the totally depleted layer area can use the ion implantation of existing art, wherein the operation is simple and extra processes are not needed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

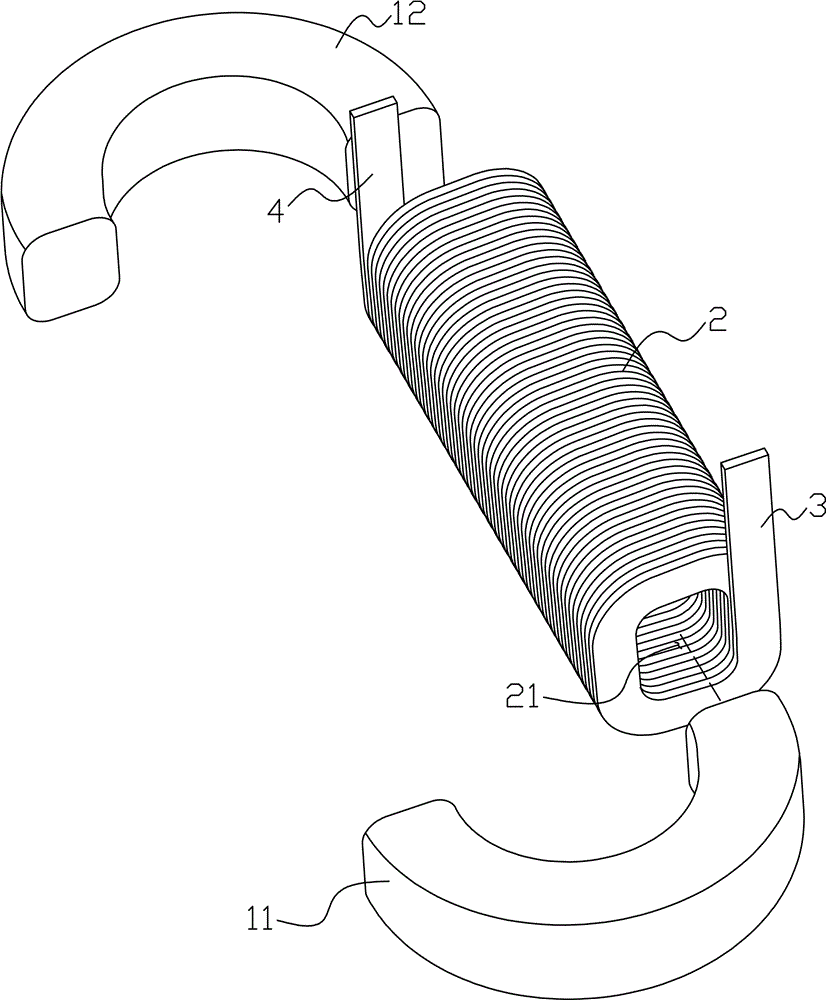

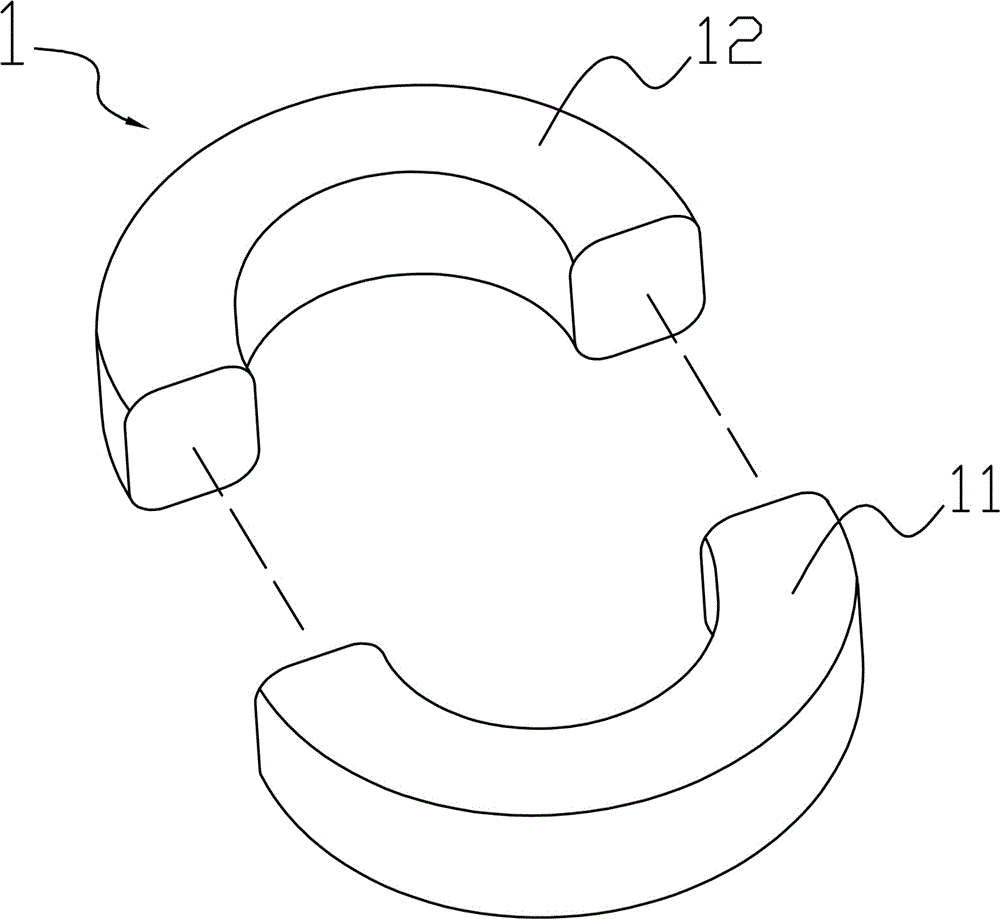

Annular differential-mode inductor and production method thereof

InactiveCN105825998AReduce labor intensityAvoid damageTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresElectricityWinding machine

The present invention relates to the field of magnetoelectric technology, in particular to a ring-shaped differential-mode inductor and a production method thereof. The ring-shaped differential-mode inductor includes a ring-shaped magnetic core and a coil, and the ring-shaped magnetic core is connected by a first magnetic core and a second magnetic core. In combination, the window in the middle of each turn coil forms a magnetic core channel, and the first and second magnetic cores are inserted into the magnetic core channel and then docked. The production method of the annular differential mode inductor comprises the following steps: winding the coil by a winding machine, respectively passing the first and second magnetic cores through the coil, while the second magnetic core is passed through the other end of the coil core channel, and the The starting and tail wires are stripped and soldered. In the present invention, the coil passes through the magnetic core after being wound by a winding machine. The winding process is simple, which solves the problem that the wire diameter is too large and cannot be wound. At the same time, it reduces the labor intensity of workers and improves production efficiency; The copper wire will be damaged or have pinholes during the process, which improves the yield.

Owner:湖口健诚电子电器有限公司

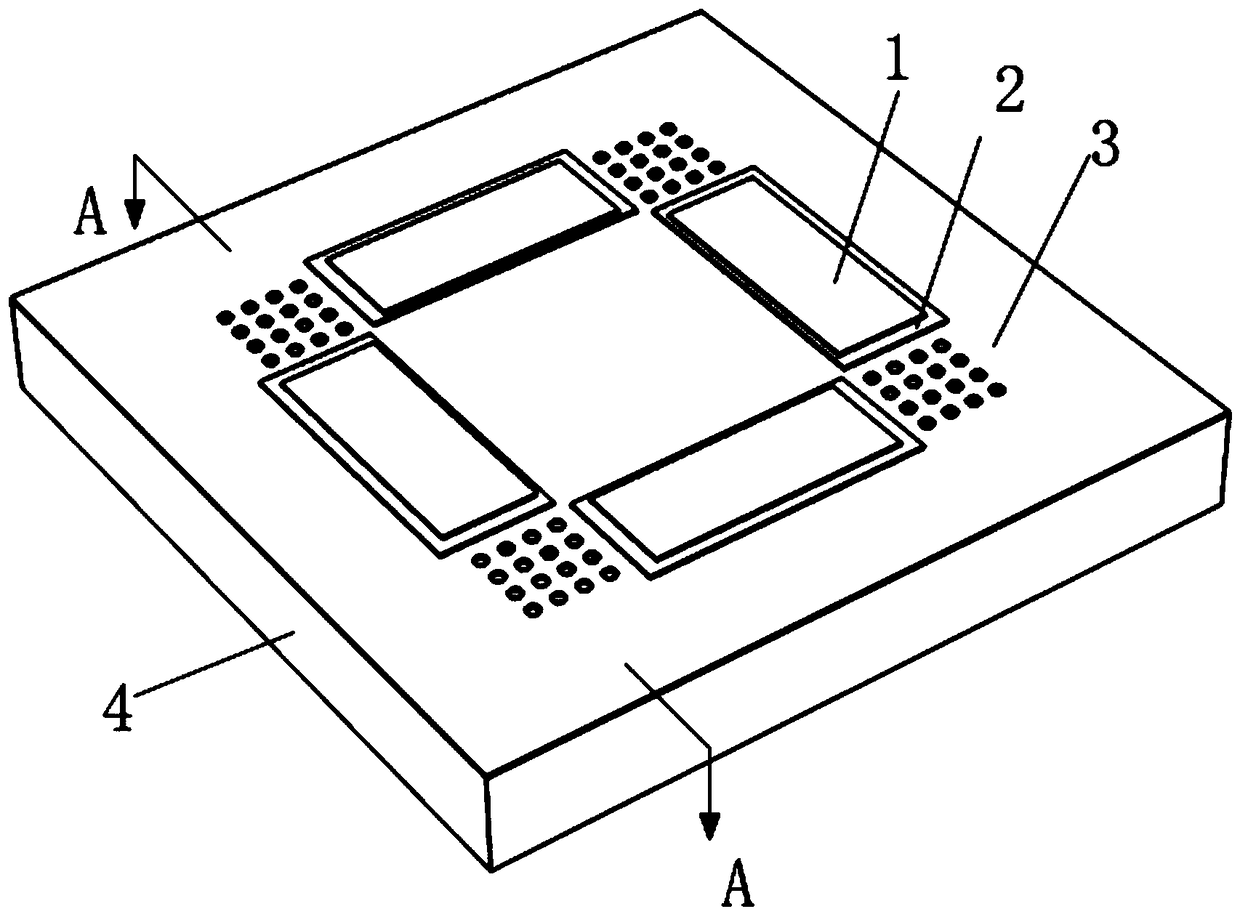

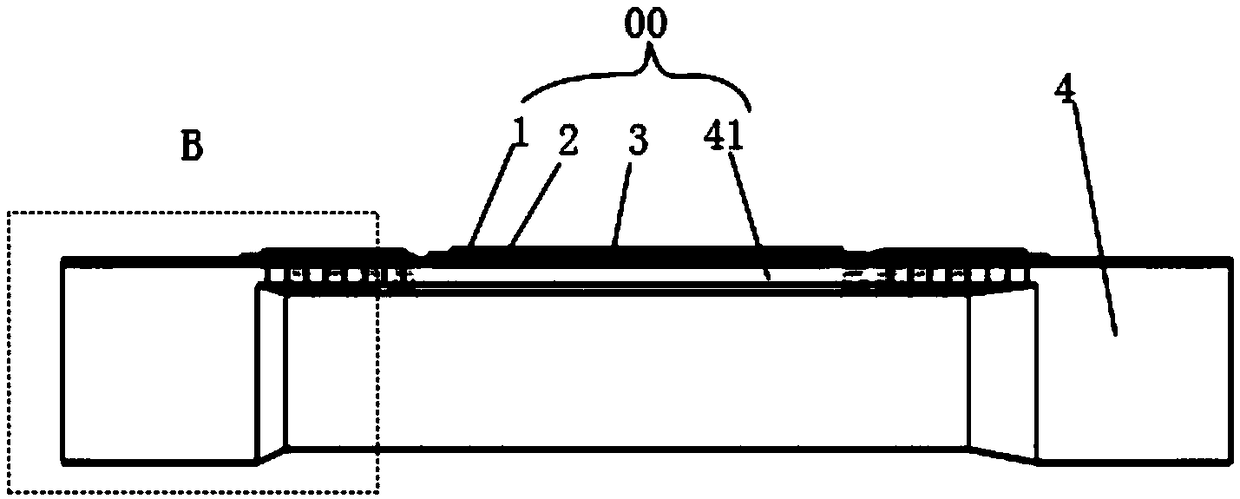

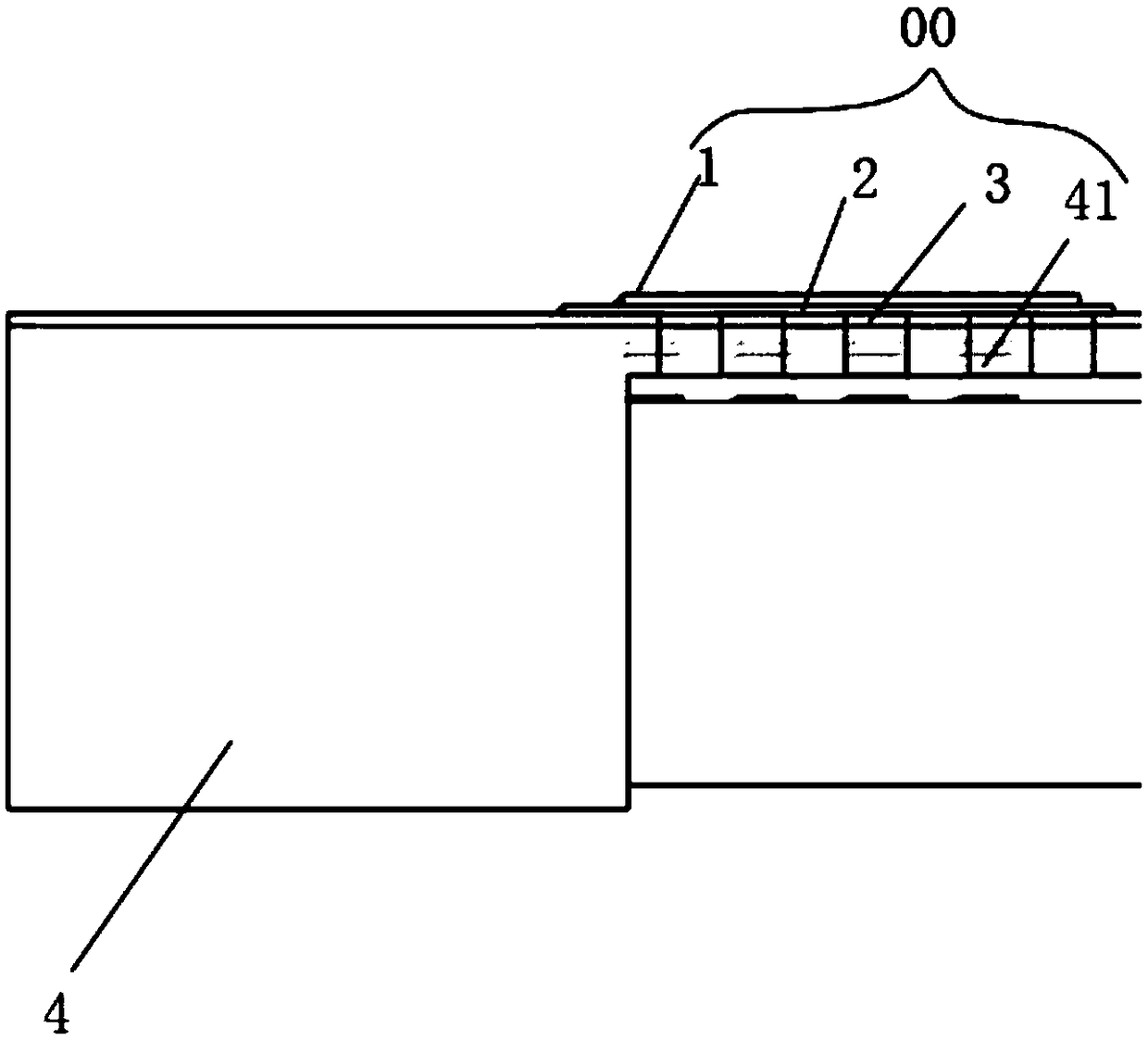

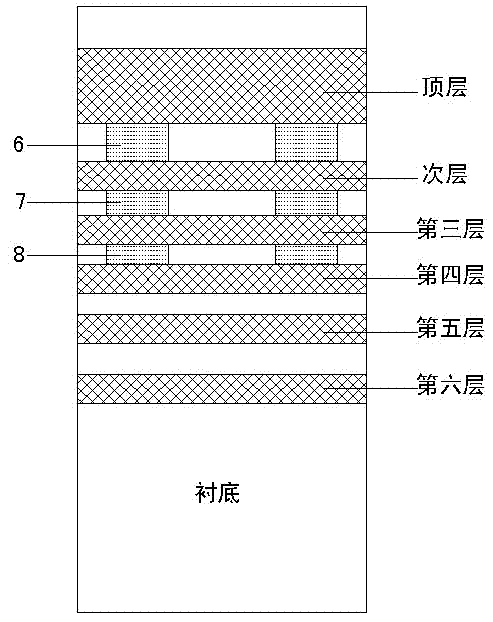

Microcomputer voltage electric ultrasonic transducer with etching hole and sectioned upper electrode

PendingCN109261477AImprove signal-to-noise ratioHigh sensitivityMechanical vibrations separationCapacitanceMicrocomputer

The invention discloses a microcomputer voltage electric ultrasonic transducer with an etching hole and a sectioned upper electrode. The transducer is provided with a substrate, a structural layer, abottom electrode, a piezoelectric layer and the upper electrode. A working principle of the transducer is that direct and inverse piezoelectric effects are used for realizing conversion from mechanical energy to electric energy or the electric energy to the mechanical energy. The transducer is capable of dividing the upper electrode and the piezoelectric layer in an original square ring structureto four pieces of equal area rectangular structures. Such structure is capable of reducing an opposite area of the upper electrode and the bottom electrode, thereby reducing a stray capacitance, and improving a signal to noise ratio of the ultrasonic transducer. At the same time, small holes are etched at four empty corners, so rigidity of a vibrating diaphragm is advantageously reduced, and transmitting sensitivity of the transducer is improved, thereby loss of the transmitting sensitivity of the transducer caused by reducing the area of the upper electrode is remedied.

Owner:ZHEJIANG UNIV

Contact bonding pad for reducing parasitic capacitance and manufacturing method thereof

ActiveCN101533813AIncrease distanceLow manufacturing process costSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceEngineering

The invention discloses a contact bonding pad for reducing parasitic capacitance and a manufacturing method thereof, and belongs to the technical field of semiconductor manufacture. The contact bonding pad comprises a bonding pad metal layer, and a full exhaust layer area formed by alternative doping of a first type semiconductor and the second type semiconductor in the adjacent areas; the full exhaust layer area is formed in the semiconductor substrate and located on the upper surface of the semiconductor substrate below the bonding pad metal layer. The full exhaust layer area exbands the distance between the bonding pad metal layer and the semiconductor substrate and reduces the parasitic capacitance value of the contact bonding pad; meanwhile, the method for manufacturing the full exhaust layer area is simple, and does not increases the manufacturing processing cost of the contact bonding pad.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

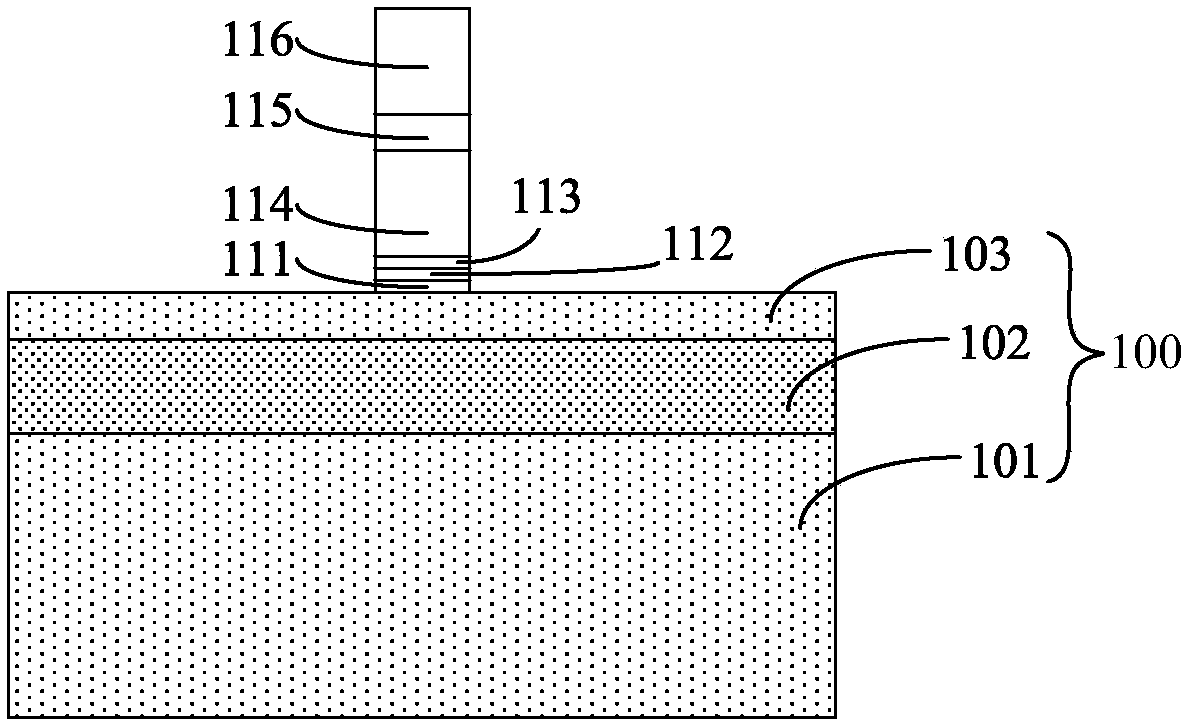

Semiconductor transistor structure and preparation method thereof

PendingCN109390402AReduce the value of parasitic capacitanceLow switching energySemiconductor/solid-state device manufacturingSemiconductor devicesResistance capacitanceIsolation layer

The present invention provides a semiconductor transistor structure and a preparation method thereof. The structure comprises: a semiconductor substrate; a grid module located on the semiconductor substrate, wherein the grid module comprises a grid dielectric layer and a grid conductive layer located on the grid dielectric layer; a side wall isolation structure located at the side wall of the gridmodule, wherein the side wall of the grid module comprises a first isolation layer, an air insulation layer and a second isolation layer arranged in order from inside to outside; and bolt conductivelayers located at two sides of the grid module, wherein the side wall isolation structure is configured to separate the bolt conductive layers from the grid module. The semiconductor transistor structure and the preparation method thereof can effectively reduce the stray capacitance value so as to improve the resistance-capacitance delay increasing speed and reduce the switching energy.

Owner:CHANGXIN MEMORY TECH INC

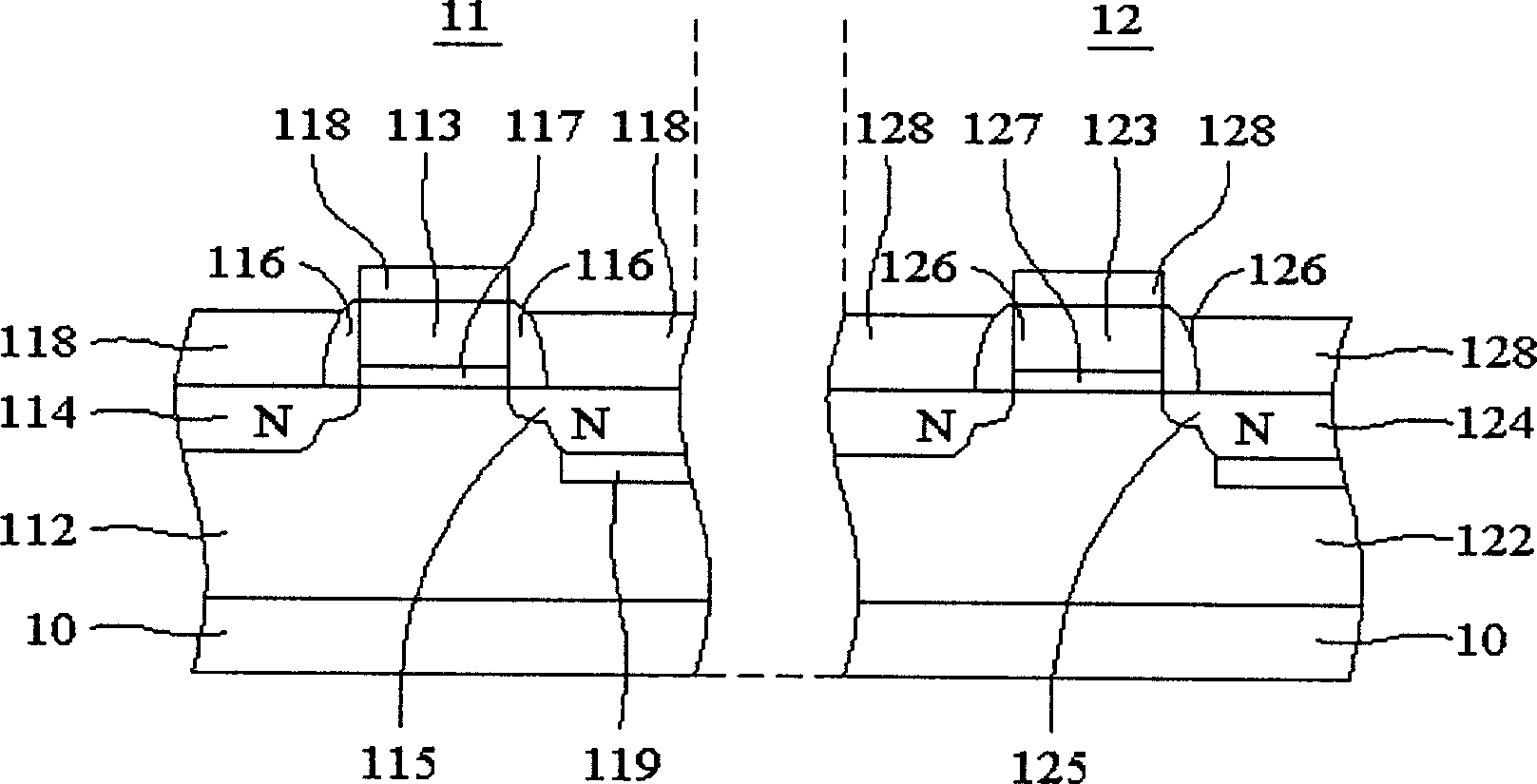

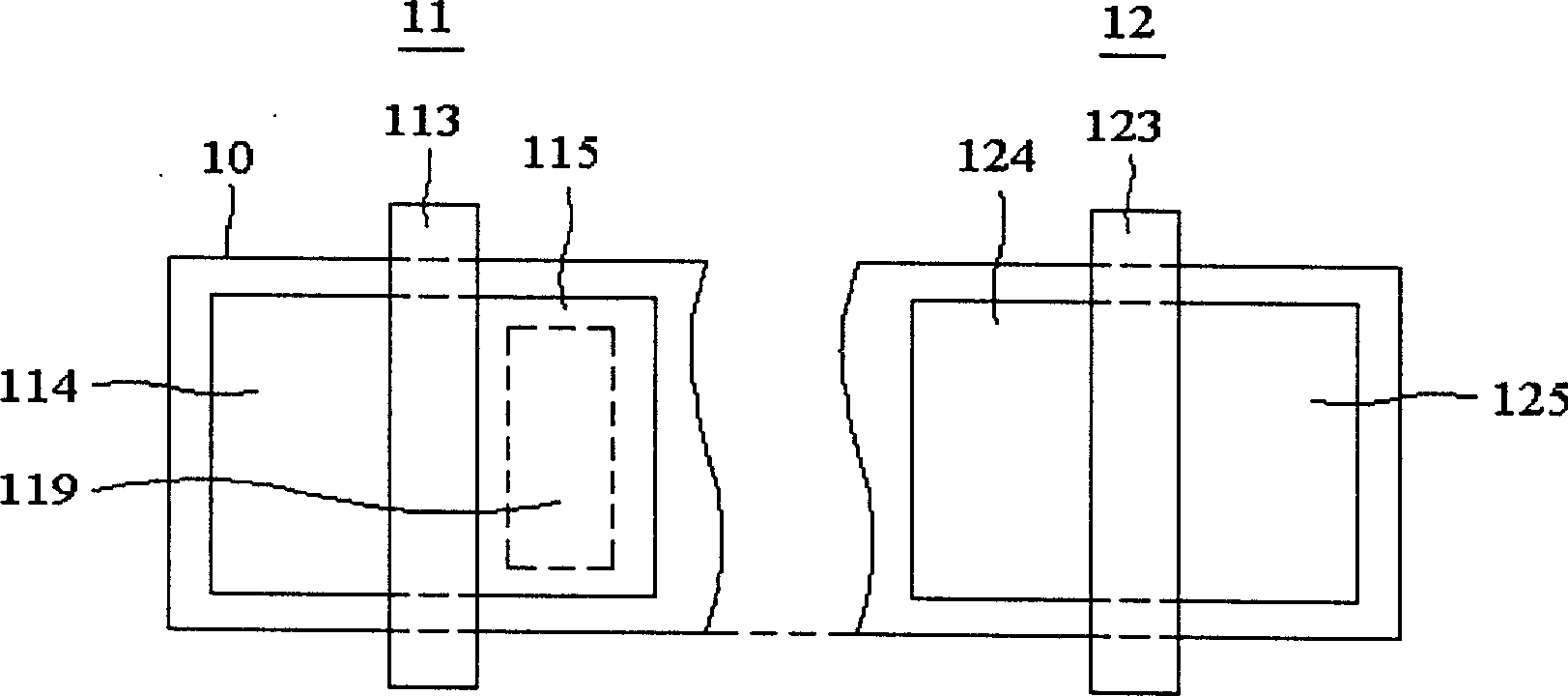

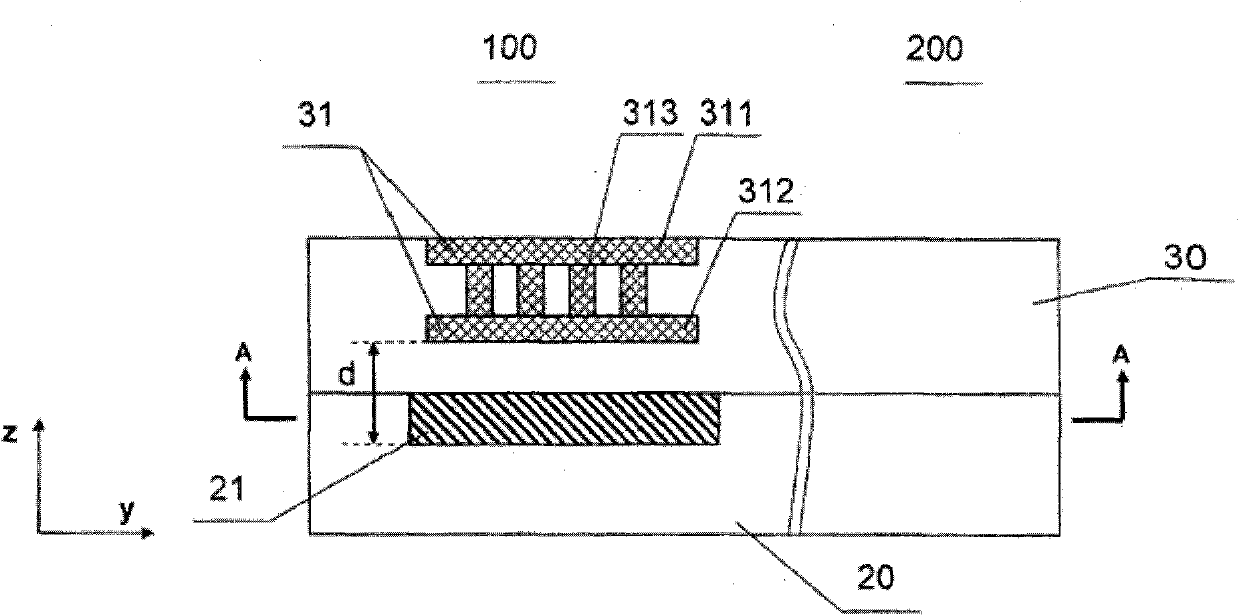

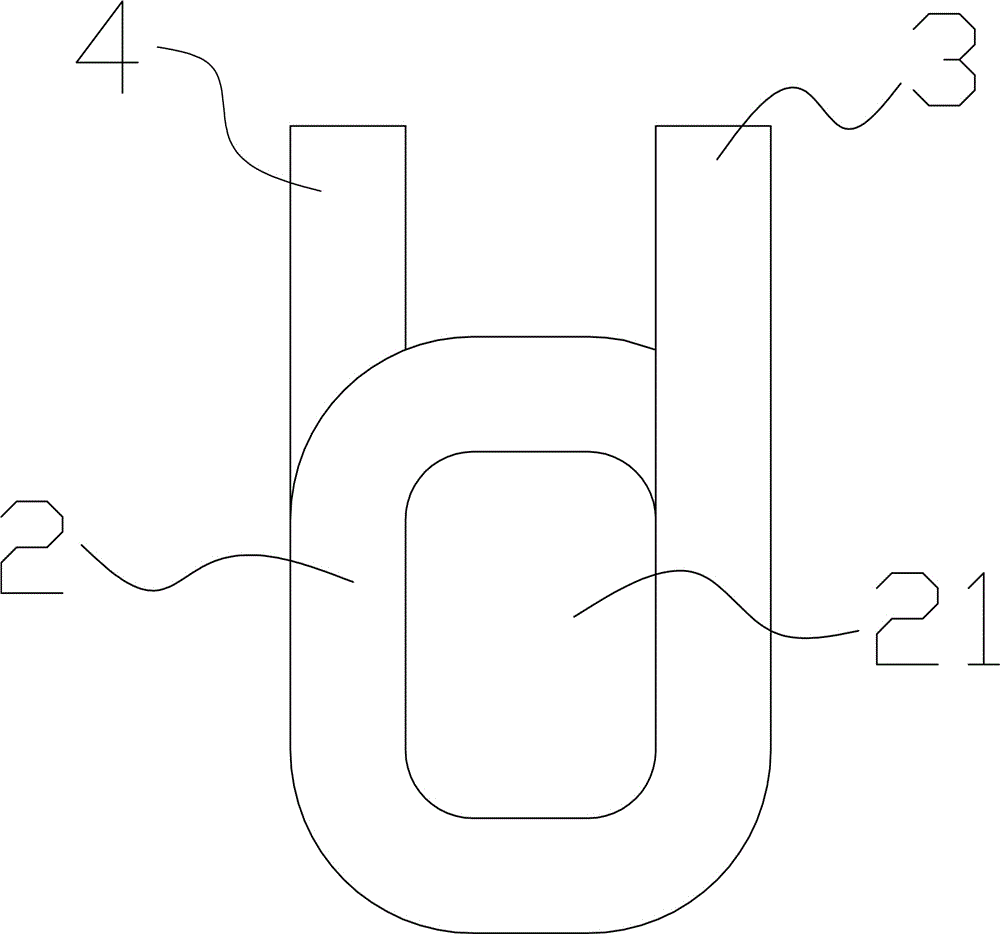

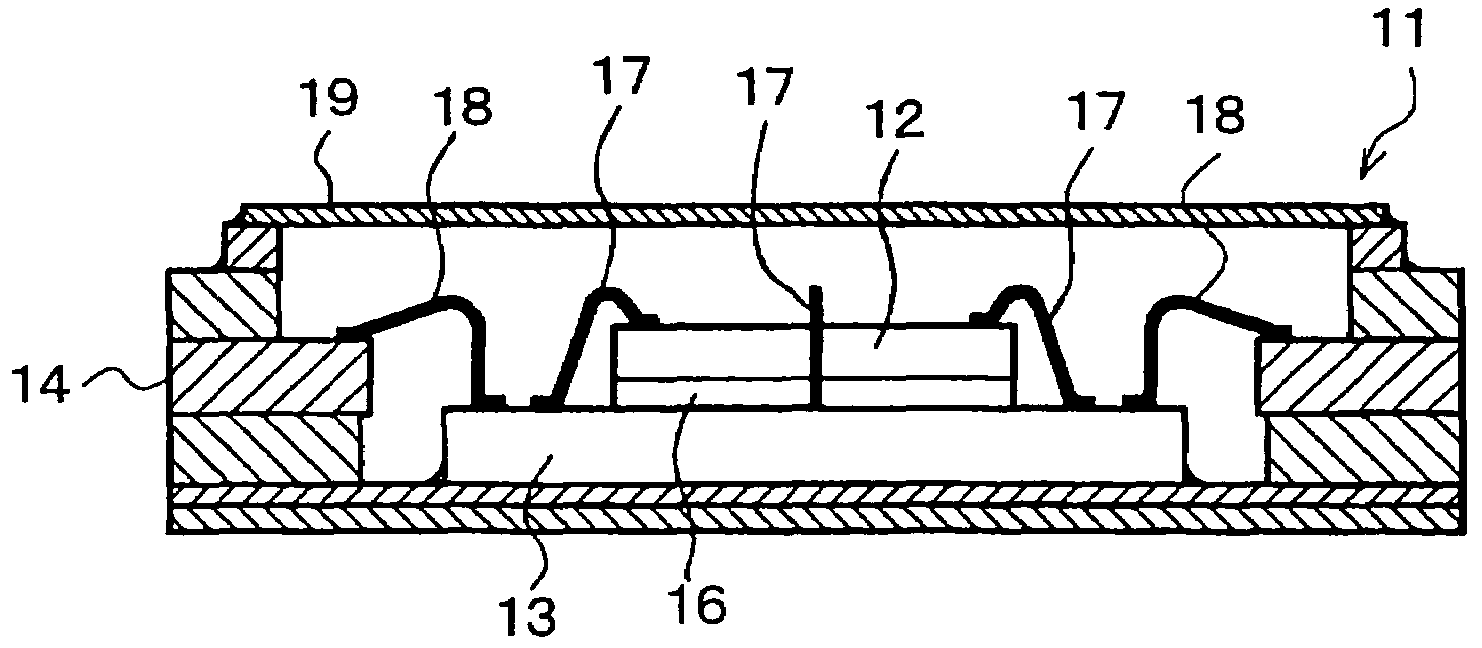

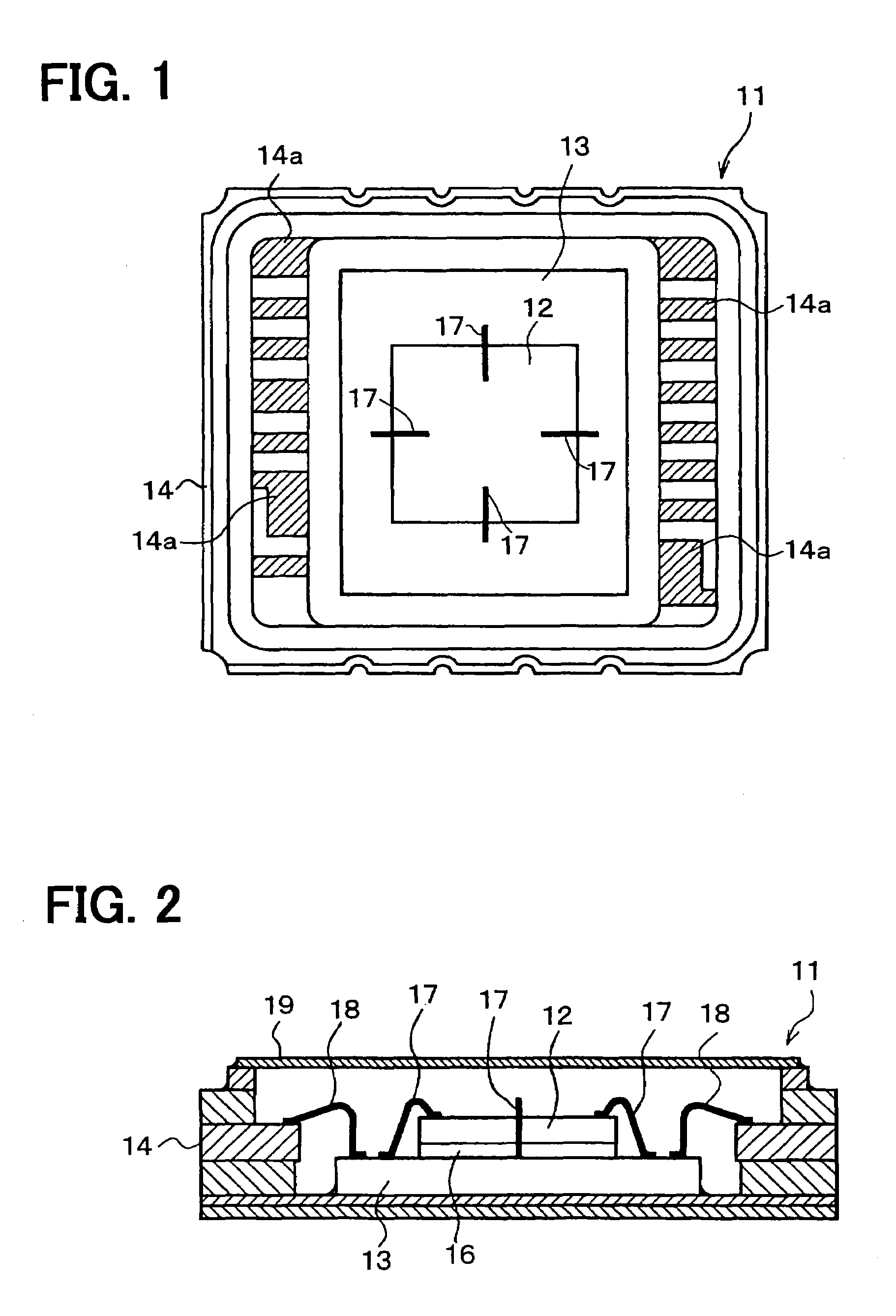

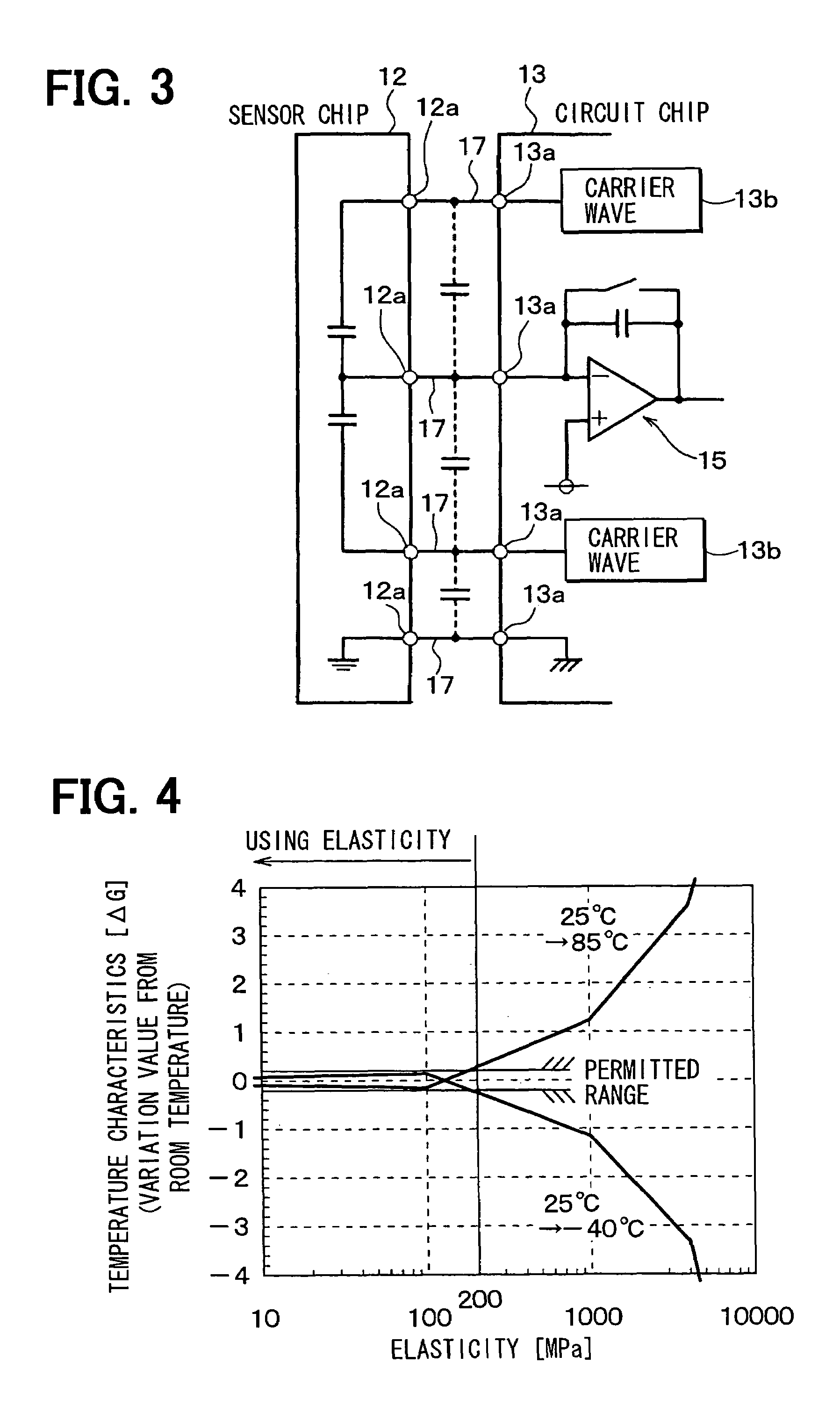

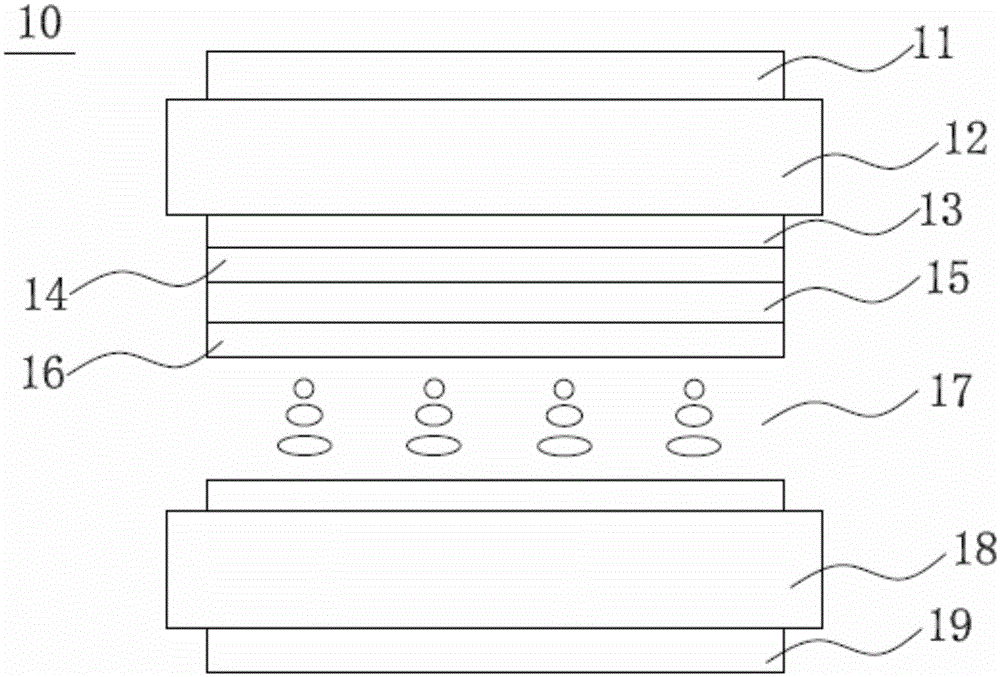

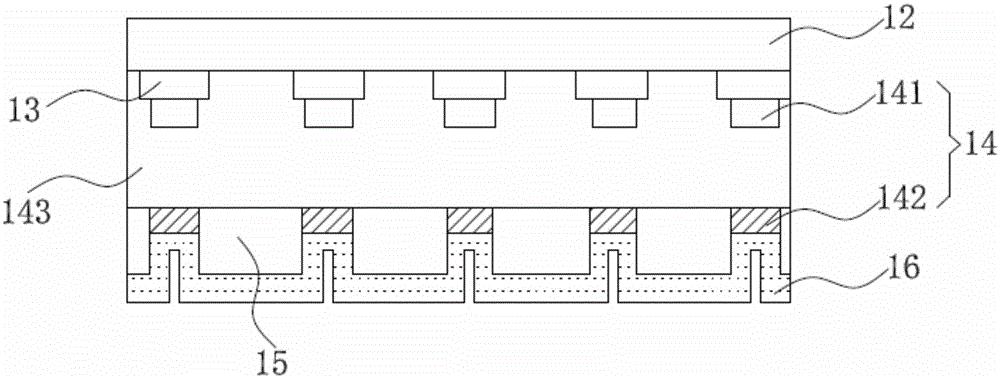

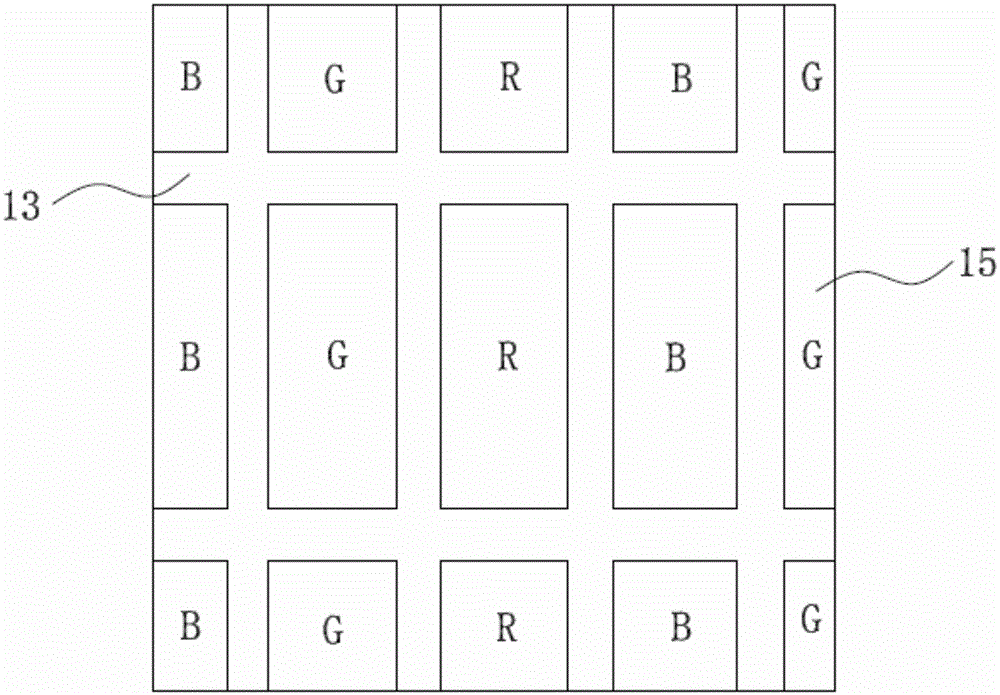

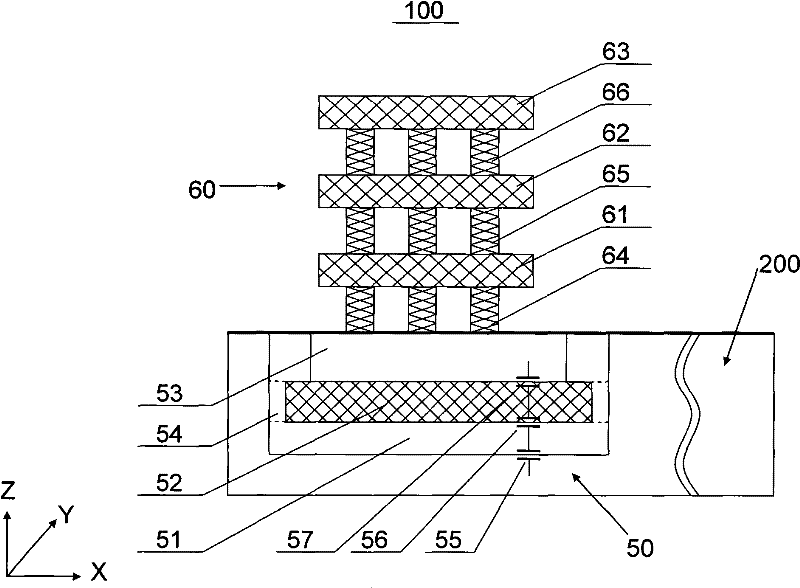

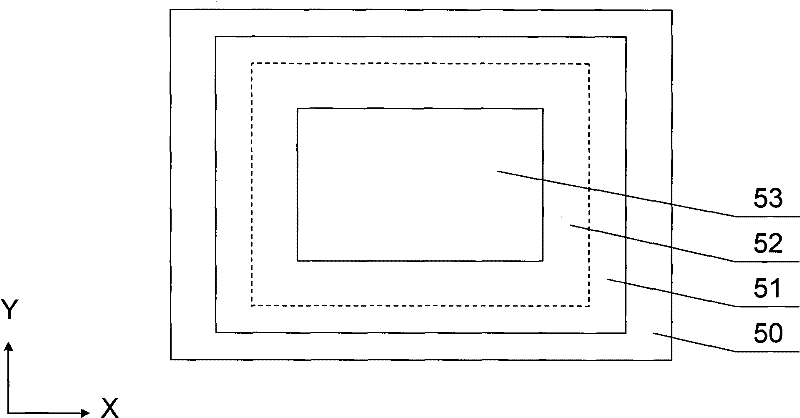

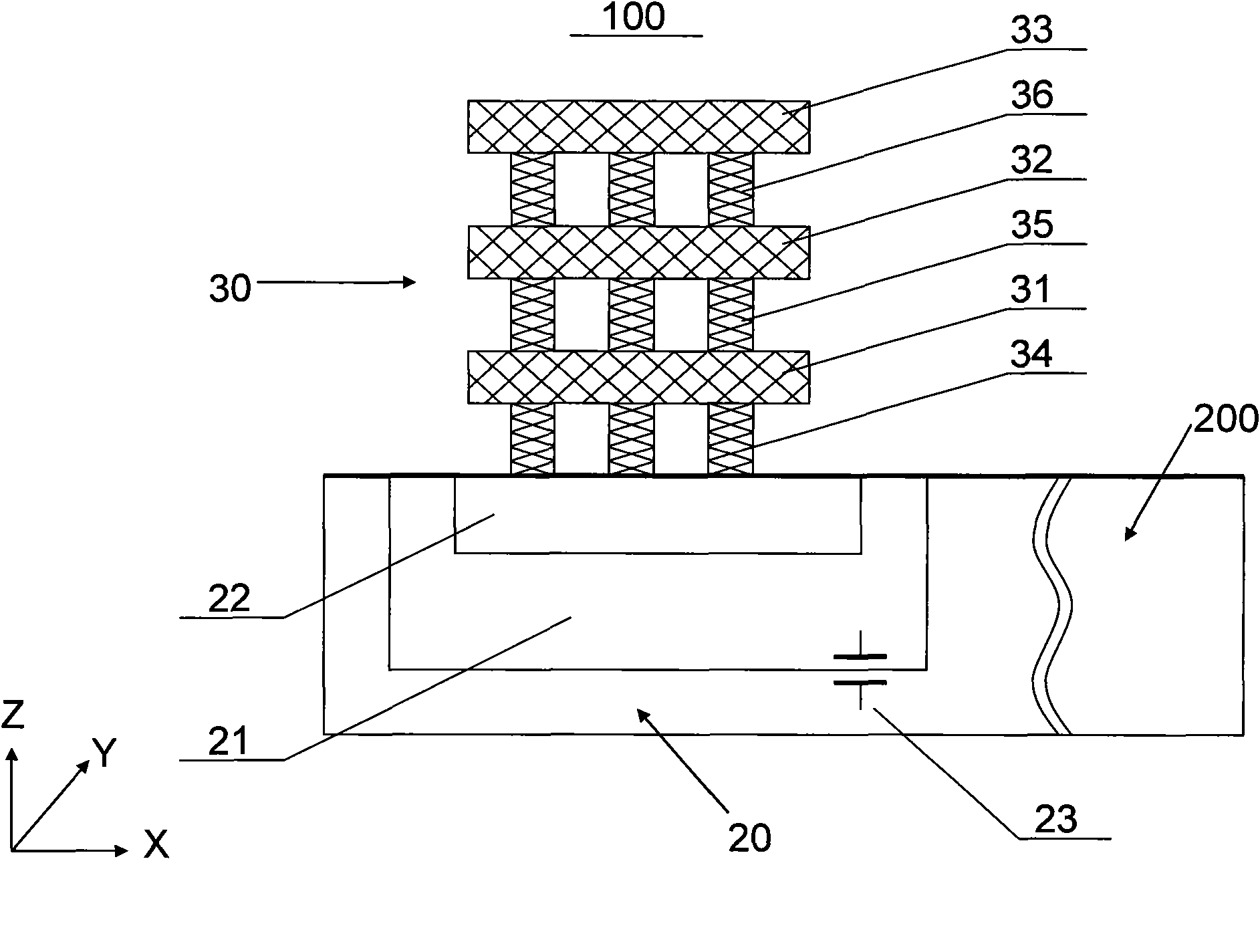

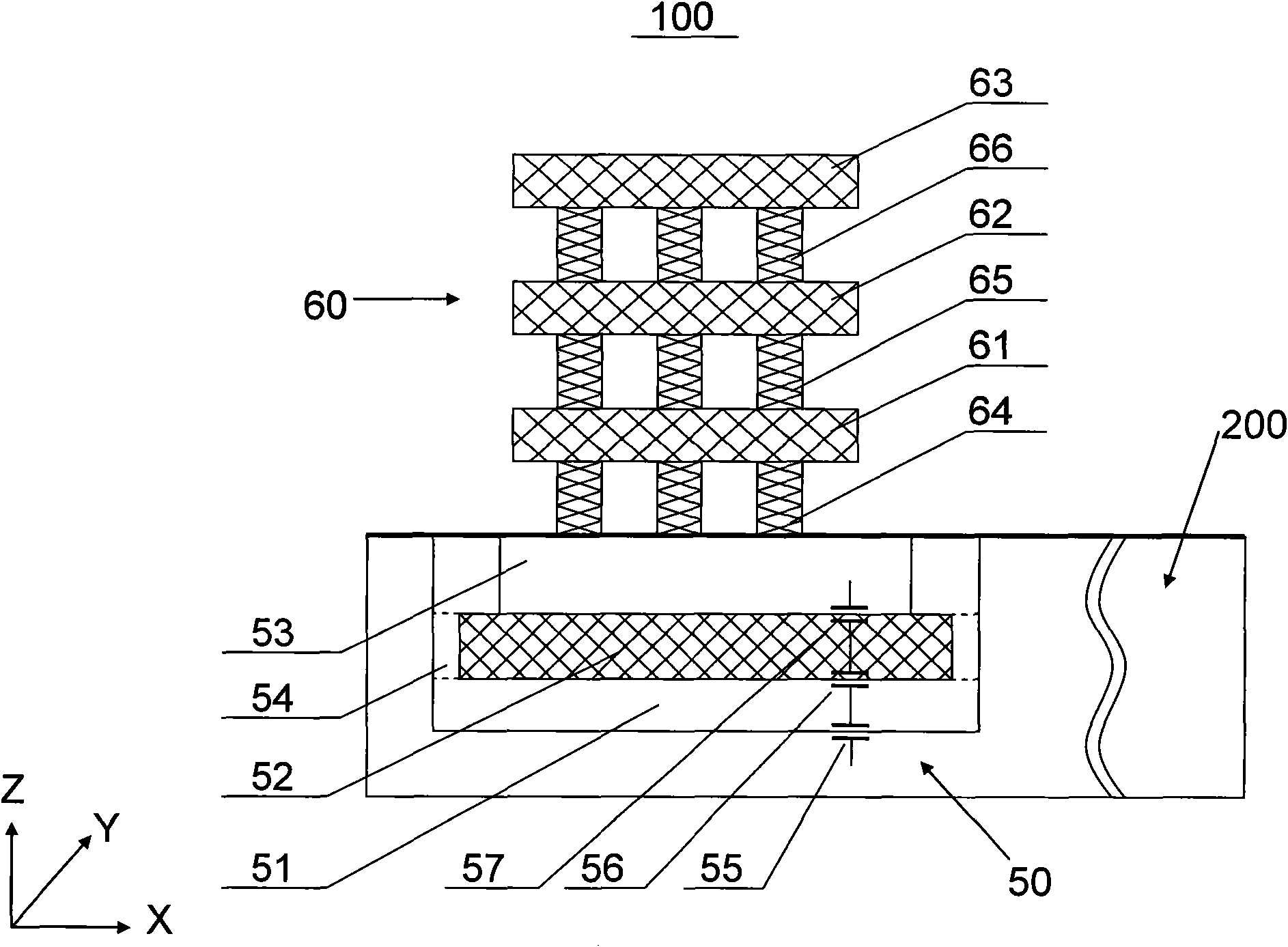

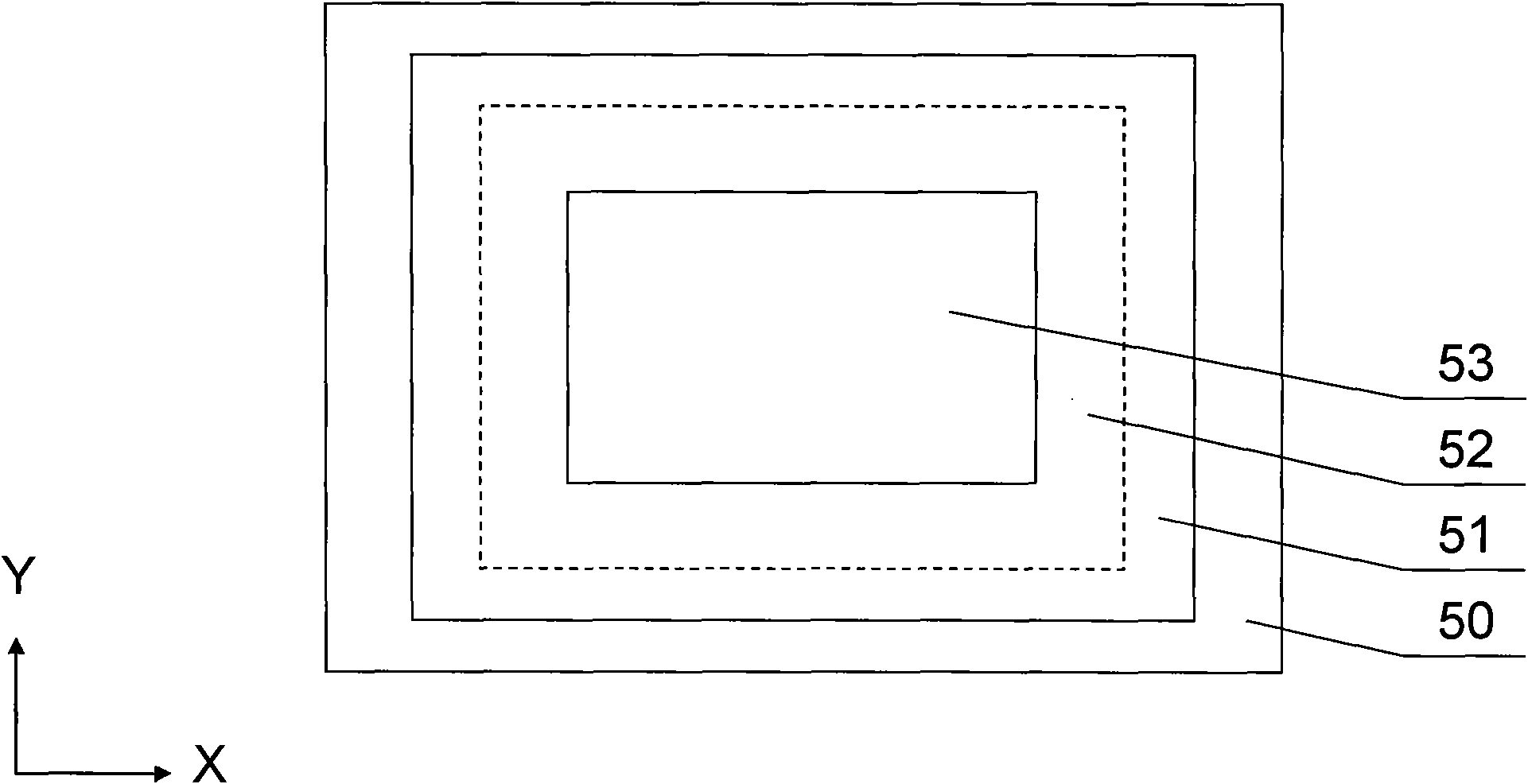

Capacitance type semiconductor sensor

InactiveUS7339265B2Reduce adverse effectsImprove featuresSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceSemiconductor sensor

Owner:DENSO CORP

Touch display device and manufacturing method thereof

InactiveCN106484157AImprove touch performanceImprove the display effectInput/output processes for data processingTouch SensesDisplay device

A touch display device and a manufacturing method thereof are provided. The touch display device has a touch sensing area and a virtual touch area, and comprises a first and a second metal layer, filter layers, and common electrode layers. The first metal layer is arranged below an upper glass substrate, and the first metal layer includes a first touch line that is located in the touch sensing area; the second metal layer is arranged below the first metal layer, and includes a second touch line and a second virtual line, wherein the second touch line is located in the touch sensing area, the second virtual line is located in the virtual touch area, and the second touch line and the first touch line form a touch sensing element; the filter layer located in the touch sensing area covers the second touch line, and the filter layer located in the virtual touch area does not cover the second virtual line; and the common electrode layer located in the touch sensing area is not in contact with the second touch line, and the common electrode layer located in the virtual touch area is in direct contact with the second virtual line to reduce the resistance of the common electrode layer. The present invention also discloses a manufacturing method for the touch display device.

Owner:AU OPTRONICS CORP

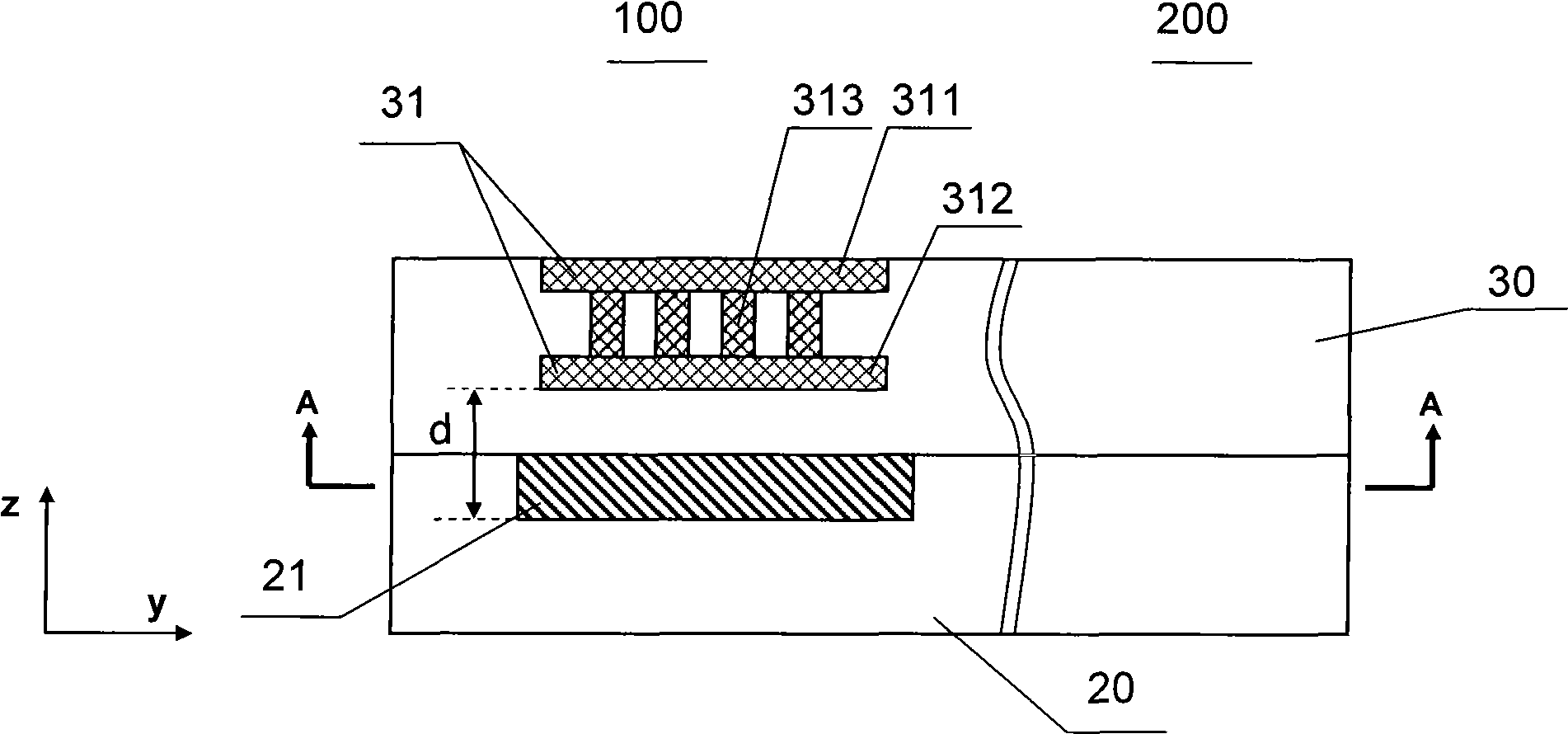

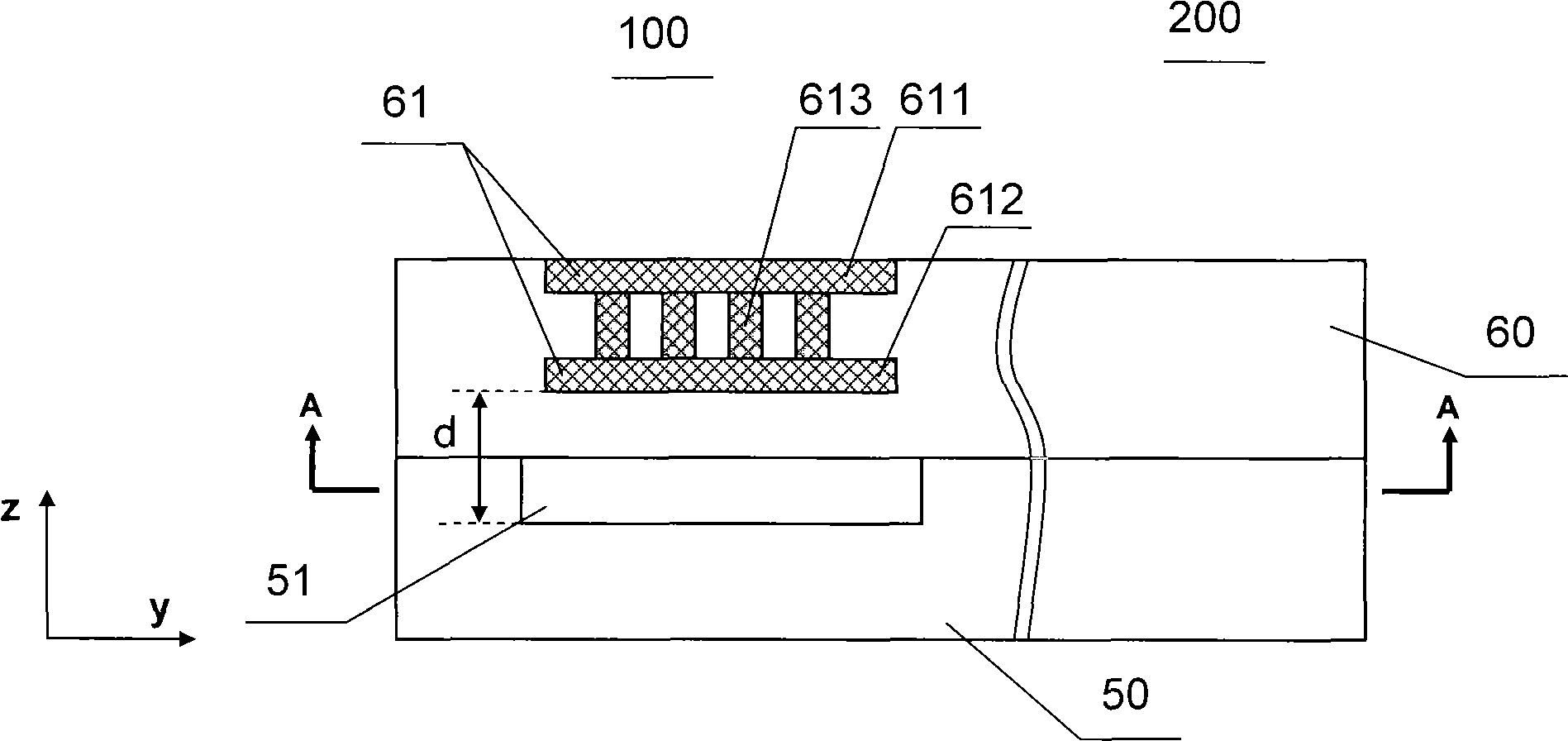

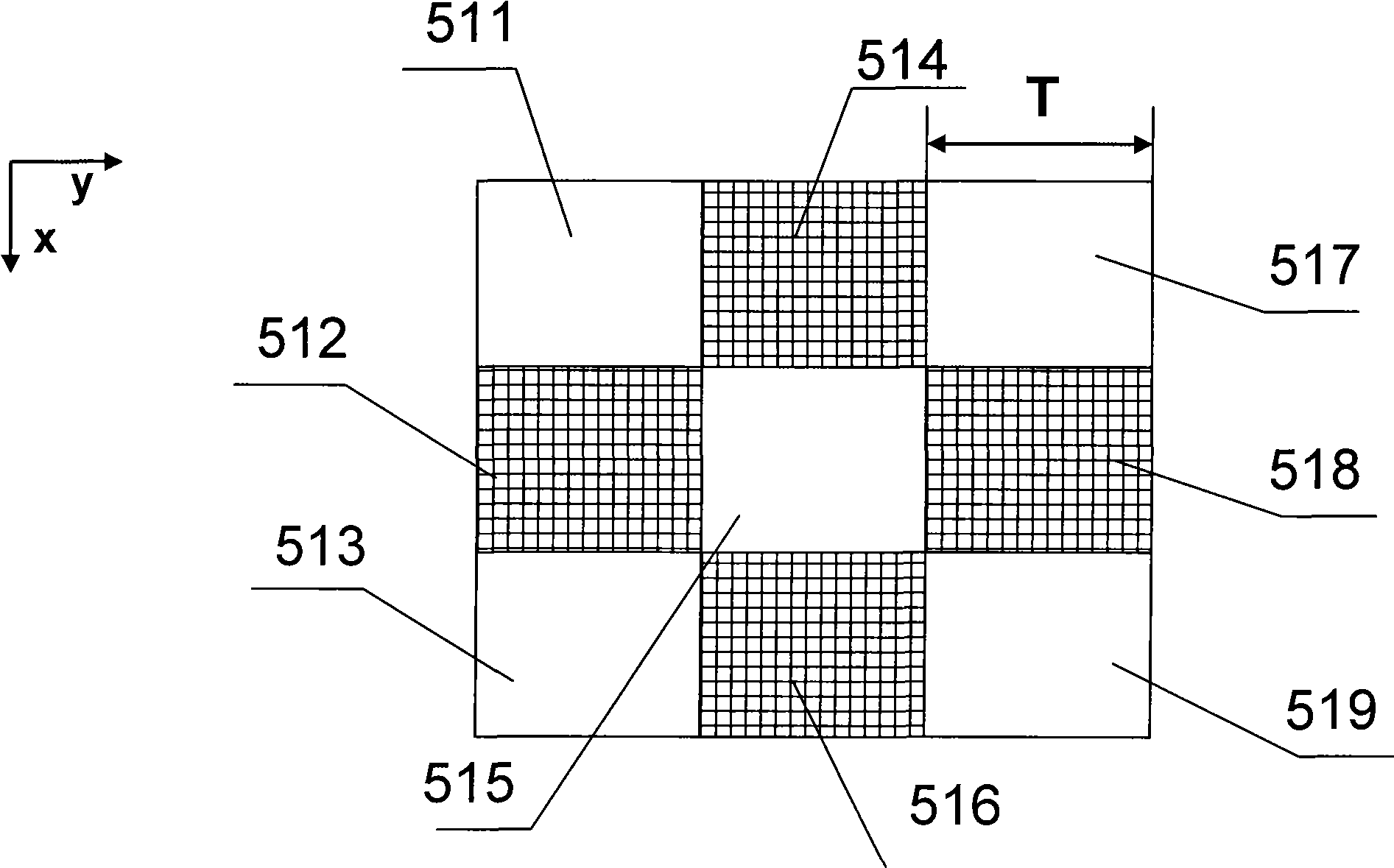

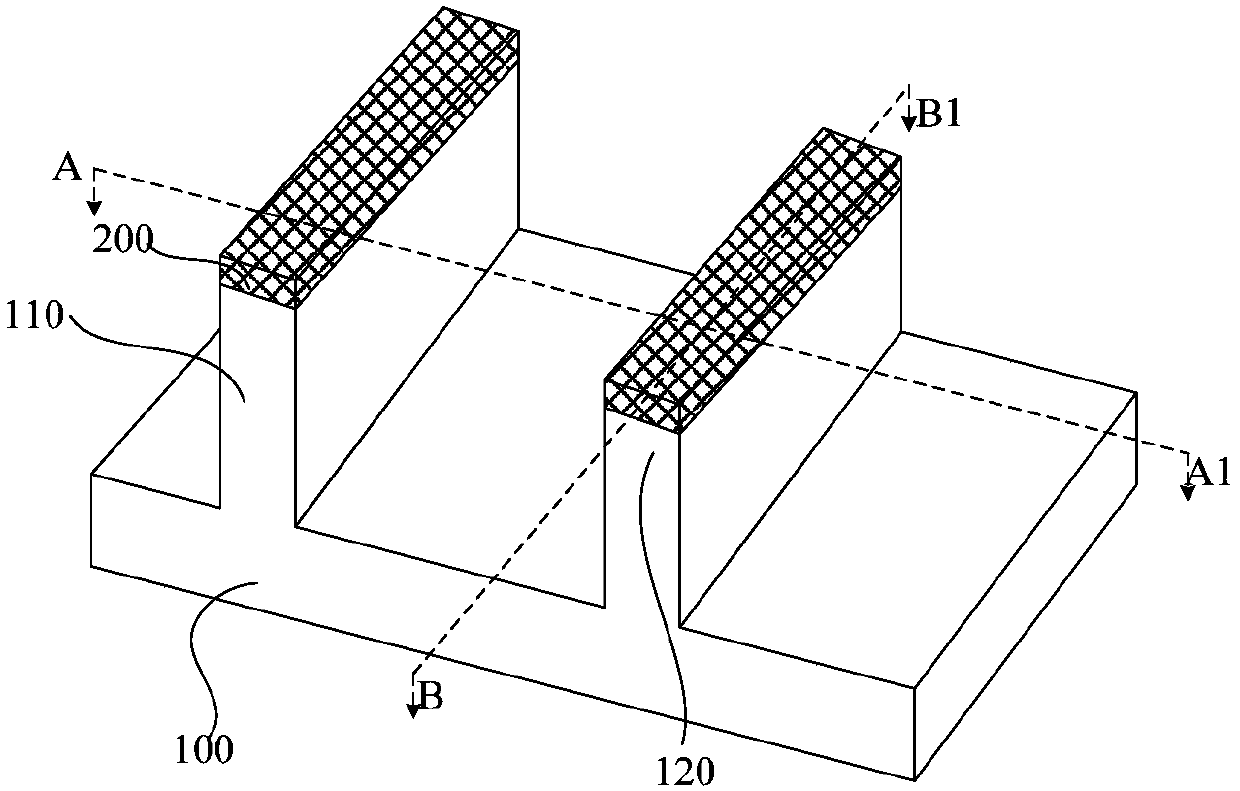

Sandwich type micro accelerometer with high signal to noise ratio

PendingCN109946482AHigh measurement accuracyImprove signal-to-noise ratio characteristicsAcceleration measurement using interia forcesAccelerometerSignal-to-noise ratio (imaging)

The invention discloses a sandwich type micro accelerometer with a high signal to noise ratio. The micro accelerometer comprises an upper electrode structure layer, an upper bonding contract area, a middle electrode structure layer, a lower bonding contract area and a lower electrode structure layer from top to bottom, wherein the upper electrode structure layer is provided with the upper bondingcontract area bonded with the middle electrode structure layer; the lower electrode structure layer is provided with the lower bonding contract area bonded with the middle electrode structure layer; the upper bonding contract area and the lower bonding contract area form a bonding contact layer; the upper electrode structure layer, the middle electrode structure layer and the lower electrode structure layer are fused and bonded in the upper bonding contract area and the lower bonding contract area to form a self-sealed structure; and the middle electrode structure layer comprises a moveable mass block. Stray capacitance values of the upper electrode structure layer, the lower electrode structure layer and the middle electrode structure layer on a device can be reduced to a large extent, and in case of a same electrode plate interval, the signal to noise ratio property of the sandwich type micro accelerometer can be remarkably improved.

Owner:四川知微传感技术有限公司

Semiconductor structure and forming method therefor

ActiveCN107591366APlay a protective effectPrevent proliferationTransistorSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

The invention discloses a semiconductor structure and a forming method therefor, and the method comprises the steps: providing a substrate; forming metal gate structures on the substrate on the substrate, wherein each metal gate structure comprise a gate dielectric layer, a work function layer located on the gate dielectric layer, and a metal layer located on the work function layer; forming a barrier layer at the tops of the metal gate structures; forming an interlayer dielectric layer on the substrate between the metal gate structures; forming a contact hole plug passing through the interlayer dielectric layer; and carrying out the annealing treatment of the substrate after the forming of the contact hole plug. After the forming of the metal gate structures, the barrier layer is formed at the tops of the metal gate structures. The barrier layer is used for protecting the metal gate structures in the subsequent annealing treatment, and prevents the atoms liable to diffuse in the annealing treatment to diffuse to the work function layers of the metal gate structures, thereby avoiding the impact on the work function values of the work function layers, and achieving optimization of the electrical performances of a semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

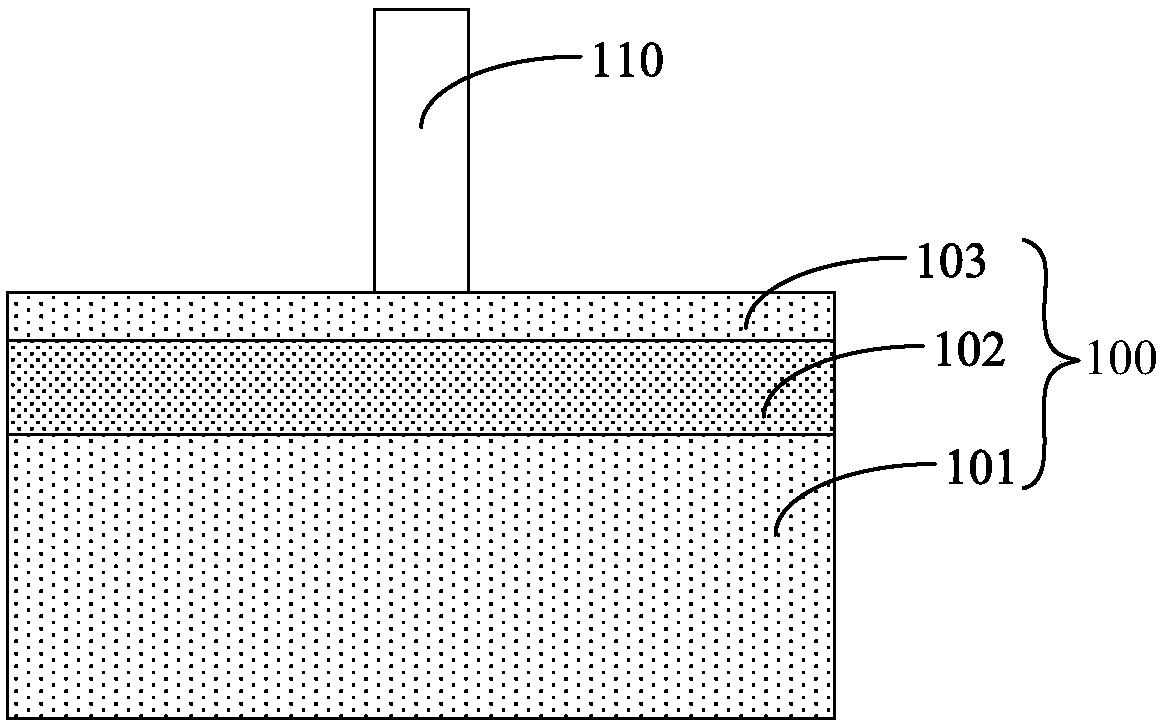

Semiconductor structure and manufacturing method thereof

ActiveCN108565287AReduce the dielectric valueImprove electrical characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesResistance capacitanceSemiconductor structure

The invention provides a semiconductor structure and a manufacturing method thereof. The semiconductor structure manufactured with the manufacturing method comprises a substrate and a grid formed on the substrate, and silicon epitaxy layers are formed at the portions, located on the substrate, of the two sides of the grid; first side walls are arranged on the side surfaces of the grid, intervals are formed between the first side walls and the silicon epitaxy layers, the surfaces of the first side walls also comprise second side walls, the second side walls cover the intervals, and air gaps areformed between the first side walls and the silicon epitaxy layers. According to the semiconductor structure and the manufacturing method thereof, the dielectric constant of the grid side walls is reduced, stray capacitance of a device is effectively reduced accordingly, and corresponding resistance-capacitance delay time is shortened.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

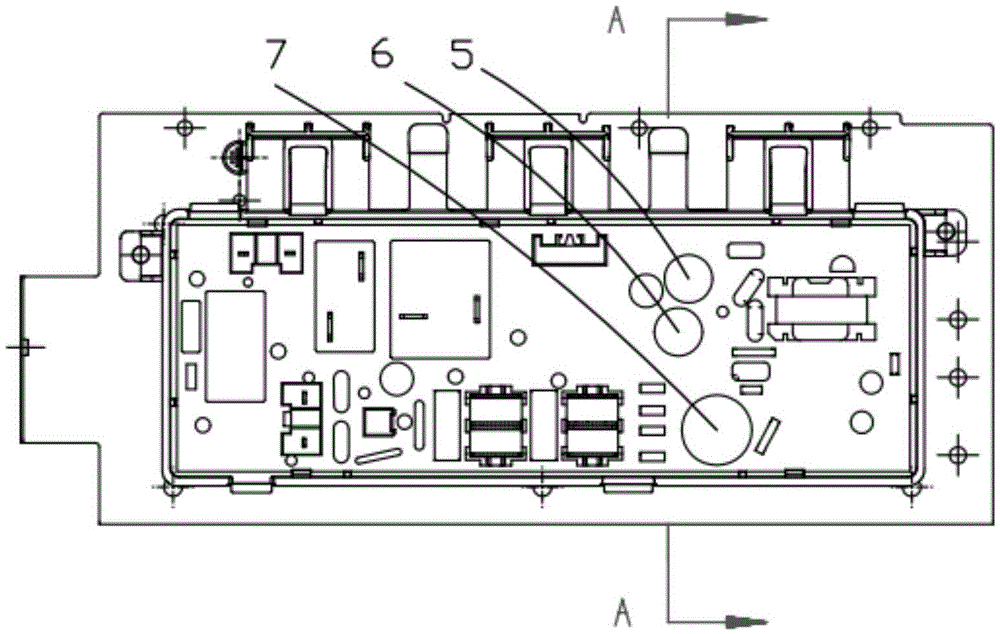

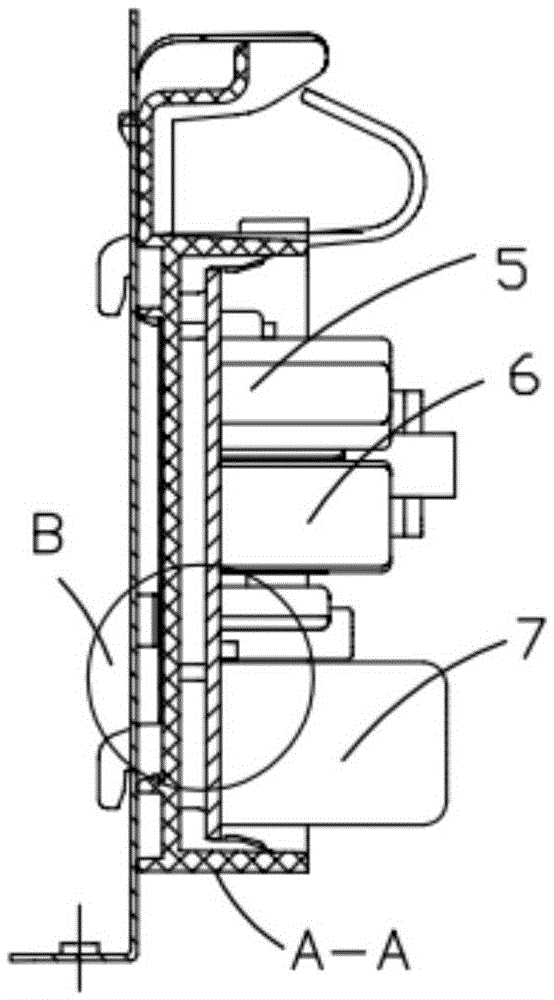

Domestic appliance and apparatus for reducing disturbance voltage

ActiveCN105636421ALow dielectric constantReduce the value of parasitic capacitanceScreening casingsDisturbance voltageParasitic capacitance

The invention provides a domestic appliance and an apparatus for reducing disturbance voltage. The domestic appliance comprises a circuit board, a circuit board box and a metal plate; the circuit board box is made from an insulating material, and positioned between the circuit board and the metal plate, wherein the domestic appliance also comprises a metal sheet; the metal sheet is arranged between the circuit board and the circuit board box, or between the metal plate and the circuit board box; and the metal sheet, the metal plate and the circuit board are spaced at preset distances mutually, and are not electrically contacted. The invention also provides a method for reducing disturbance voltage of the domestic appliance. According to the domestic appliance and the method for reducing disturbance voltage of the domestic appliance provided by the invention, the dielectric constant and stray capacitance can be effectively lowered so as to reduce the disturbance voltage; and in addition, the domestic appliance has the advantages of simple mounting structure, convenience, and economical and practical performance.

Owner:QINGDAO HAIER WASHING MASCH CO LTD

Layout structure of electrostatic discharge protecting circuit and its manufacturing method

InactiveCN101154657AReduce areaReduce the impact of featuresSemiconductor/solid-state device detailsSolid-state devicesCapacitanceParasitic capacitor

The invention discloses an arrangement of an ESD protection circuit and a method for manufacturing the same. The ESD protection circuit comprises a substrate, a protection component and a resistor, wherein, the resistor is arranged in the region of the protection component, in part or whole area. As a result, the occupied area by the resistor is reduce and the junction parasitic capacitor generated inside the protection component, thereby reducing the manufacture cost of the ESD protection circuit and the influence of the ESD protection circuit on the whole internal circuit to the lowest.

Owner:NOVATEK MICROELECTRONICS CORP

Bonding welding disk lowering parasitic capacitance and preparing method thereof

ActiveCN101656239BReduce the value of parasitic capacitanceEffective capacitance is smallSemiconductor/solid-state device detailsSolid-state devicesSurface layerParasitic capacitance

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Bonding welding disk lowering parasitic capacitance and preparing method thereof

ActiveCN101656239AReduce the value of parasitic capacitanceEffective capacitance is smallSemiconductor/solid-state device detailsSolid-state devicesSurface layerParasitic capacitance

The invention discloses a bonding welding disk lowering parasitic capacitance and a preparing method thereof, belonging to the technical field of manufacturing semiconductors. The bonding welding diskprovided by the invention comprises a welding disk metal layer, a fist semiconductor doping well region, a second semiconductor doping zone and a first semiconductor high-doping zone, wherein, the fist semiconductor doping well region is formed by doping the semiconductor, the second semiconductor doping zone is formed in the fist semiconductor doping well region, and the first semiconductor high-doping zone is formed on the upper surface layer of the second semiconductor doping zone; junction capacitance formed between the first semiconductor doping well region and the second semiconductor doping zone, the junction capacitance formed between the second semiconductor doping zone and the first semiconductor high-doping zone and the junction capacitance formed between the first semiconductor doping well region and the semiconductor substrate are connected in series to lower the equivalent parasitic capacitance value of the bonding welding disk; meanwhile, the second semiconductor dopingzone has simple preparing method and increases little cost of the preparing technology of the bonding welding disk.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Semiconductor structure and manufacture method thereof

InactiveCN1979841AReduce the likelihood of breakageReduce or eliminate negative impactsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureOptoelectronics

A semiconductor structure and a fabricating method of the same are provided. The semiconductor structure includes a substate; a first low dielectric constant dielectric layer covering the substate and having a first area and a second area; a plurality of conductive member in the low dielectric constant dielectric layer; an upper lid layer positioned on at least a part of the conductive member; and a dielectric upper lid layer covering the second area of the first low dielectric constant dielectric layer and not covering the first area, wherein the conductive member positioned in the second area has a wider space than the conductive member positioned in the first area. The dielectric upper lid layer preferably has an invariable compressing stress.

Owner:TAIWAN SEMICON MFG CO LTD

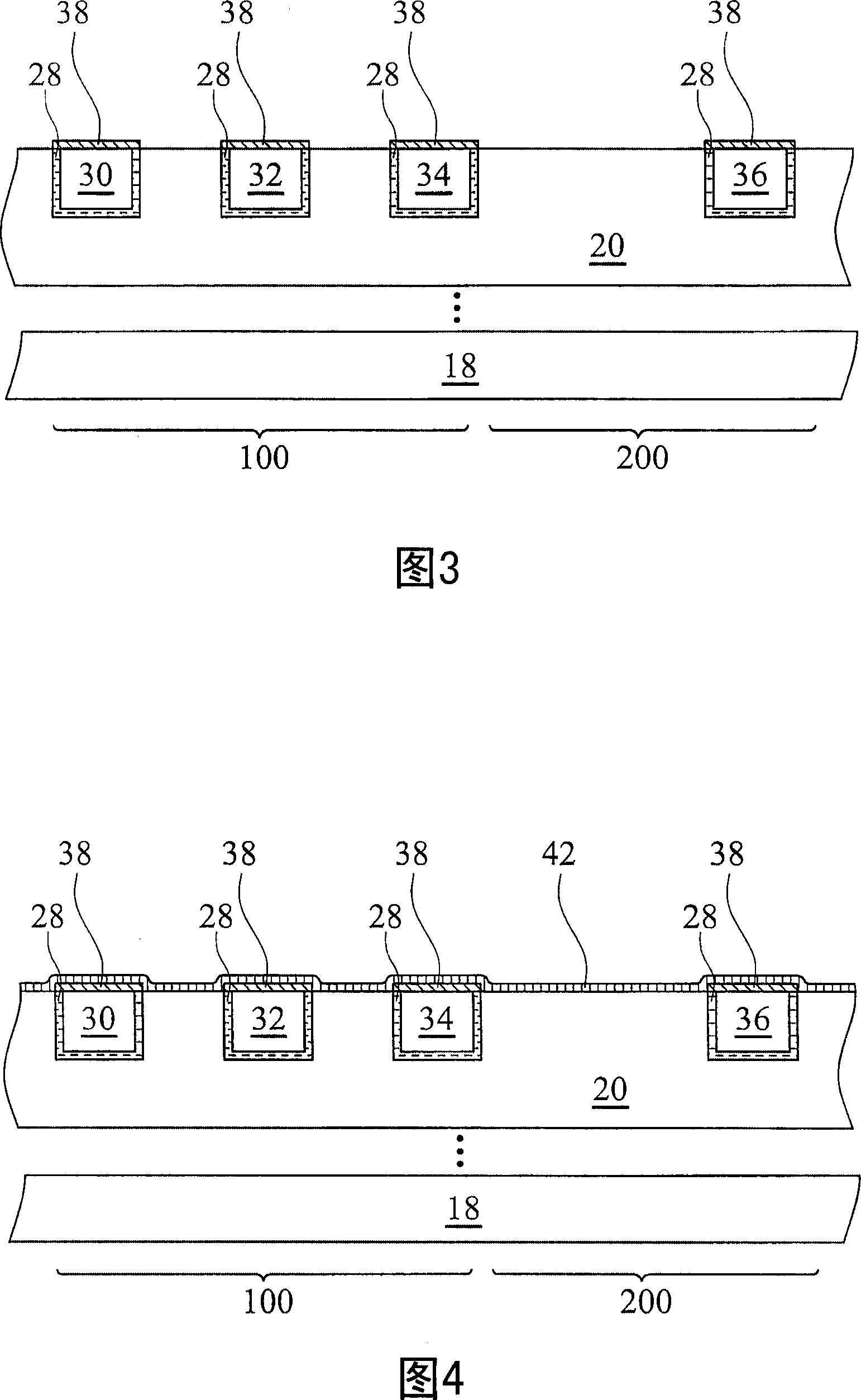

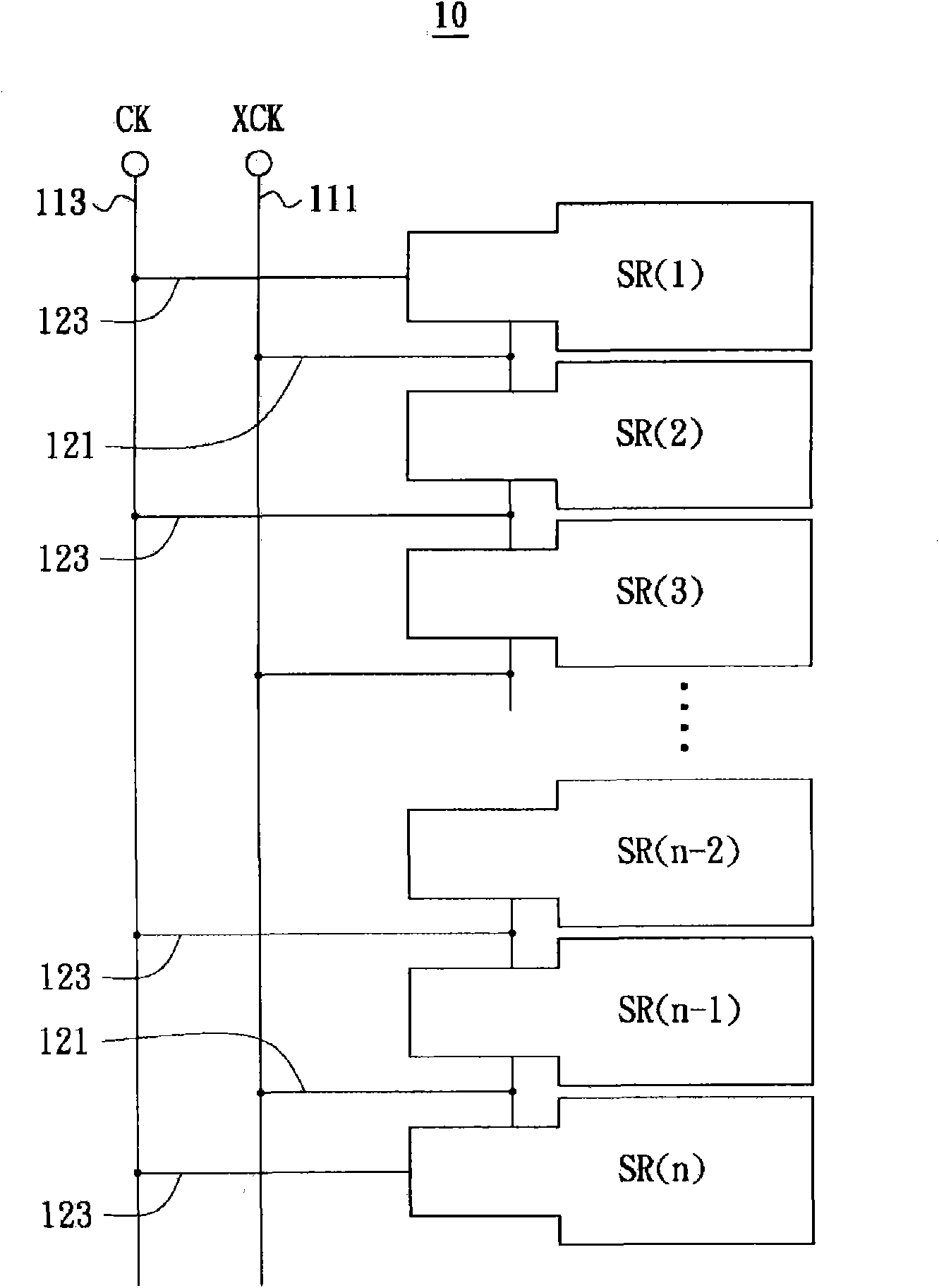

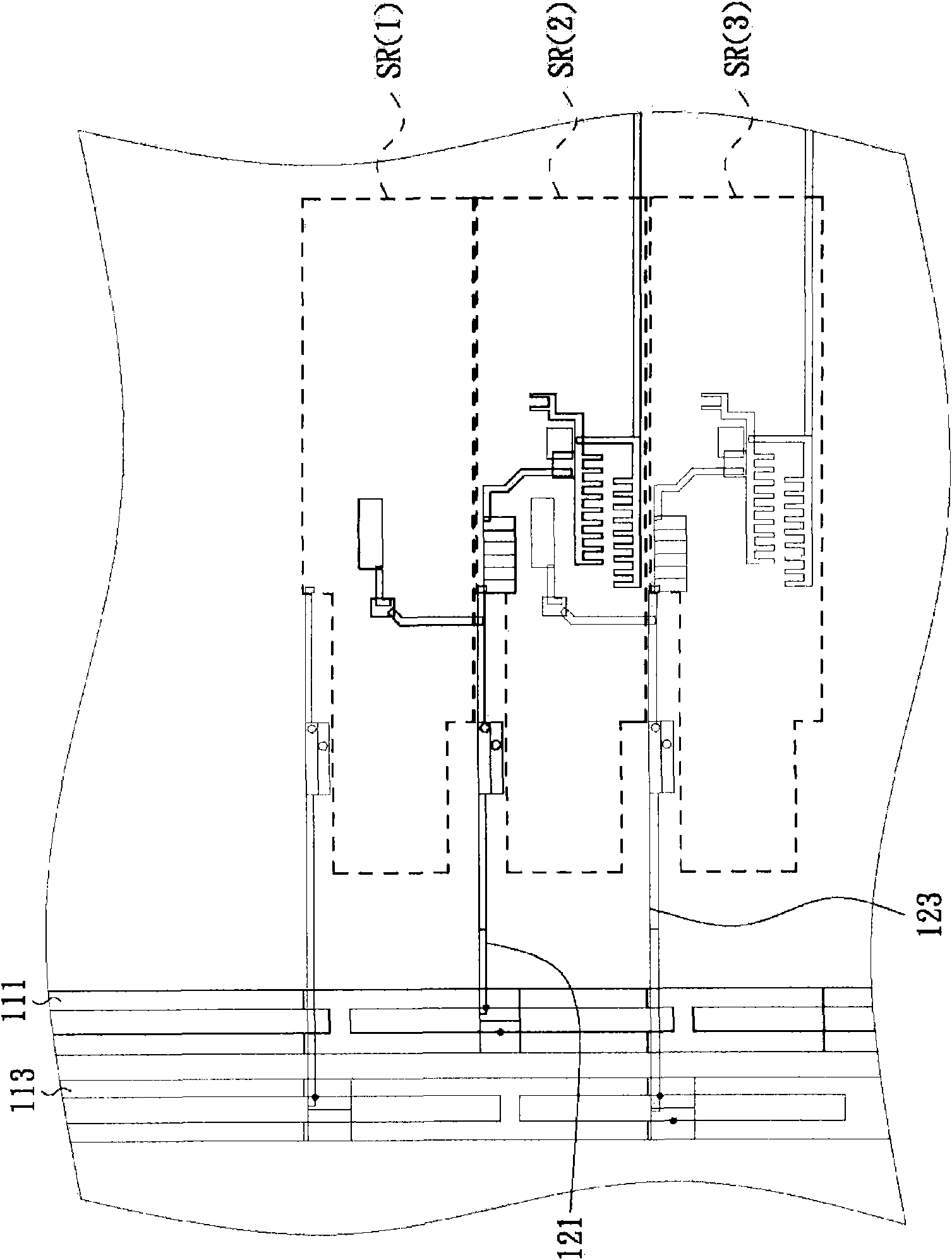

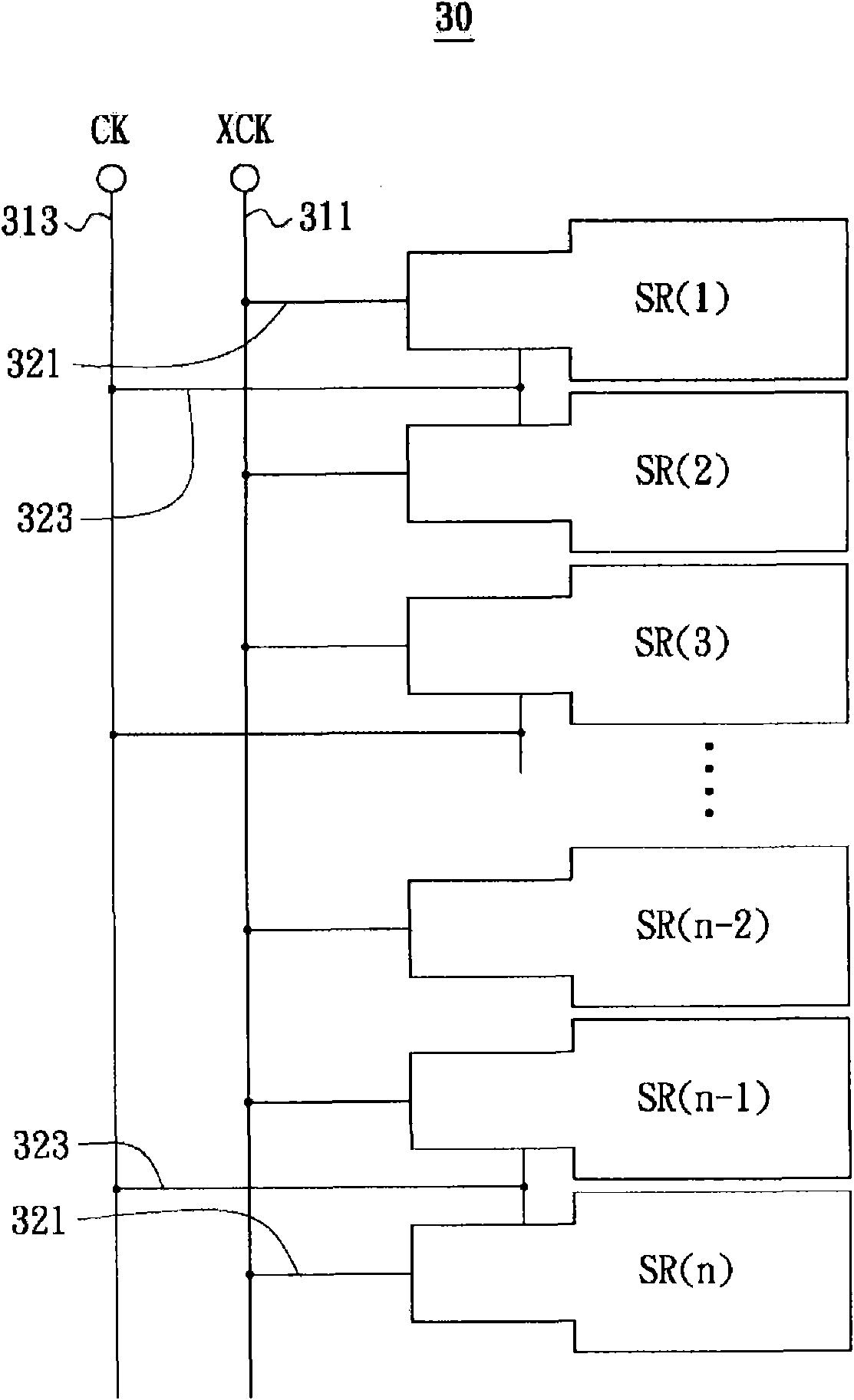

Layout structure for shift buffer circuit

InactiveCN102184703AReduce the value of parasitic capacitanceSave wiring spaceStatic indicating devicesSolid-state devicesEngineeringSignal lines

The invention relates to a layout structure for shift buffer circuits, which comprises a first shift buffer and a second shift buffer arranged adjacent to the first shift buffer. A first signal and a second signal are received by the first shift buffer and the second shift buffer. The second signal and the first signal are reversed phases to each other. In addition, the first shift buffer and the second shift buffer share the signal line so as to receive the first signal. The shared signal line extends between the first shift buffer and the second shift buffer.

Owner:AU OPTRONICS CORP

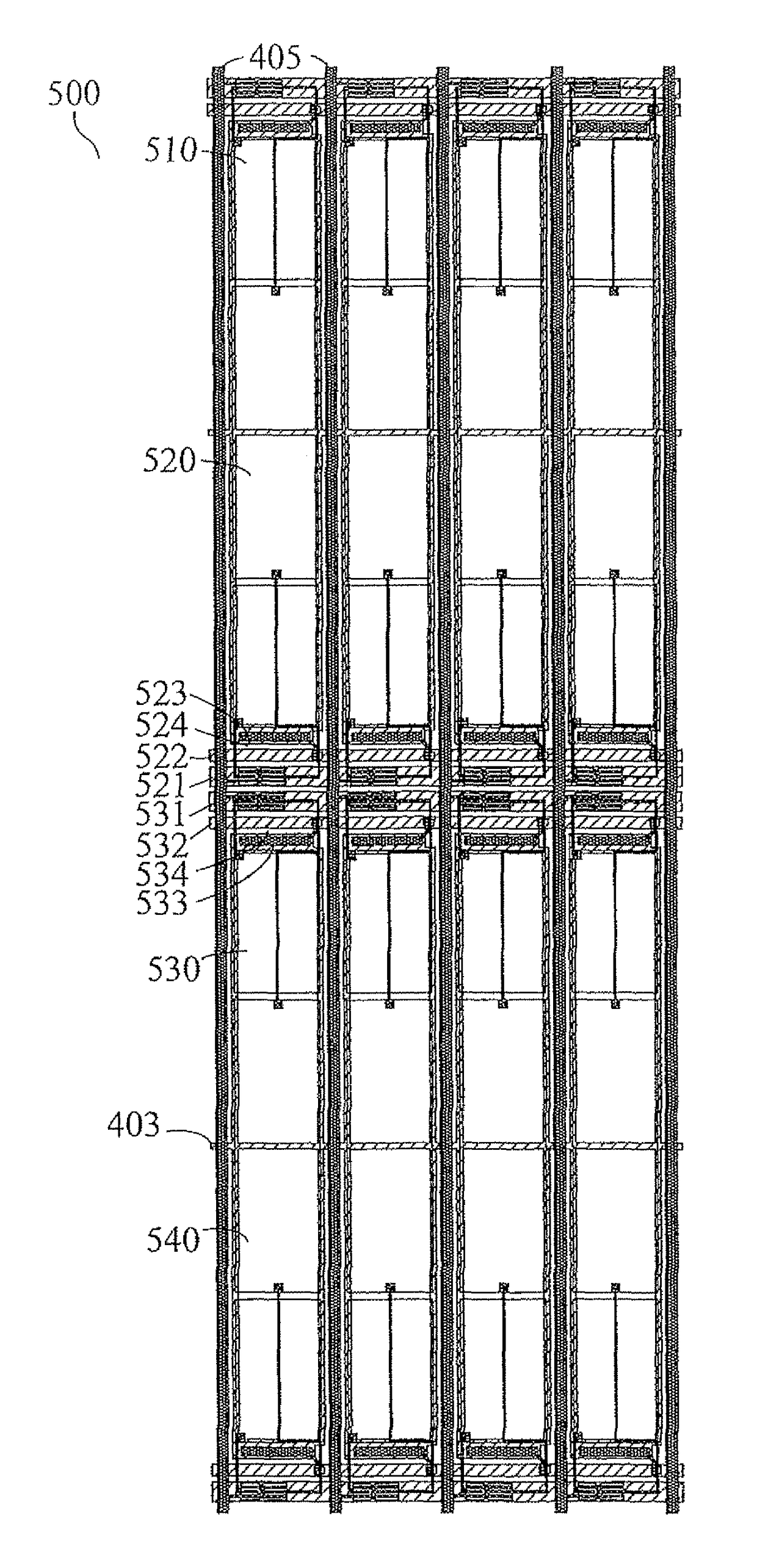

Liquid crystal display for eliminating movable mura

ActiveUS9740069B2Eliminate movable muraReduce RC delayNon-linear opticsCapacitanceLiquid-crystal display

An array substrate is disclosed. A gate line group, common electrode line and two adjacent data lines together defining a pixel unit which has: a thin film transistor; a first and second pixel electrode disposed between the gate line group and the common electrode line; a sharing capacitor disposed between the gate line group and the pixel electrodes. The pixel units are arranged in a plurality of rows along the extending direction of data line, two adjacent pixel units are arranged sequentially in opposite direction. By using each of the sharing capacitors of the adjacent pixel units, the light leakage regions will be away from the openings of the pixel electrodes, therefore the movable mura can be eliminated without increasing the width of the black matrix and the aperture ratio loss can be solved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

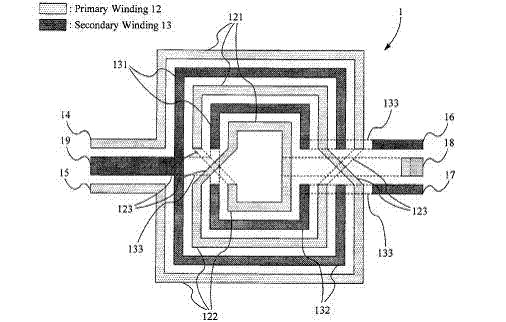

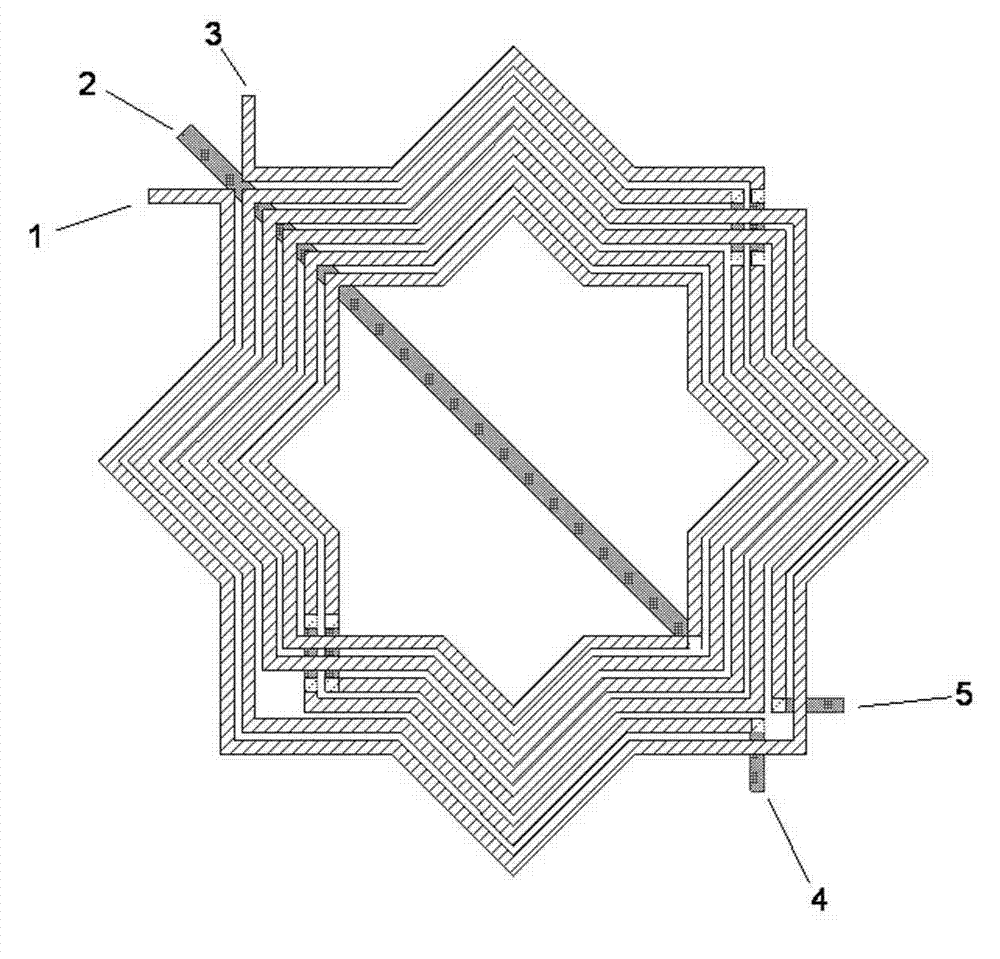

Non-fully-convex dioctahedral transformer Balun

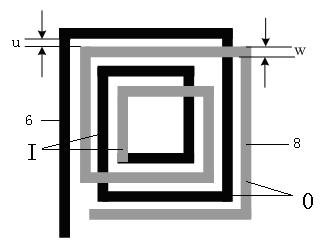

ActiveCN102184910BIncrease the number of sidesIncreased number of sidesSemiconductor/solid-state device detailsSolid-state devicesCMOSTransformer

The invention discloses a non-fully-convex dioctahedral transformer Balun which comprises an encircled pattern formed by encircling a primary winding and a secondary winding at a certain interval, wherein the encircled pattern has a dioctahedral structure; and sixteen angles include eight convex outer angles and eight concave inner angles which are arranged close to one another. The transformer Balun has a novel structure, small chip area, high resonant frequency and high primary and secondary inductance. High resonant frequency and high primary and secondary inductance can be provided on a system on a chip, the transformer Balun can be manufactured under the processing conditions of a BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor Transistor) and a CMOS (Complementary Metal-Oxide-Semiconductor Transistor), high quality factor, high resonant frequency and high primary and secondary inductance are realized, and only small ship area is consumed.

Owner:GUANGZHOU RUNXIN INFORMATION TECH

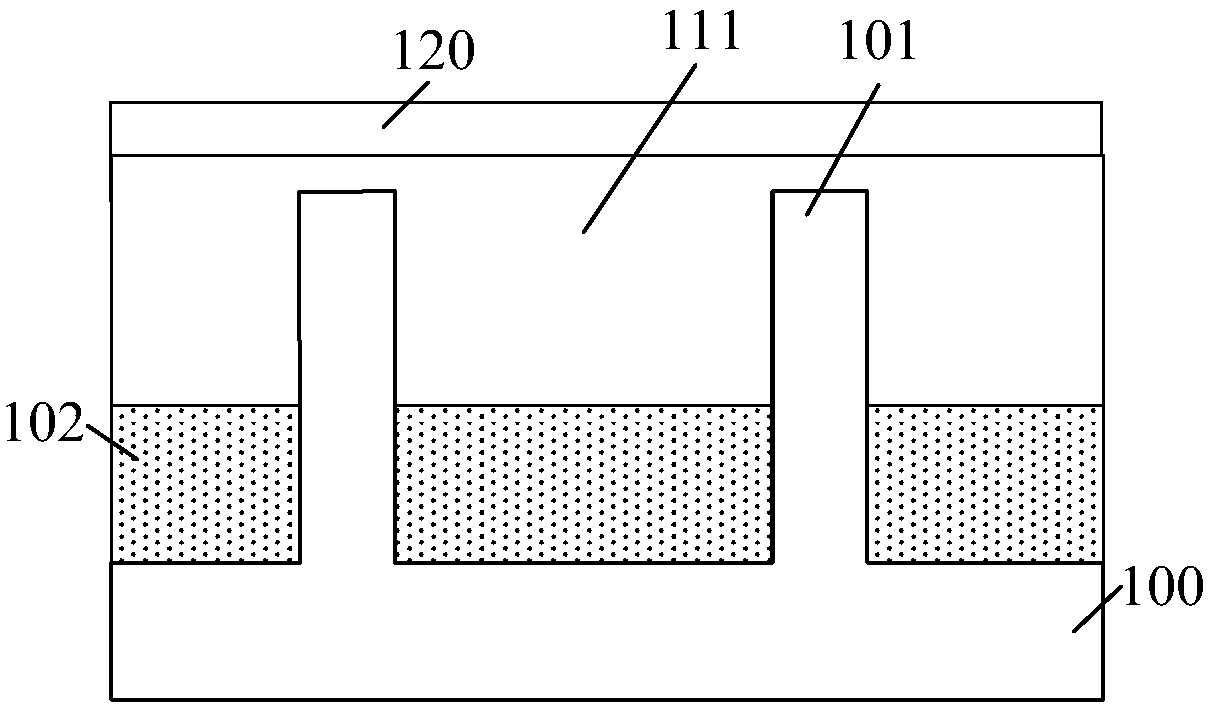

Semiconductor structure and manufacturing method for same

InactiveUS20190378910A1Reduce parasitic capacitanceReduce the value of parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The present disclosure provides a semiconductor structure and a manufacturing method for the semiconductor structure. The semiconductor structure manufactured according to the manufacturing method provided in the present disclosure comprises a substrate and a gate formed on the substrate, and a silicon epitaxial layer is formed on the substrate at two sides of the gate; and a side surface of the gate is provided with a first side wall, with a gap being provided between the first side wall and the silicon epitaxial layer, and a surface of the first side wall further comprises a second side wall, with the second side wall covering the gap, so that there is an air gap between the first side wall and the silicon epitaxial layer.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

A liquid crystal display for eliminating movable mura

ActiveUS20160054630A1Eliminate movable muraReduce RC delayTransistorNon-linear opticsCapacitanceLiquid-crystal display

An array substrate is disclosed. A gate line group, common electrode line and two adjacent data lines together defining a pixel unit which has: a thin film transistor; a first and second pixel electrode disposed between the gate line group and the common electrode line; a sharing capacitor disposed between the gate line group and the pixel electrodes. The pixel units are arranged in a plurality of rows along the extending direction of data line, two adjacent pixel units are arranged sequentially in opposite direction. By using each of the sharing capacitors of the adjacent pixel units, the light leakage regions will be away from the openings of the pixel electrodes, therefore the movable mura can be eliminated without increasing the width of the black matrix and the aperture ratio loss can be solved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

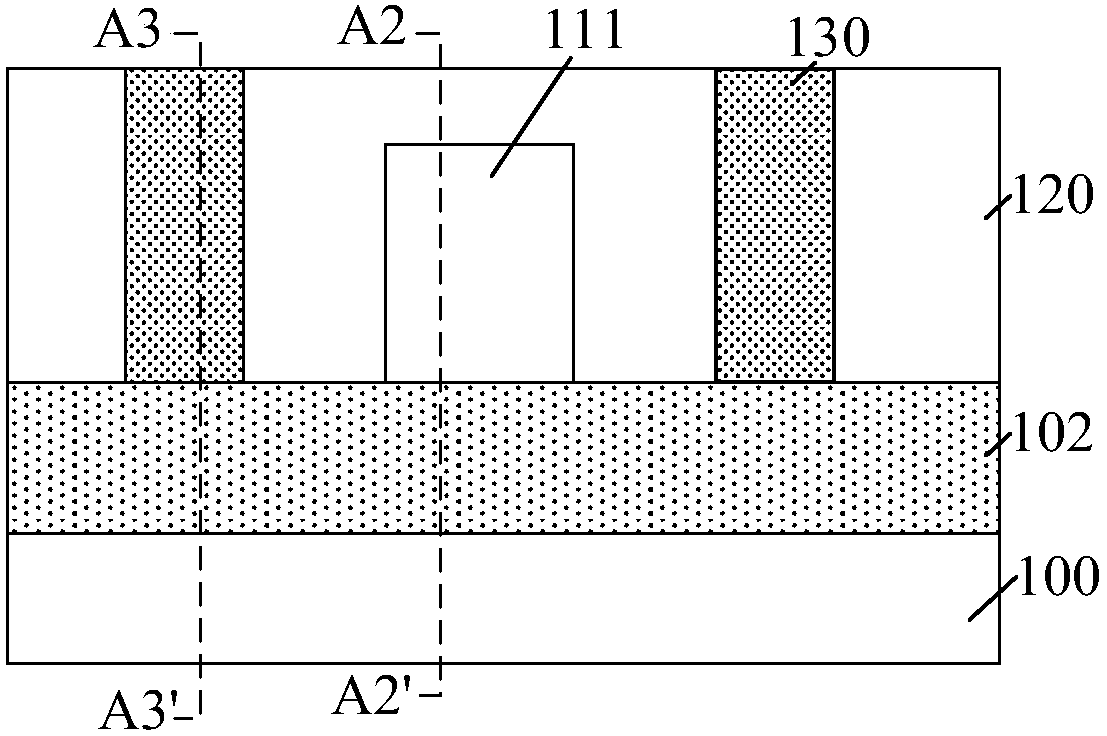

Semiconductor structure and forming method thereof

ActiveCN109727976AImprove structural performanceIncrease contact areaTransistorSemiconductor/solid-state device manufacturingSemiconductor structureParasitic capacitance

A semiconductor structure and a forming method thereof are provided. The forming method involves a first dielectric layer, a metallide and a second dielectric layer. The first dielectric layer is located on a substrate, covers the side walls of a gate, and has first grooves. The first grooves extend from the first dielectric layer of device regions to the first dielectric layer of isolation regions, and the top and side wall surfaces of source-drain doping layers are exposed at the bottoms of the first grooves. The metallide is located on the surfaces of the source-drain doping layers exposedat the bottoms of the first grooves. The second dielectric layer is located in the grooves of the isolation regions, and exposes the metallide on the top surfaces of the source-drain doping layers. The second dielectric layer can reduce the projection pattern area of the electrical connection structure of the isolation regions on the side wall surface of the gate, so as to reduce the value of parasitic capacitance formed by the electrical connection structure, the gate and the first dielectric layer between the electrical connection structure and the gate and improve the performance of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com