Transistor and forming method thereof

A transistor and semiconductor technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of high dielectric constant, affect the performance of transistors, reduce the effect of stress in the channel region, etc., and achieve the effect of increasing the size of the stress.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

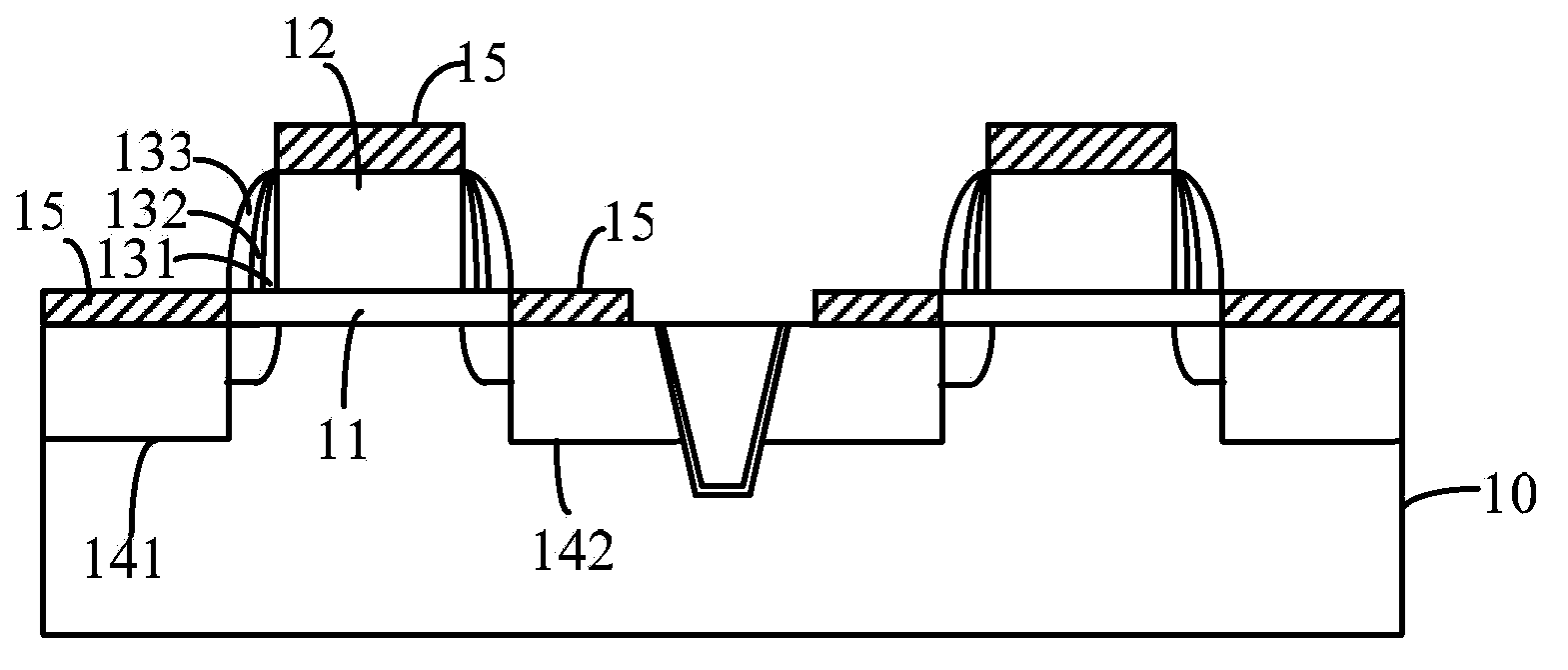

[0040] As mentioned in the background, the method for forming a transistor in the prior art needs to form three layers of sidewalls on both sides of the gate structure of the transistor, the steps are complicated, and the process cost is high. Moreover, the dielectric constant of the silicon nitride sidewall is relatively high, so that the parasitic capacitance around the gate structure of the formed transistor is relatively high, which affects the performance of the transistor.

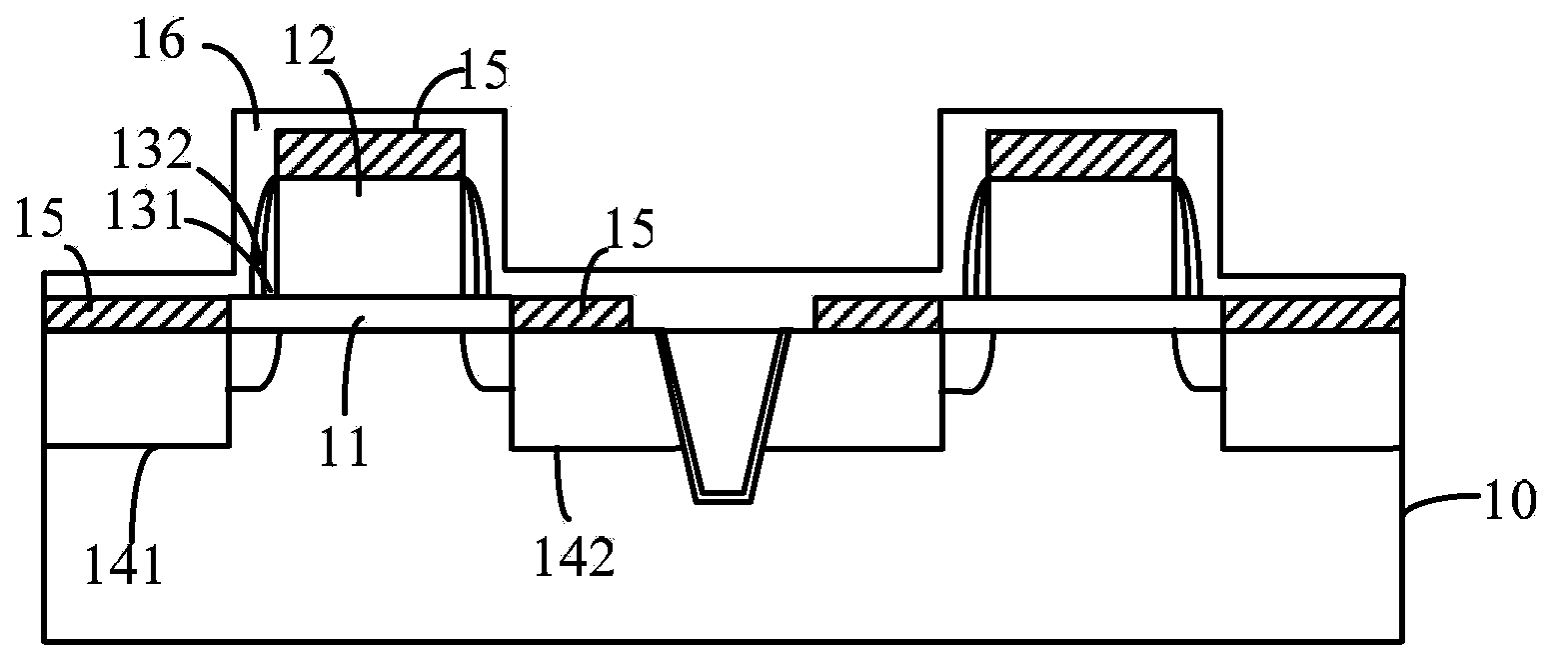

[0041] In the method for forming a transistor proposed by the present invention, a first side wall and a second side wall are formed on both sides of the gate structure, the first side wall is a doped silicon nitride layer, and then a source electrode, a drain electrode, and a source electrode are formed. The metal silicide layer on the surface of the electrode and the drain, and then remove the second side wall to form a stress layer. Removing the second sidewall can reduce the distance between the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More