Semiconductor structure and forming method therefor

A semiconductor and forming layer technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems that the electrical properties of semiconductor devices need to be improved, and achieve the effect of optimizing electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

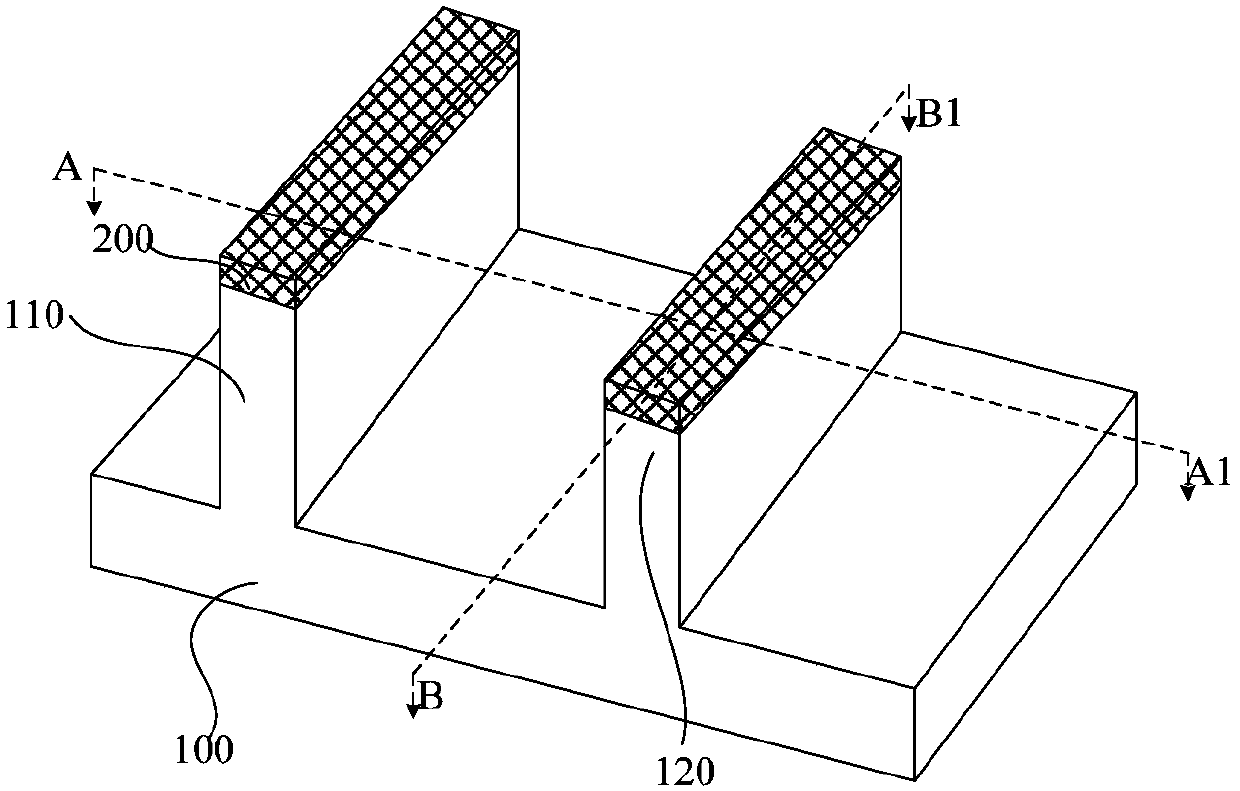

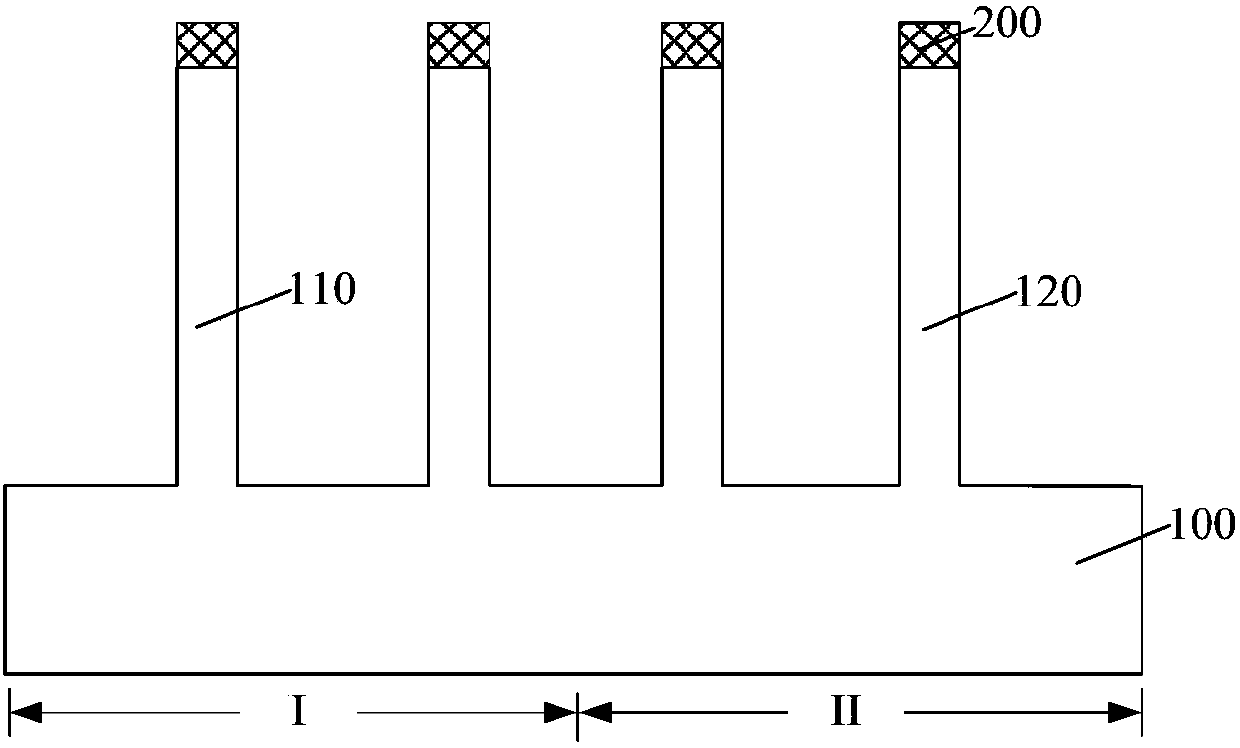

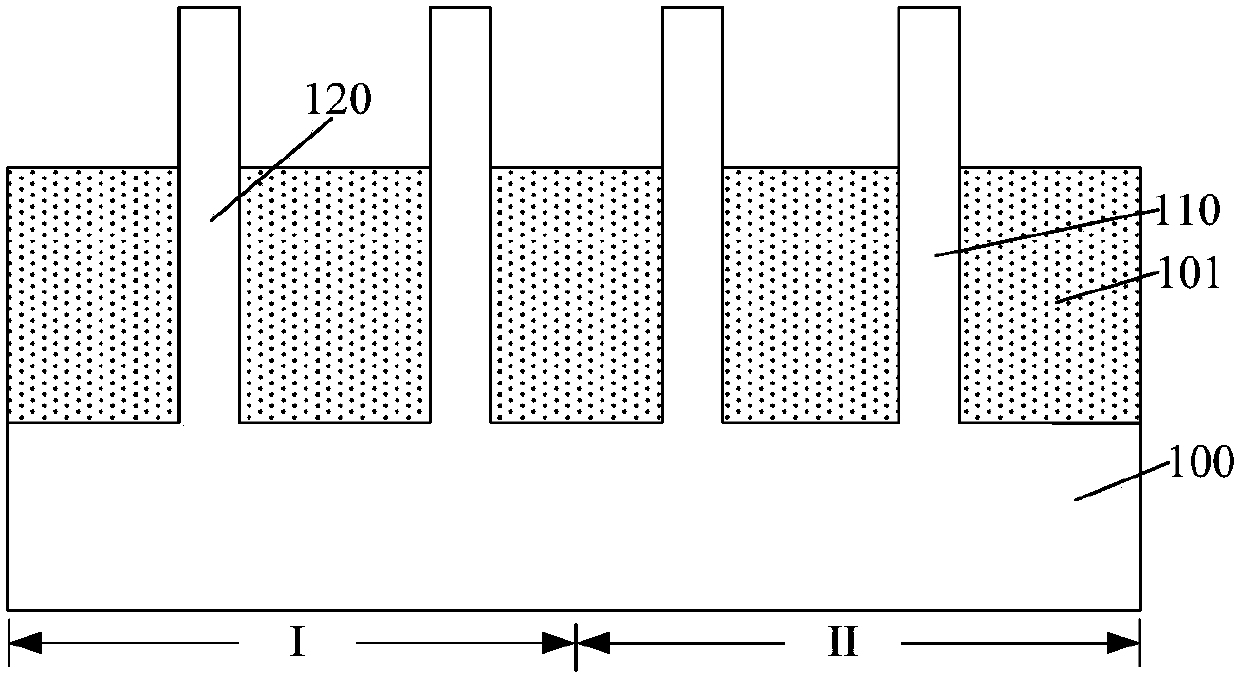

[0014] It can be seen from the background art that the electrical performance of semiconductor devices formed in the prior art needs to be improved. The reason is analyzed in conjunction with a method of forming a semiconductor structure, the method of forming includes:

[0015] A base is provided, the base includes a substrate and a fin protruding from the substrate, the substrate includes an N-type region and a P-type region; forming a part of the side across the fin and covering the fin A dummy gate structure on the wall surface and a top surface; a source-drain doped region is formed in the fins on both sides of the dummy gate structure; a bottom interlayer dielectric layer is formed on the substrate between the fins, and the bottom interlayer The top of the dielectric layer is flush with the top of the dummy gate structure; the dummy gate structure is removed, a first opening is formed in the interlayer dielectric layer at the bottom of the N-type region, and a first open...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More