Contact pad

A technology for contact pads and pads, which is applied to electrical components, electrical solid devices, circuits, etc., can solve the problems of reducing parasitic capacitance, limited height, etc., and achieve good isolation effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the above objects, features and advantages of the present invention more comprehensible, the embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods.

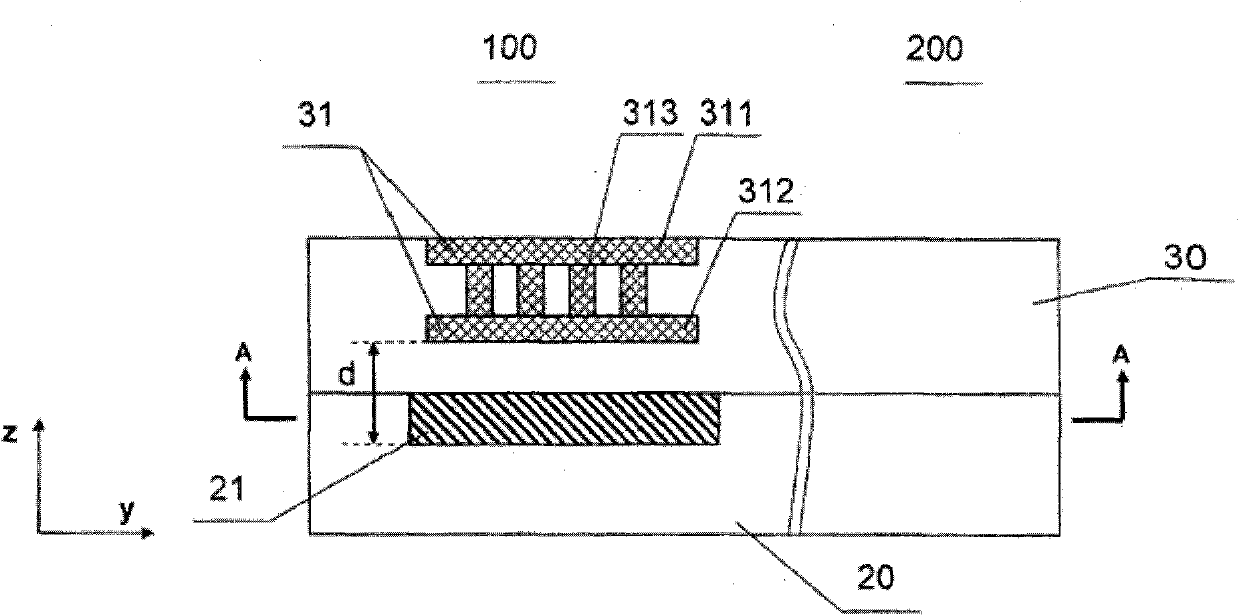

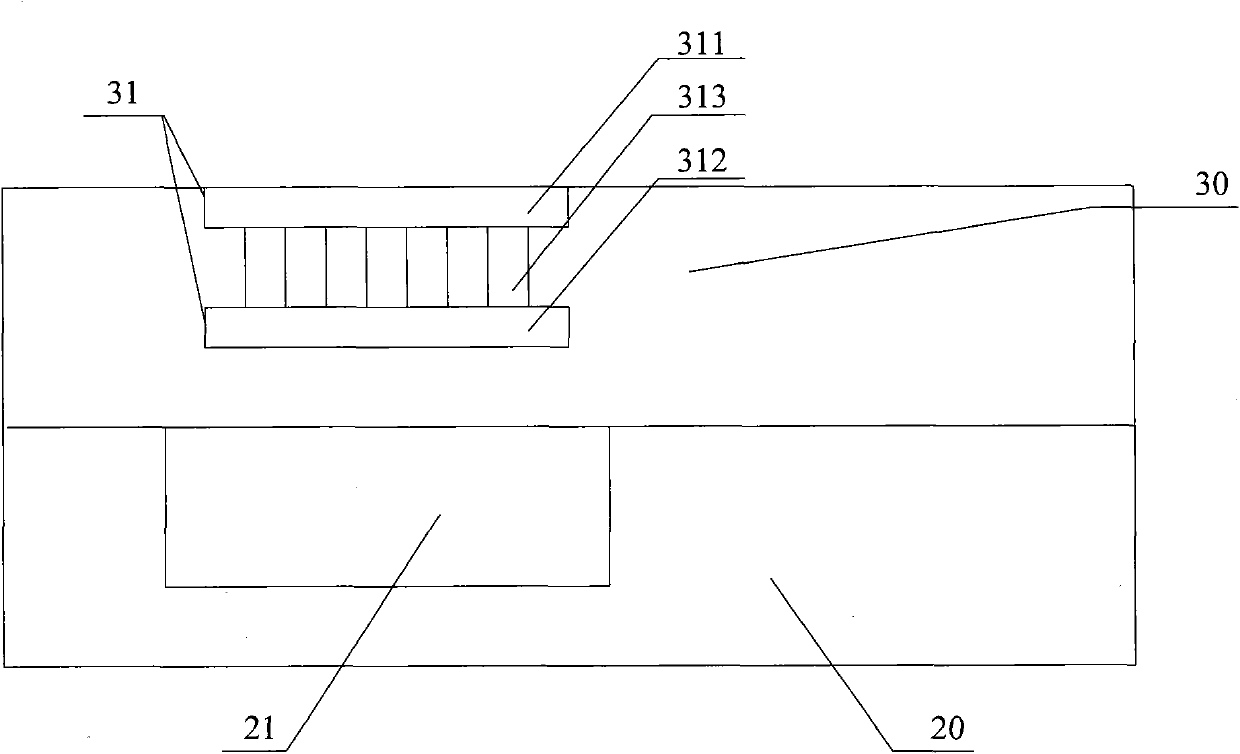

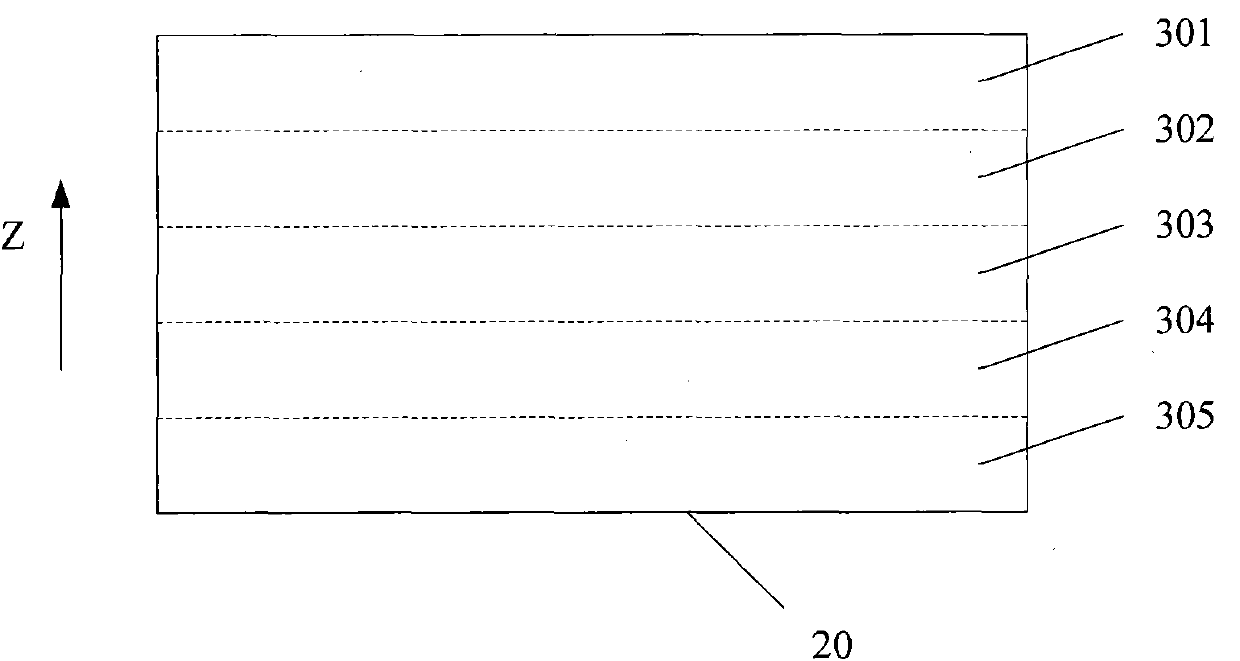

[0023] figure 2 Shown is a schematic diagram of a contact pad structure provided by the present invention in order to reduce the parasitic capacitance in the CMOS device. Such as figure 2 As shown, the contact pad is formed in the substrate 20 and the interconnect structure layer 30, wherein the Z direction is a direction perpendicular to the upper surface of the semiconductor substrate. The interconnect structure layer 30 includes a multi-layer metal layer, and the contact pad includes a pad metal layer 31. In this embodiment, the pad metal layer 31 includes a first layer of pad metal layer 311, a second layer of pad metal layer 312 and A hole 313 for connecting the first layer of pad metal layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More