Estimation method for integrate circuit function yield

A technology of integrated circuit and yield rate, which is applied in the field of integrated circuit function yield estimation, and can solve problems such as yield estimation error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

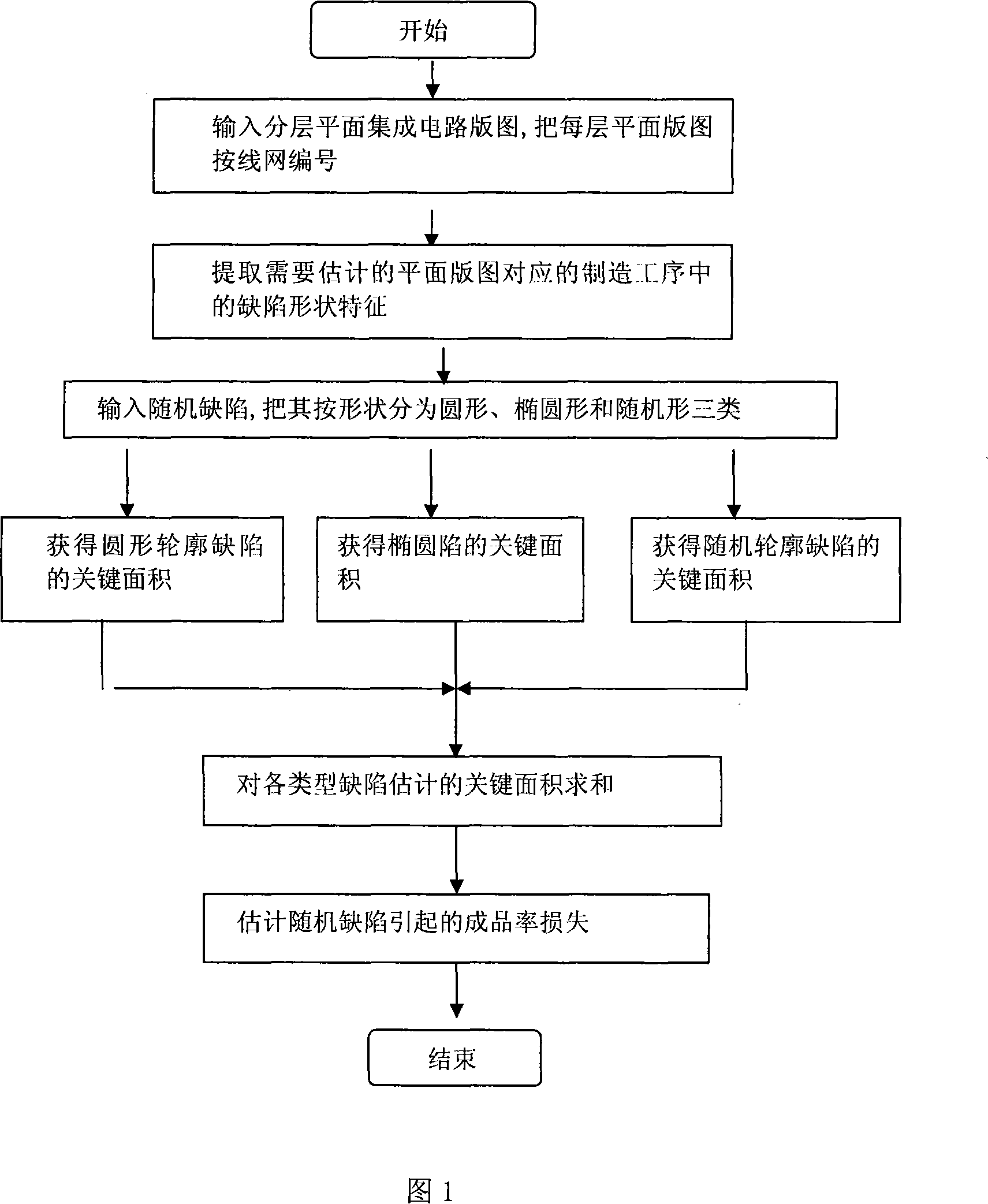

[0059] The yield estimation method implemented in the present invention is to analyze the defect parameters on the basis of collected defect characteristic parameters related to process function yield, and then estimate the functional yield of different process layers according to the layout of the input integrated circuit chip. The defect characteristic parameters of the functional yield related to the i-th layer process generally include defect shape, defect density D i , the defect spatial distribution characteristic is the defect clustering coefficient α i , these parameters are collected and stored in the engineering database. In the embodiment of the present invention, according to the type of the analyzed defect data, that is, a set of formulas can accurately estimate the functional yield of the integrated circuit, and the specific process is shown in FIG. 1 .

[0060] With reference to Fig. 1, the process of the integrated circuit function yield estimation method of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More