Special-purpose double production line RISC instruction system and its operation method

A technology of instruction system and operation method, applied in the direction of concurrent instruction execution, machine execution device, etc., can solve the problems of increased hardware area, poor compatibility, operation speed and efficiency limitation, etc., to save resource waste, low cost and low power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

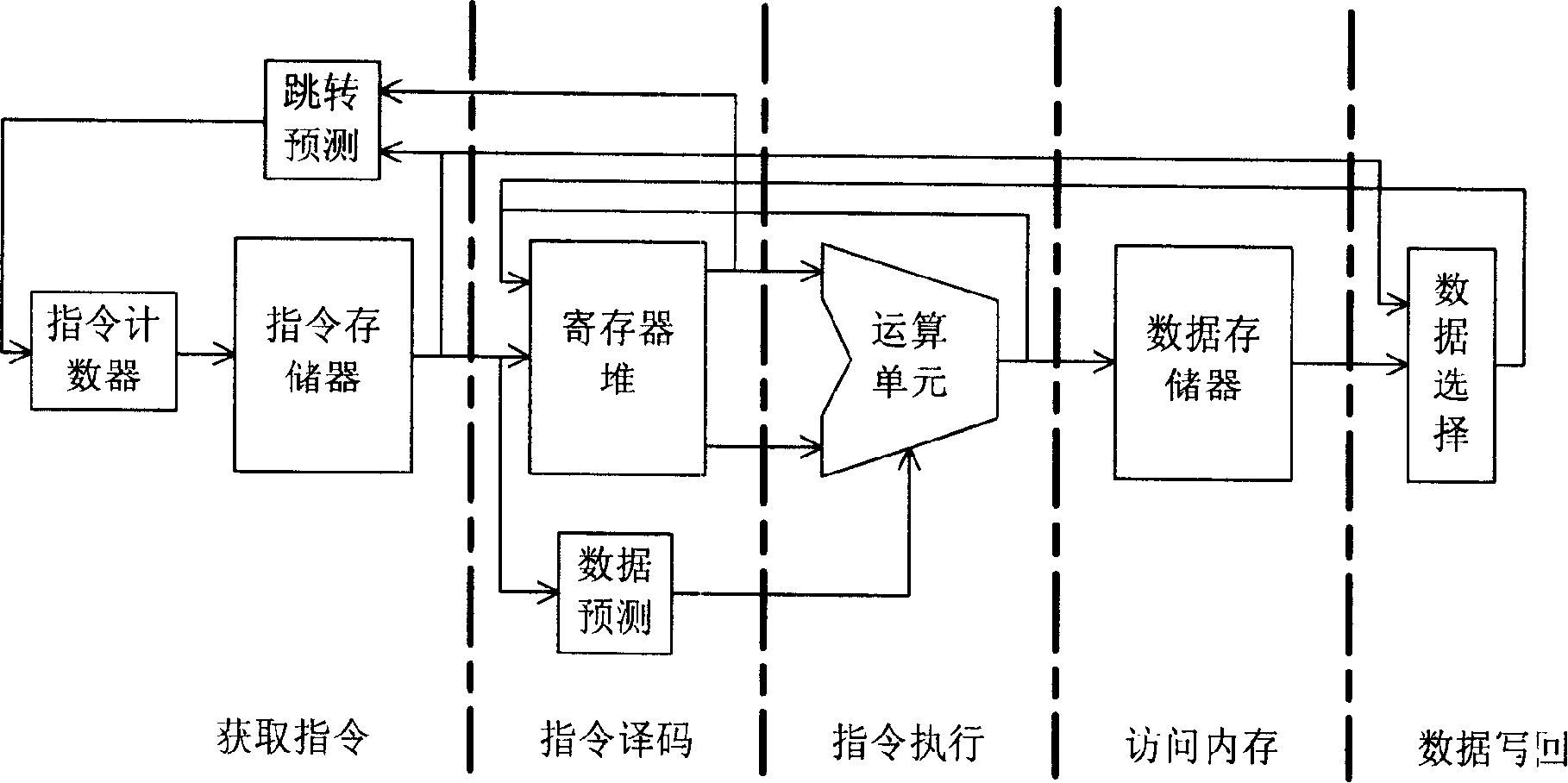

[0022] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0023] This embodiment is a special-purpose dual-pipeline RISC instruction structure used in an electric energy metering chip with a special-purpose double-pipeline RISC structure, so as to realize the design requirements of electric energy metering.

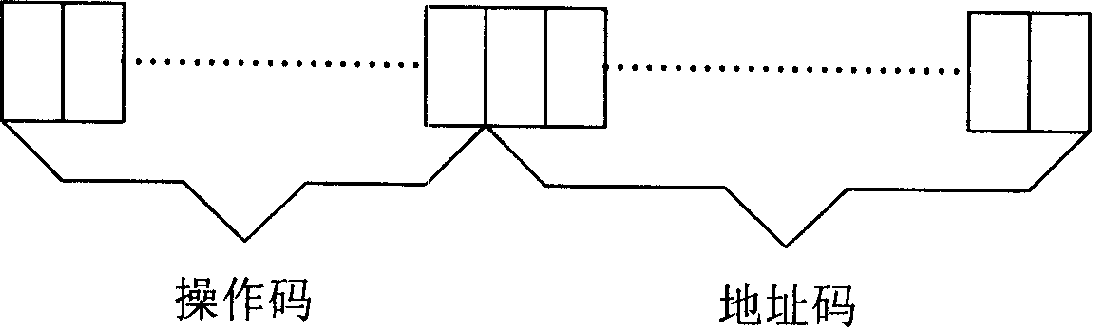

[0024] figure 1 It is a schematic diagram of the single-pipeline RISC instruction structure.

[0025] As shown, a single-pipeline instruction consists of an opcode and an address code. The operation code is the type of operation instruction, and the address code is the storage address of the data involved in the instruction.

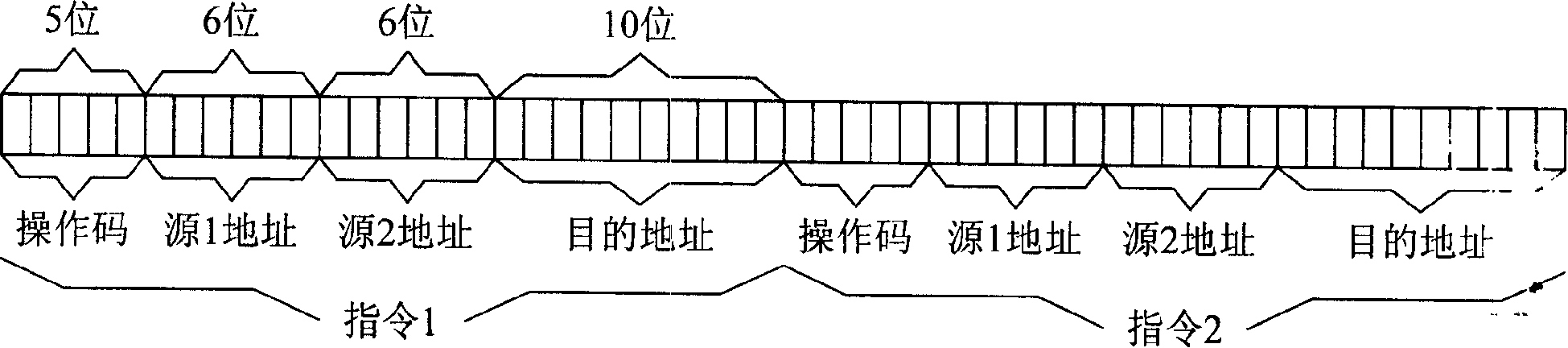

[0026] figure 2 It is a schematic diagram of the special-purpose dual-pipeline RISC instruction structure of the present invention.

[0027] As shown in the figure, the instruction length of the dedicated dual-pipeline RISC instruction is 54 bits, including two singl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More