Stack type chip packaging structure and manufacturing method thereof

A technology of chip packaging structure and packaging structure, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc. cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

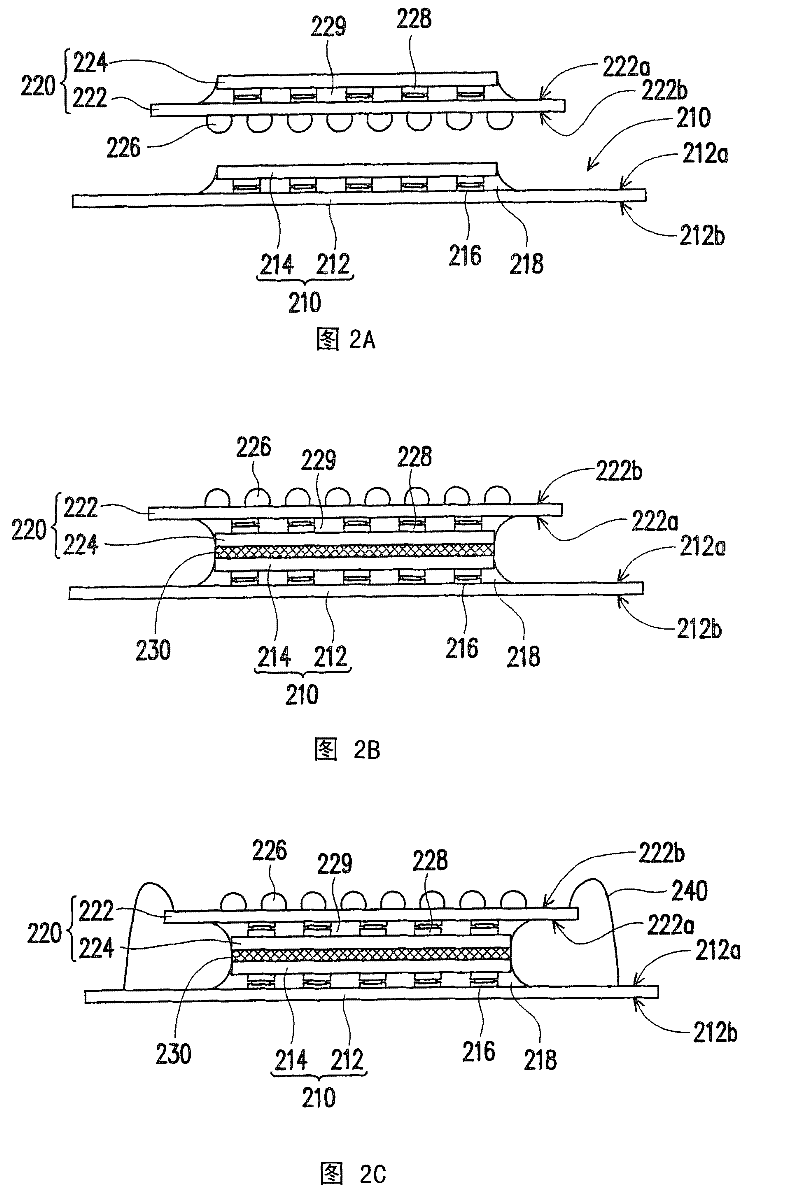

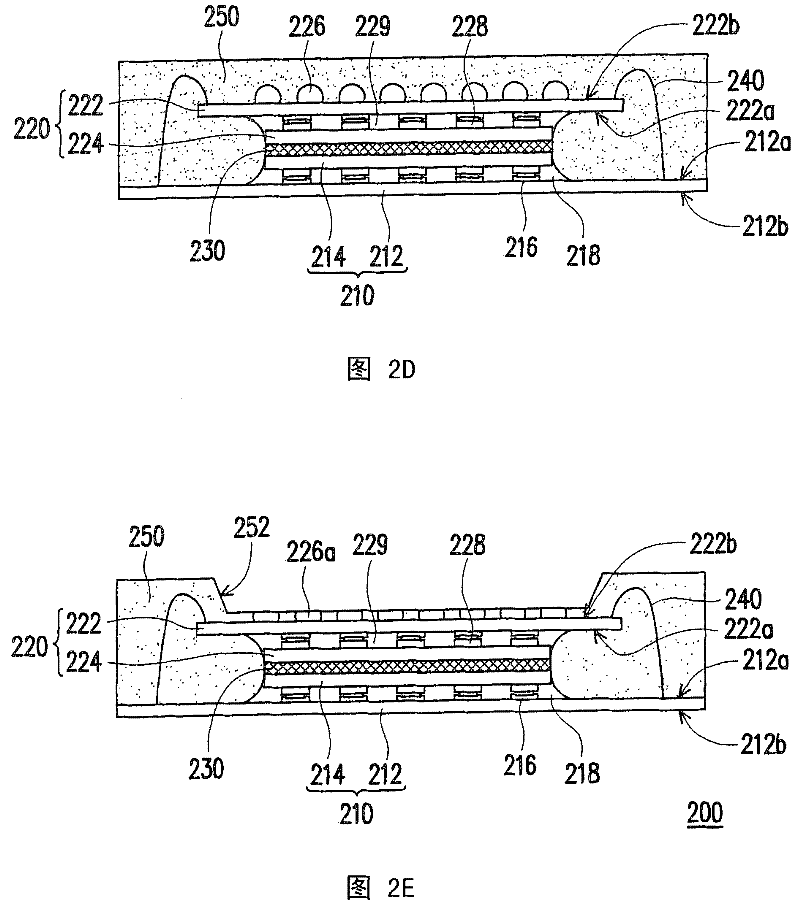

[0079] Figure 2A~2H Shown as a cross-sectional schematic diagram of a manufacturing process of a stacked chip package structure according to an embodiment of the present invention. First, please refer to Figure 2A As shown, a first package structure 210 and a second package structure 220 are provided. The first packaging structure 210 includes a first substrate 212 and a first chip 214. The first substrate 212 has a first surface 212a and a second surface 212b corresponding thereto. The first chip 214 is disposed on the first surface 212 a of the first substrate 212 and is electrically connected to the first substrate 212. In this embodiment, the first chip 214 is electrically connected to the first substrate 212 through a plurality of first bumps 216. However, the first chip 214 can also be electrically connected to the first substrate 212 in other ways, and the present invention does not impose any limitation on this. In addition, in order to protect the first bump 216 f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More