Router power consumption model based on network on chip

A network-on-a-chip, router technology, applied in the field of router power consumption model, can solve the problems of small computational complexity and implementation cost, increasing NoC cost, reducing network performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

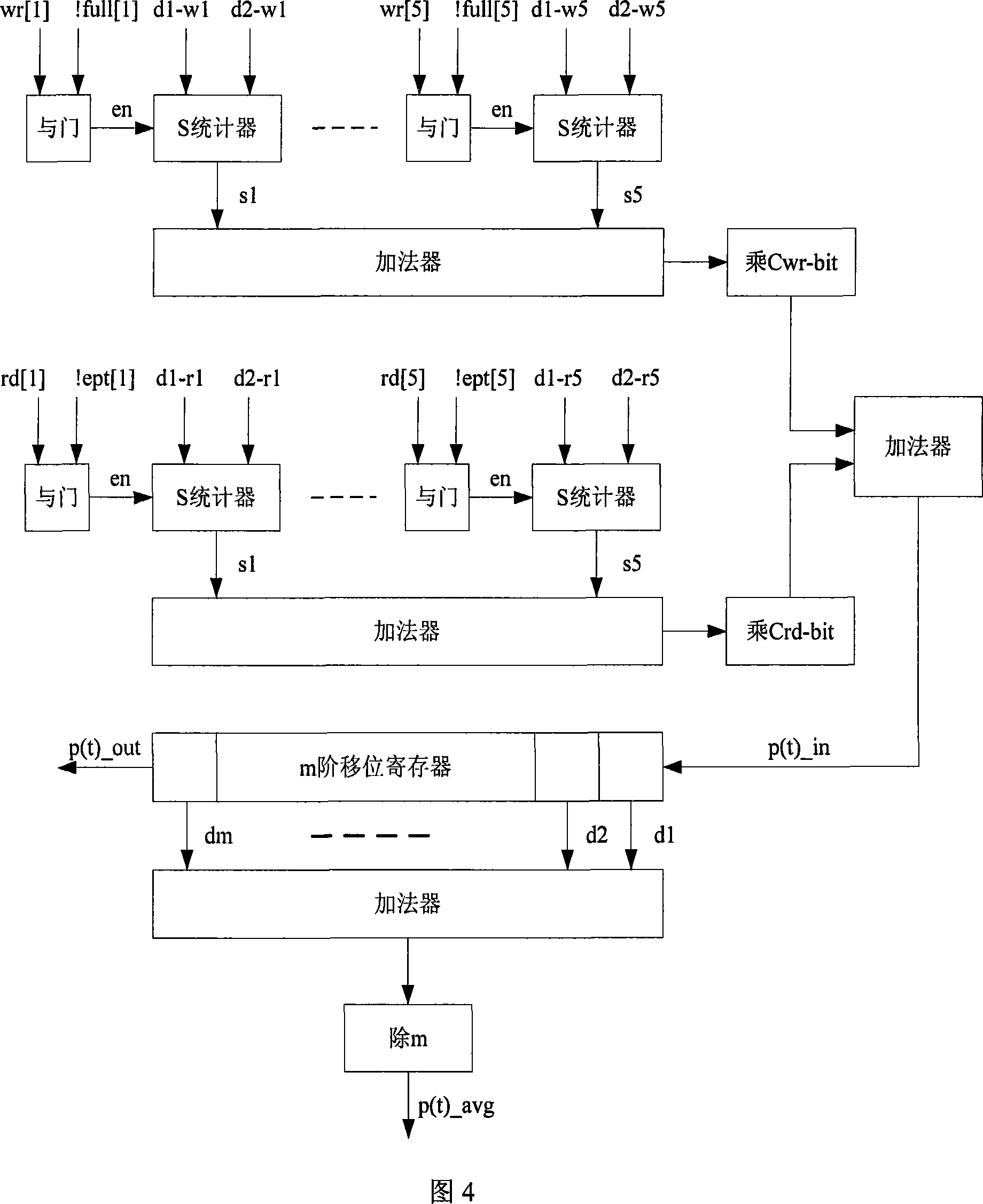

[0058] A router power consumption model based on a network-on-chip, which simplifies the router operation into four power consumption links of write cache, read cache, span switch and span link according to the proportion of power consumption, and attributes the dynamic power consumption to the current The bit inversion activity triggered when the data piece arrives, the power consumption is counted through the bit inversion activity, and the obtained router

[0059] The power consumption model is as follows:

[0060] P total = ( C wr - bit × Σ i = 1 N fli t - wr ...

Embodiment 2

[0064] Using the statistical average value of the bit inversion number to replace the instantaneous sampling value, the simplified formula of the router power consumption model is as follows:

[0065] P total =(C wr-flit ×N flit_wr +C rd-flit ×N flit_rd ) / T

[0066] In the formula, C rd-flit is the average power consumption coefficient of the router to read a single data slice operation, C wr-flit is the average power consumption coefficient of the router writing a single data slice operation.

[0067] The hardware implementation of the simplified power consumption model is shown in Figure 6. It is mainly composed of 10 MUX, 10 AND gates, 4 adders, 1 divider and 1 m-order shift register. The biggest difference from the complete model is that the simplified model only uses one-of-two MUX, AND gate and adder to realize the statistics of read and write operation power consumption, eliminating the need for complex units such as S statistic and multiplier, greatly reducing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More